尽管大规模集成在当代电子设计中无处不在,但经典CMOS图腾柱拓扑中的分立MOSFET有时仍然是不可或缺的。因此,用逻辑电平信号有效驱动它们的技巧和窍门也同样有用,因为这可能"有点"棘手,特别是在涉及到标准逻辑电压电平之外的情况下。

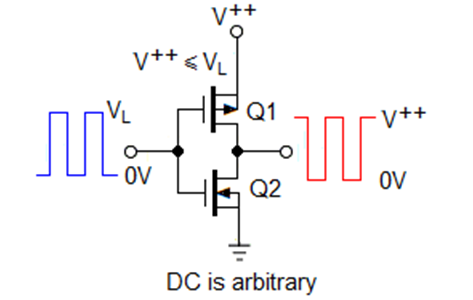

如果(幸运的话)它们不是,我们就得到了图1。

图1 在V++<= VL的情况下,逻辑信号图腾柱驱动-直接连接的最简单情况。

幸运的是,图腾FET的源极引脚连接到与逻辑电平相匹配的正负电轨上,因此简单的直接连接(一根导线)就足够了。这样的话,只需这样做就能成功:

第2项尤为重要,因为它会影响到图腾柱效率的头号敌人——交叉导通。

经常发生的情况是,在Q1导通和Q2不导通到相反状态之间的转变过程中,两个晶体管导通时会有一段重叠的时间。这就是“交叉导通”,它会浪费电能,有时甚至会浪费很多。持续时间越长,浪费就越大。交叉导通的持续时间取决于逻辑信号完成0/1或1/0转换所需的时间,这取决于对各个栅极输入电容充电和放电所需的时间。延迟一个FET关断的电容也会延迟其互补FET的开启,这在一定程度上缓解了交叉导通的困扰,但速度仍然至关重要。

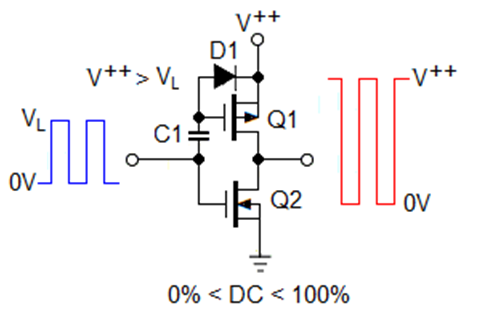

现在假设Q1的V++源电压高于VL。那么该怎么办?图2显示了一个简单的解决方案:交流耦合。

图2 如果控制信号连续运行,交流耦合可以解决正轨电压失配的问题。

当然,只有当逻辑信号始终具有交流分量时,这种简单的解决方法才有效。也就是说,如果其占空比既不是0%(始终关闭)也不是100%(始终打开):0%<DC<100%。C1的电容至少要比Q1的栅极电容大一个数量级(例如,1nF)。虽然D1通常可以是普通结型二极管(例如1N4148),但如果需要额外的数百毫伏的栅极驱动电压,肖特基型二极管可能是更好的选择。

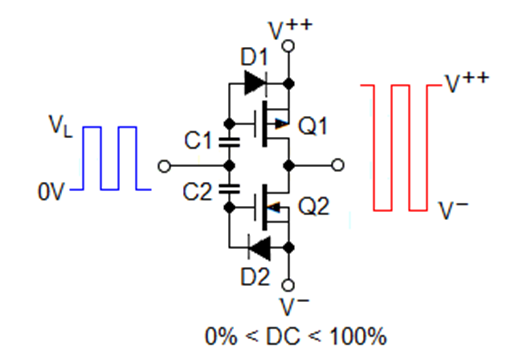

如果图腾柱的负轨低于接地,交流耦合也可以发挥作用,如图3所示。当然,同样的直流限制也适用。

图3 交流耦合和负轨失配也是如此。

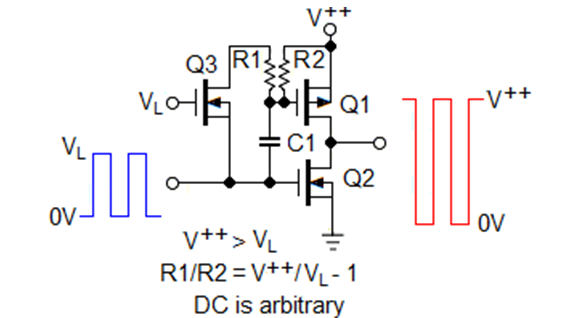

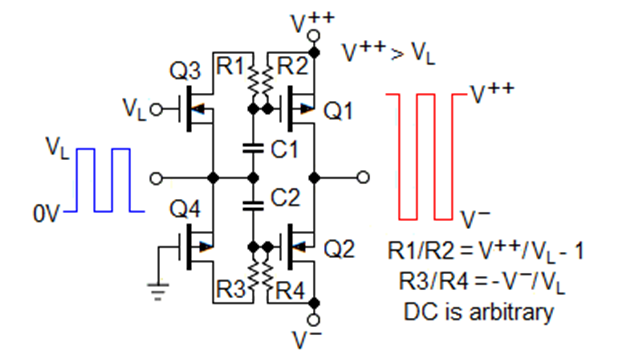

那么,如果DC不遵守规则,我们又不能依靠简单的二极管来定义信号电平,该怎么办呢?参见图4。

图4 当逻辑信号停止时,“接地”栅极Q3保持C1电荷。

小信号晶体管Q3配置为共栅极、非反相高速放大器,可将必要的稳态电流传输至Q1。选择足够小的R2电阻来获得Q2的最大预期源极至栅极漏电流(R2=10k通常是一个非常保守的选择),然后R1=R2(V++/VL–1)。

当然,如图5所示,同样的技巧也适用于负图腾柱轨。

图5 接地栅极Q4通过C2和Q2将逻辑信号转移到负电源轨。

(原文刊登于EDN美国版,参考链接:Driving CMOS totem poles with logic signals, AC coupling, and grounded gates,由Ricardo Xie编译)

最前沿的电子设计资讯

最前沿的电子设计资讯