在电子设备中, 电源的稳定性很重要,电源对纹波噪声的抑制能力也同样重要。用来描述对电源纹波噪声的抑制能力,通常用电源抑制比(Power Supply Rejection Ratio)来表征,它是衡量电源供应的稳定性和对干扰的抑制能力的重要参数。是经常在电子放大器(特别是运算放大器 )或稳压器等规格书出现的参数。

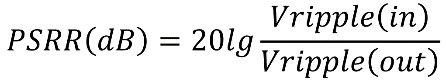

电源抑制比(Power Supply Rejection Ratio)简称PSRR,它以电源输入纹波和输出纹波的对数比来计算,单位为分贝(dB),其计算公式为:

其中Vripple(in)是输入端的纹波,Vripple(out)是输出端的纹波。绝大多数情况使用Vripple(in)/Vripple(out)来计算,此时PSRR为正值;如果使用Vripple(out)/Vripple(in)来计算,此时PSRR为负值。

从上面的公式可以看出:

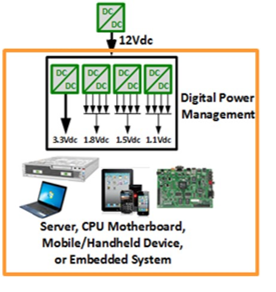

PSRR在电源管理芯片(PMIC)中应用广泛,覆盖包括电源稳压器、放大器等器件或电路的性能评估。尤其在当今典型的系统为处理器(如GPUs, SoCs, FPGAs)、高速串行接口(如SerDes,PCIe,USB)、高速并行数据(如DDR、LPDDR、GDDR)以及多路电源同时工作的需要稳定电源供应且对电源干扰抑制力较高的低压供电场景中,电源轨上的纹波噪声来自于电源的开关噪声和谐波、数字信号串扰、时钟耦合等诸多因素,由于系统对信号很敏感,如果电源对纹波噪声的抑制能力不够,会直接导致信号抖动、产生误码、影响系统稳定性并导致系统效率降低。

所有这一切使得预留给电源的纹波噪声裕量越来越小,从而要求高精度的电源纹波噪声抑制能力(PSRR)的测量。PSRR的测试已广泛应用于精密工业、汽车电子、医疗设备等行业中。

图1. 低电压应用场景

精密工业:在电源稳压器尤其是在LDO电源电路设计与应用中,对其PSRR性能的测试有助于为精密低压差电源供应的电源稳定性提供评估参考。如下图2展示的是一款用于数码相机、手机摄像头、可穿戴设备等上的LDO芯片datasheet上列出的必要的PSRR项目指标:

图2. LDO芯片PSRR项目(图片来自TI)

汽车电子:在汽车电子系统中,车规级电源器件/系统的PSRR测量可以更大限度地帮助评估电子器件/设备在车规级供电要求的稳定及安全工作特性。

图3. 车载电源系统

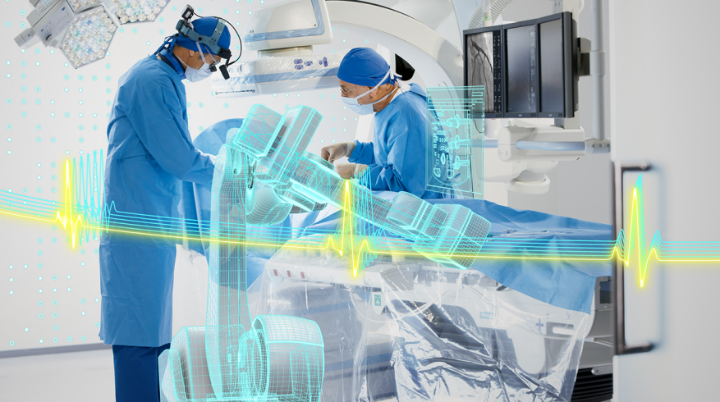

医疗设备:在医疗设备中,PSRR的测量可以帮助评估电源噪声对医疗设备精度和稳定性的影响,以最大程度减少电源噪声造成的干扰,确保医疗设备的可靠和安全以实现精确的读数和诊断。

图4. 医疗设备供电系统

PSRR在电源管理芯片(PMIC)中应用广泛,覆盖包括电源稳压器、放大器等器件或电路的性能评估。尤其在当今典型的系统为处理器(如GPUs, SoCs, FPGAs)、高速串行接口(如SerDes,PCIe,USB)、高速并行数据(如DDR、LPDDR、GDDR)以及多路电源同时工作的需要稳定电源供应且对电源干扰抑制力较高的低压供电场景中,电源轨上的纹波噪声来自于电源的开关噪声和谐波、数字信号串扰、时钟耦合等诸多因素,系统对信号很敏感,如果电源对纹波噪声的抑制能力不够,会直接导致信号抖动、产生误码、影响系统稳定性并导致系统效率降低。

需要关注的是在人工智能(AI)技术快速发展的今天,与之相关的电路/器件呈现极低的电压供电趋势,测试其电源管理芯片的PSRR可直接评估电源对纹波噪声的抑制能力,用于减少系统能量损耗,提高系统性能和效率,并且有助于延长芯片的寿命。

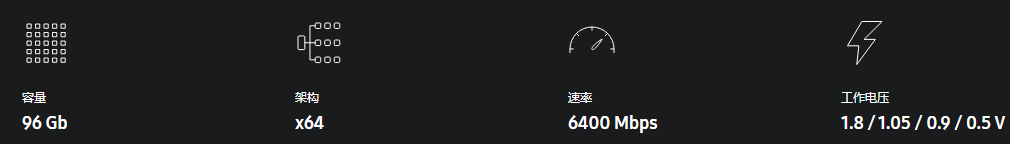

下图为一款用于人工智能(AI)的存储器LPDDR,其工作电压已低至0.5V,预留给电源的纹波噪声裕量越来越小。

图5. 用于人工智能(AI)的存储器LPDDR(图片来源:SAMSUNG)

鉴于其低电压的电源需求及高吞吐量的特性,如果要保障其持续运行在高算力的AI应用场景下,高稳定且对纹波噪声高抑制能力的电源供应是必要的保障,如果电源纹波噪声抑制能力不够,又会有什么影响呢?

图6. 高性能芯片易受电源纹波噪声的影响

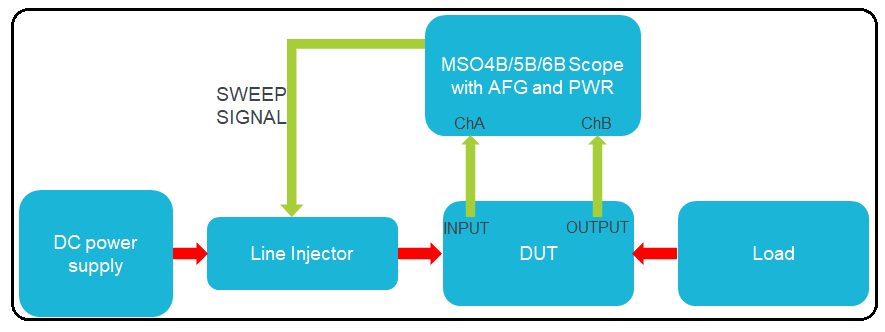

使用示波器对DUT电源输入端与输出端纹波做直接测试并绘制所需要的PSRR曲线即可。使用泰克Mainstream系列低本底噪声及高分辨率的示波器系统做准确测试,连接如下图示:

图7. PSRR测试连接示意图

Ø 通过示波器的AFG注入特定扫频信号至线性注入器后引入到DUT;

Ø 通过示波器系统分别测试DUT电源输入端输出端纹波;

Ø 通过示波器PSRR功能实现PSRR值的计算、数据记录及曲线绘制

最前沿的电子设计资讯

最前沿的电子设计资讯