关于继电器和螺线管,一个公认的事实是,在它们被驱动到致动状态后,只需要一半的线圈电压和四分之一的线圈功率就能可靠地维持致动状态。因此,任何螺线管或继电器驱动器如果持续施加全部初始致动电压来维持工作,就会浪费四倍于工作所需功率的电力。

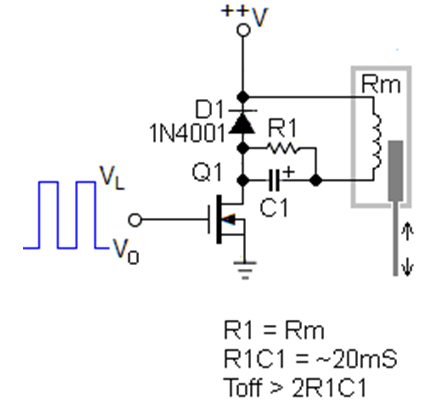

解决这一问题的最简单、最经济的(部分)方案如图1所示。

图1 基本驱动电路,其中C1致动,电流减半R1维持,然后C1在Toff期间通过R1放电。

但是,正如"简单而便宜"通常的情况一样,图1的解决方案也存在一些成本和复杂性。

虽然R1成功地将维持电流降低了一半,但它消耗的功率与线圈一样多。因此,总维持功率是致动功率的1/2而不是1/4,因此实际实现的功率节省只有理论值的一半。

当致动器关闭时,必须在下一个致动脉冲之前施加较长的恢复延迟,以便C1有足够的时间通过R1放电。否则,下一个致动脉冲的幅度将不足,并可能失败。在致动过程中,C1通过R1和Rm的并联组合充电,但在Toff过程中,C1仅通过R1放电,这一事实加剧了上述影响。这使得恢复时间是致动时间的两倍。

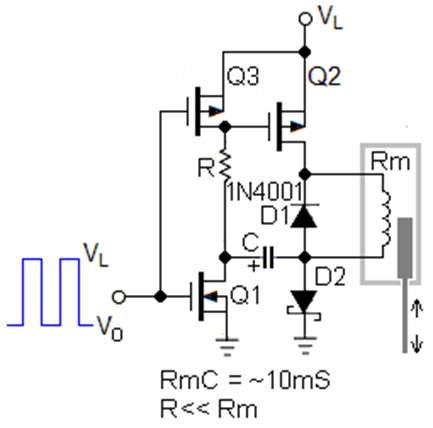

图2展示了一种性能更佳的解决方案,尽管它不那么简单和便宜,但它却是本设计实例的主题。

图2 Q1和Q2与C配合将VL增加一倍以致动,Q2和D2维持,然后Q3通过R使C迅速放电,从而为下一个周期快速恢复。

致动开始时,输入端会出现一个正脉冲,打开Q1,驱动线圈底端至-VL,同时打开Q2,将线圈顶端拉至+VL。因此,线圈两端出现2VL,确保了可靠致动。C充电完成后,肖特基二极管D2接管Q1的导通。这会将维持电压降至致动值的½,因此维持功率会降至¼。

在周期结束时,当输入信号返回到V0时,Q3导通,通过D2和R致动C的快速放电。事实上,恢复过程可以轻松地安排在比继电器或螺线管需要断开的时间更短的时间内完成。这样就不需要明确的周期间延迟,因此恢复时间实际上为零!

只能说:一分钱一分货!

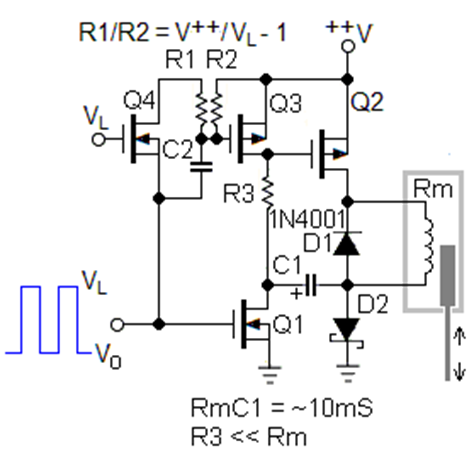

但是,如果即使将VL逻辑轨加倍,仍然无法产生足够的电压来驱动线圈,并且需要更高的电源轨,该怎么办?

图3利用先前的设计实例中描述的一些技巧解决了该问题:利用逻辑信号、交流耦合和接地栅极驱动CMOS图腾柱电路。

图3 添加电平移位Q4、R1和R2以适应++V>VL。

(原文刊登于EDN美国版,参考链接:Relay and solenoid driver circuit doubles supply voltage to conserve sustaining power,由Ricardo Xie编译)

最前沿的电子设计资讯

最前沿的电子设计资讯