国际电气电子工程师学会(IEEE)曾发表《国际集成电路设备和系统路线图》(IRDS)预测,到2037年,半导体工艺制程才将达到约0.5纳米,晶体管栅极长度为12纳米。

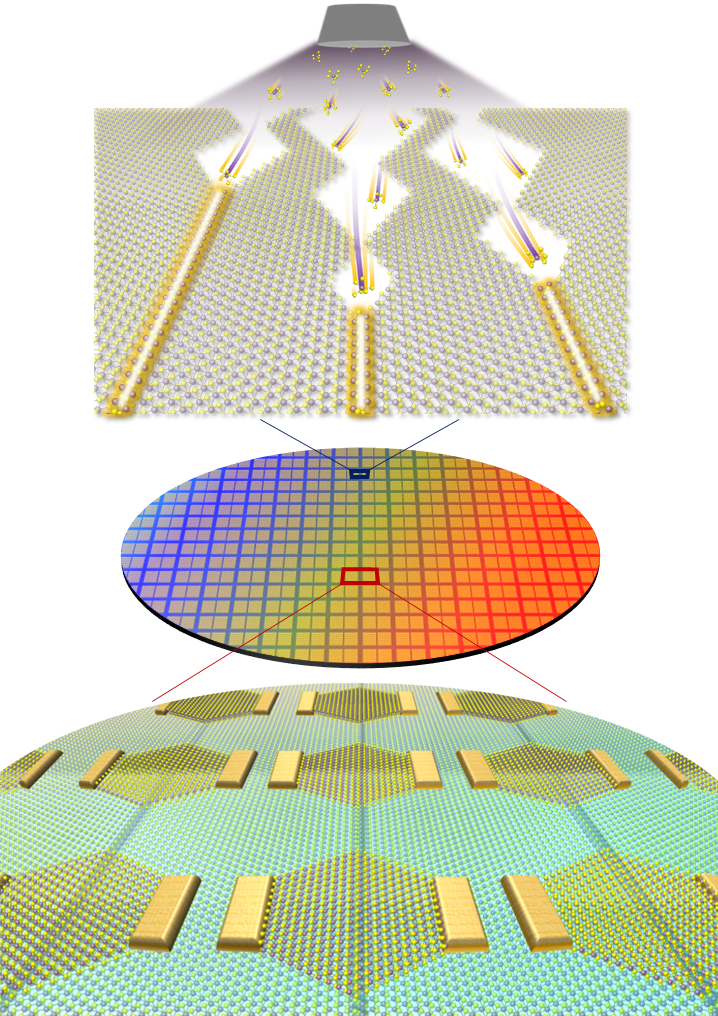

而在近日,韩国基础科学研究所(IBS)的研究团队取得了一项重大突破,通过一种新的方法,该团队成功实现了宽度小于1纳米的亚纳米级晶体管,并应用此工艺开发了一种用于二维半导体逻辑电路的新结构。

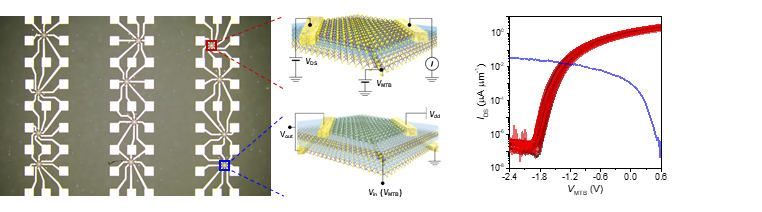

半导体器件的集成度取决于栅极电极的宽度和控制效率,其控制着晶体管中的电子流动。在传统半导体制造工艺中,由于光刻分辨率的限制,将栅极长度减小到几纳米以下几乎是不可能的。而二维半导体二硫化钼(MoS₂)的镜面孪晶边界(MTB),其宽度仅为0.4纳米,是一种天然的一维金属,使用这种材料制造超小型晶体管的栅极电极,可以克服传统光刻工艺的限制。

该团队通过在原子水平上控制现有二维半导体的晶体结构,将其转化为一维MTB,实现了一维MTB金属相,由这种1D MTB制造的晶体管栅极长度仅为3.9纳米,大大超出了IEEE对未来的预测。

在电路性能方面,与用于硅半导体器件小型化的FinFET或GAA等技术相比,1D MTB晶体管由于结构简单、栅极宽度极窄,可以将寄生电容降至最低,从而提高集成电路的稳定性。

研究人员表示:“通过外延生长实现的一维金属相是一种新型材料工艺,可应用于超小型半导体工艺,有望成为未来开发各种低功耗、高性能电子器件的关键技术。”

最前沿的电子设计资讯

最前沿的电子设计资讯