就像摩尔定律的终结一样,闪存的扩展挑战多年来一直是一个重大问题。随着嵌入式应用的技术节点缩小到28nm以下,嵌入式闪存正在达到其极限,因此必须缩小闪存单元的物理尺寸。

这种微型化对闪存和其他非易失性存储器(NVM)衍生物中的电荷捕获基本机制提出了挑战,使得在这些更小的节点上进行制造极为昂贵,且对于嵌入式应用而言不切实际。

此外,即使在嵌入式闪存可行的节点上,闪存单元的耐用性也有限,它们只能承受有限次数的编程/擦除循环,之后就会发生性能下降。

与MRAM和ReRAM等替代NVM技术相比,闪存的功耗更高。在嵌入式系统中,能效对于延长电池寿命至关重要,因此功耗是一个关键因素。在电源管理和其他高压应用方面,客户使用的是BCD(双极-CMOS-DMOS)工艺流程,该流程对FEOL(前道工艺)的修改(例如闪存所需的修改)更为敏感。功率器件往往对成本更为敏感,而闪存通常需要10个额外的掩模,制造成本非常高,会增加20-25%的晶圆成本。

然而,MRAM和ReRAM等新兴NVM的优势更符合较小工艺节点的先进嵌入式系统的要求。这些技术还可能颠覆更成熟几何尺寸(如40nm、65nm甚至130nm)的嵌入式闪存市场。这对许多供应商来说意义重大,尤其是对价格高度敏感的成熟节点。

MRAM(磁性随机存取存储器)因其非易失性、高运行速度和耐用性而备受关注。Everspin Technologies等公司已成功商业化MRAM,具有多种类型,例如切换MRAM(Toggle MRAM)和自旋转移力矩MRAM(Spin-Transfer Torque MRAM)。

通常,MRAM单元由两个磁性层组成:一个具有固定磁化,另一个具有可以切换方向的自由磁化。写入数据时,需要施加电流产生磁场,使自由磁化层与固定层平行或反平行,也就代表了二进制中的1或0。

然而,MRAM面临着成本挑战,因为其制造过程中需要许多薄层,这通常会使晶圆成本增加30-40%。同时,潜在的污染问题需要特殊的洁净室操作、专用工具和全面的质量控制措施,这通常需要单独的设施和生产线来生产MRAM,从而进一步增加成本。

此外,无线充电器和自动门锁等磁场可能会干扰IC中的邻近元件,给MRAM集成带来挑战,其中也包括安全风险。据报道,一些领先的消费电子公司由于此类干扰问题而拒绝考虑MRAM解决方案。而其他挑战还包括使用稀土材料,导致MRAM价格昂贵,并带来企业ESG问题和供应相关风险。

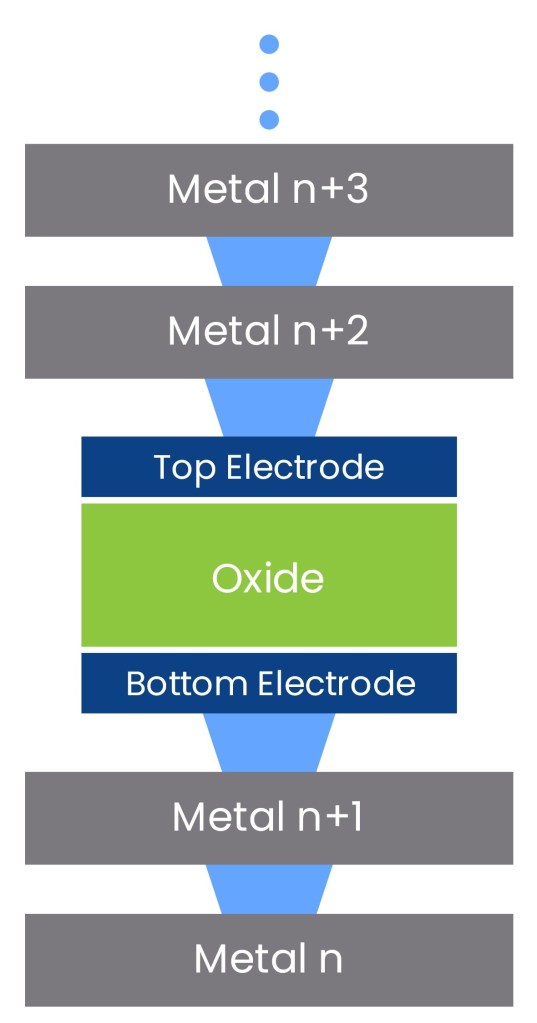

另一项新兴的内存技术是ReRAM(电阻式随机存取存储器),该技术得到了台积电、联电和Weebit Nano等独立ReRAM IP提供商的大力支持。ReRAM的工作原理是基于材料的电阻开关特性。ReRAM单元由夹在两个电极之间的薄绝缘层组成。

图1:ReRAM位单元示意。(图片:Weebit Nano)

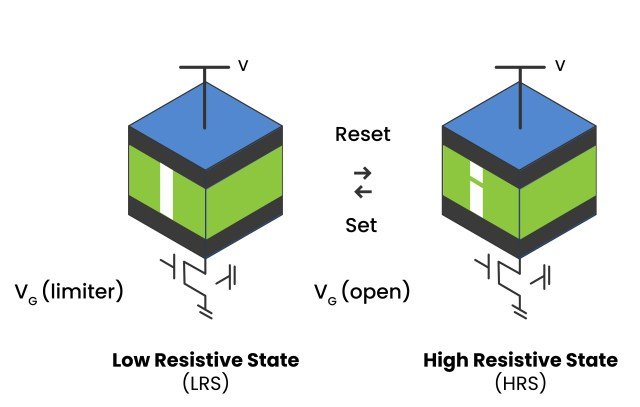

写入数据要在电极上施加定向电压脉冲,从而使绝缘层内导电细丝的产生或溶解。这种变化会将单元的电阻从代表二进制0的高阻状态(HRS)改变为代表二进制1的低阻状态(LRS),反之亦然。读取数据需要通过施加低电压来测量单元的电阻。

图2:Weebit ReRAM中的低阻状态和高阻状态。(图片:Weebit Nano)

与其他嵌入式NVM相比,ReRAM技术制造时需要的额外掩模更少。例如,Weebit Nano的ReRAM仅需要两个额外掩模,而闪存通常需要10个,这相当于增加的晶圆成本不到10%。而且,与MRAM不同,ReRAM不易受磁场影响。它还具有天然的抗辐射性。

与闪存一样,ReRAM也是非易失性的,具有快速的读写速度,并且功耗极低,因此非常适合节能应用。对闪存编程需要在写入前擦除整个扇区,这会导致时间和功耗问题。ReRAM是字节寻址或位寻址的,因此无需擦除周期,从而提高了先进应用的性能和耐用性。

尽管MRAM、ReRAM有诸多优点,但如今并非所有设计都开始使用MRAM或ReRAM。部分原因是设计师更熟悉外部闪存。虽然不够雅观,也不安全且效率低下,但它已经在使用中,而且工程师们有一种“能跑就不要动”的心态。

不过,由于与代工厂的合作以及各行各业的兴趣,新内存技术被广泛采用的潜力很大。主要驱动因素是现有解决方案无法使用的较小工艺节点,以及较旧节点的电源管理设计。这一趋势支持将模拟、射频、电源管理和微控制器与NVM集成在单个芯片上。

越来越多的代工厂正在增加ReRAM功能,甚至在全面认证之前就与客户签约。我们可以预见,ReRAM将在18到24个月内出现在许多新设备中,取代嵌入式闪存和外部NVM芯片,并实现经济高效、节能的系统集成。

(原文刊登于EDN姊妹网站Embedded,参考链接:Understanding the contenders for the Flash memory crown,由Ricardo Xie编译。)

最前沿的电子设计资讯

最前沿的电子设计资讯