在前不久的第九届上海FD-SOI论坛上,三星详述了和ST联合准备推向市场的18nm FD-SOI;GlobalFoundries再度提及12nm FD-SOI——并且给出了更明确的时间线;

年中CEA-Leti甚至宣布推出10nm与7nm FD-SOI试验线;Soitec在论坛上则预判边缘AI时代大潮之下,FD-SOI有希望走向主流...今年的FD-SOI究竟走到哪儿了?为什么参与者们忽然信心大增?本文尝试探讨AI大时代下,FD-SOI的现在和将来。

FD-SOI的技术优势我们也年年在谈,年年在重复。Handel Jones(IBS首席执行官)在圆桌的总结发言中说,FD-SOI技术已经被证明了是好的,优势也非常明确,这些都不需要再多说。

比如从工艺特性角度,FD-SOI允许更低的栅极电容和漏电流,latch-up immunity、更好的模拟信号及射频增益、更低的闪烁噪声、超低功耗,以及提到SOI就始终不得不提的body-biasing体偏置等...

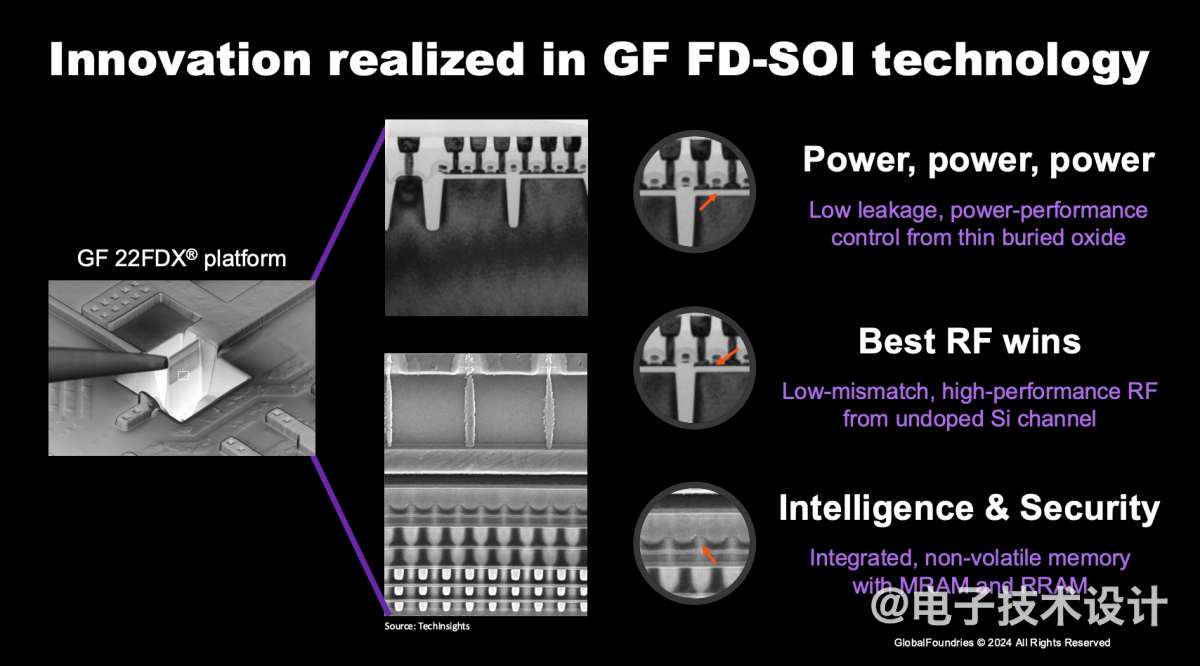

GlobalFoundries以及ST(意法半导体)仍然在主题演讲中大略概括了FD-SOI的技术优势。GlobalFoundries认为,FD-SOI技术的优势可概括为三点:(1)由薄埋氧层(thin buried oxide)带来的低漏电与功耗性能控制,显著表现之一就是我们常说的低功耗特性...

(2)最佳RF射频表现,由无掺杂硅沟道(undoped Si channel)带来的低失配(low-mismatch)、高性能RF;(3)智能与安全,这一点主要说的是集成的嵌入式非易失性存储应用如MRAM, RRAM。

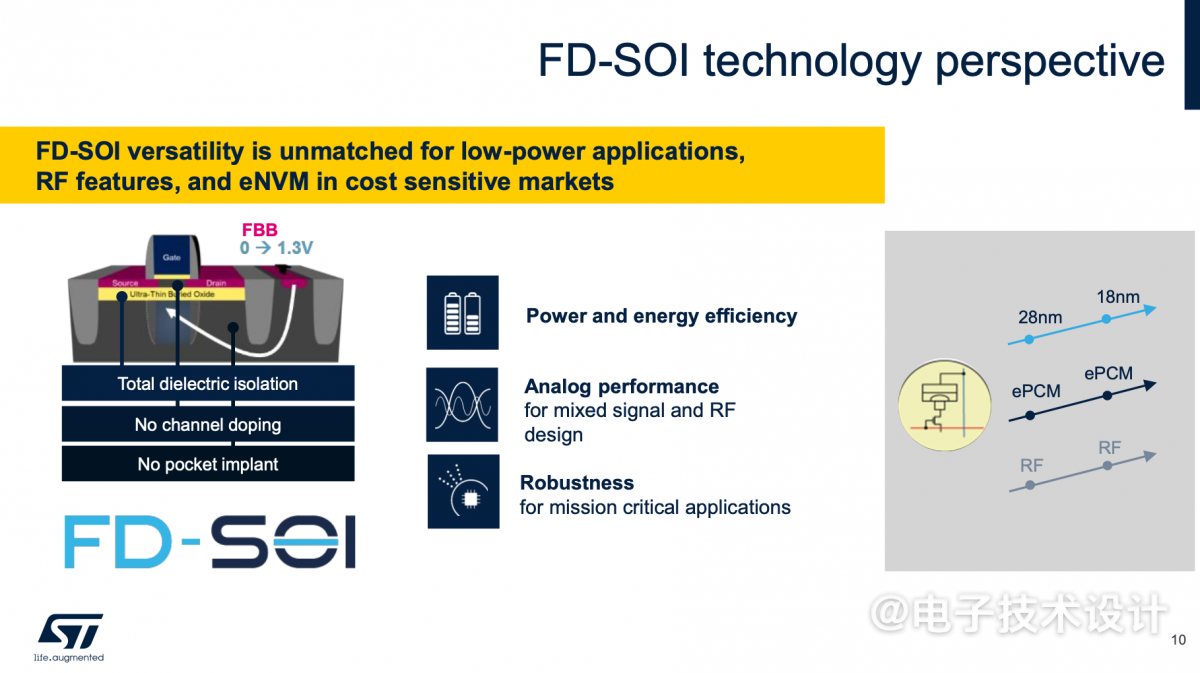

ST总结的FD-SOI技术特性基本也是类似的3点:(1)功耗与能效;(2)模拟性能,对于混合信号与RF设计表现出高价值;(3)鲁棒性,在任务关键型应用上表现出优势。所以总结起来,FD-SOI对于低功耗应用、RF功能,以及成本敏感市场的eNVM,是“无与伦比的”。

这些都已经谈过很多次了。不过此处可以再谈一个此前我们撰文未曾提及过的属于FD-SOI的优势。戴伟民(芯原股份创始人、董事长兼总裁)在圆桌环节略提了提adaptive body-biasing(ABB)的价值,除了在需要高性能和闲置standby状态下,有助于实现动态的功耗控制;

还有一点,“在芯片tape-out的时候,我们发现process会飘,存在最快、最慢的情况。”戴伟民提到,“两边都顾及到就需要投入成本和时间。FinFET工艺在这方面的控制很严格。而在body biasing的帮助下,做好bias范围和device的控制,就能节约时间和成本。”

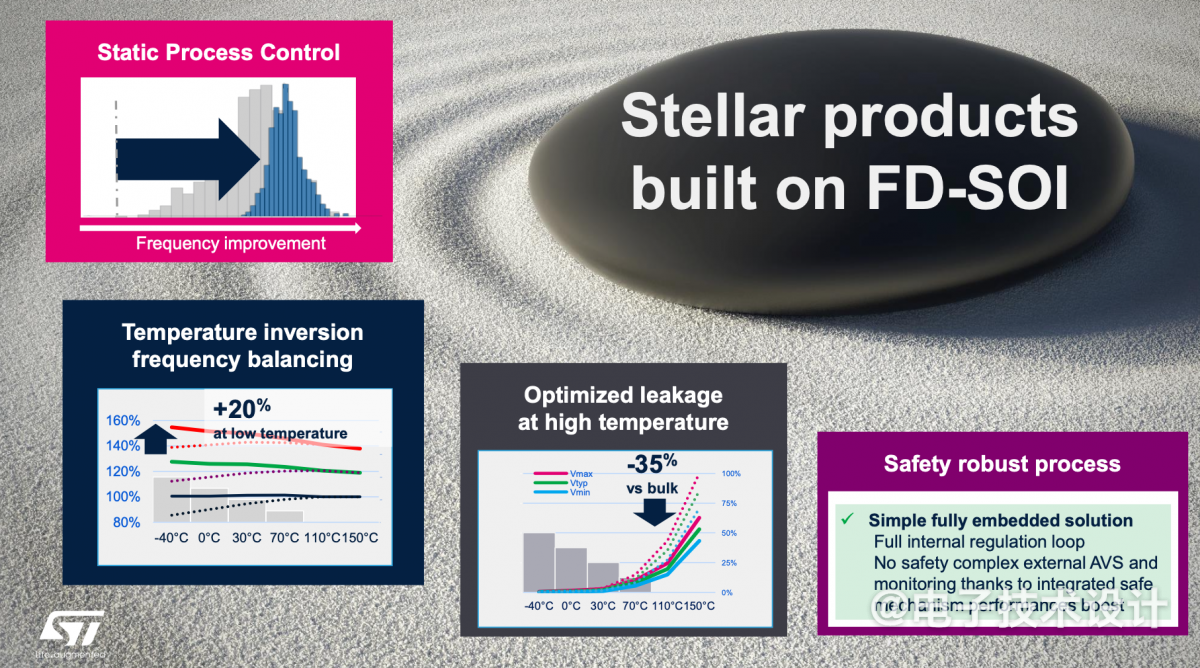

戴伟民所指,我们猜测可能是ABB可用于缓解工艺变量(process variation)和其他因素带来的影响,则流片或制造可更不受制于工艺误差这一优势。John Carey(意法半导体射频与通信部总监)也在演讲中谈到了相似的特性——“static process control(静态工艺控制)”。

“在打造一款产品,以期获得产能和稳定性时,我们总是希望能够控制工艺参数。”John说,“可以用静态工艺控制,基于自适应偏置(ABB)在低温下控制性能(regulate the performance),在高温下降低漏电。”这一点也给我们留下了比较深刻的印象。

技术专家形容body biasing特性让设计者可将其当做“另一个栅极”使用,即做所谓的背栅控制,对应地增加了晶体管特征参数调节的灵活性。

这项特性实际也令FD-SOI在不同应用场景下有了不同的优势和价值,除了这里提到的缓解工艺变量的影响、功耗/温度管理,还有射频应用利用body biasing的动态调节,可达成信号线性度的提升;可靠性方面,可一定程度做老化补偿;据说在安全性上,甚至还能让硬件层面的边信道攻击(side-channel attacks)变得更难...

很多人真正关心的,应该是FD-SOI结构的先进工艺进展情况。毕竟是否上先进工艺,仍然能够表现这一技术方向现在和未来的生命力如何。除了文首提及今年6月CEA-Leti宣布10nm和7nm FD-SOI试验线亮相这种HVM可能还比较遥远的话题,真正已经明确的是GlobalFoundries的12FDX以及三星18FDS。

先谈谈三星的规划。ST和三星今年3月联合宣布18nm FD-SOI工艺技术,当时主要提到了ePCM存储上的应用;以及对应基于新工艺的STM32 MCU,今年下半年开始出样,明年下半年计划量产。

在此之前的28nm FDSOI已经在射频、汽车、嵌入式存储领域有了大量应用。包括35款已经成功量产的产品,产能和良率稳步提升。其中包括据说是全球首个28nm的eMRAM,稳定IP良率 >98%(D0 < 0.2cm²),数据logging型应用的nvMRAM产品endurance cycle > 1E14。

所以Jinha Park(三星电子18FDS工艺集成与项目经理)对于三星18FDS也相当有信心。他说,此前ST就期望借助18nm工艺联合打造MCU,其中也包括ePCM和3.3V ZG器件。三星一方面审视了自家的主流14nm工艺,准备基于此移植(port)18nm FDSOI的平行工艺。

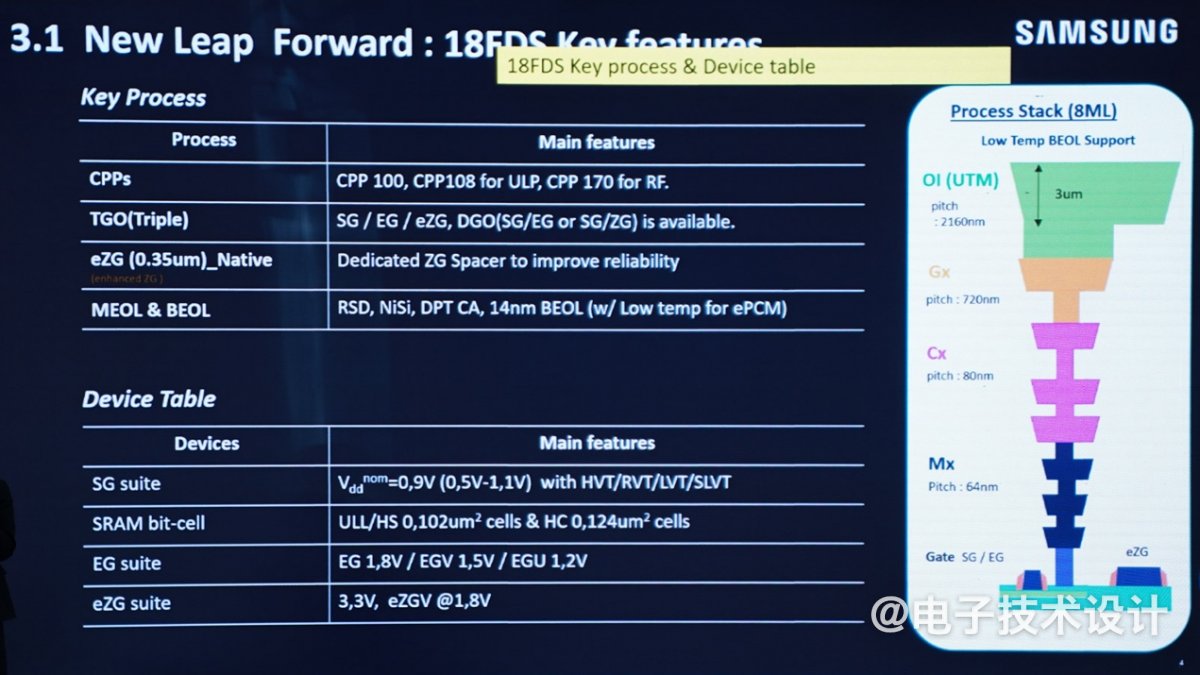

很难得的,三星这次公布了一小部分有关18FDS的CD关键参数,虽然也并不算详尽,仍然足够明确当代工艺名称标注18大致是个什么水平——可惜GlobalFoundries仍然没有公开任何12FDX的相关CD,也无从比较两家foundry厂在18/12节点上具体是如何定义的。具体如下图所示:

Gate pitch栅极间距方面的多种选项,着眼于面向性能为先(CPP100)、超低功耗(CP108)和射频(CPP170)应用。这里的TGO应该是指对于triple gate oxide的支持,而非单纯的DGO(dual gate oxide)。

Jinha此处特别强调了eZG器件,也就是enhanced Zero Gate——最小化漏电流的器件类型,据说用到了一种专门的spacer(阻隔层)来提升器件可靠性;以及BEOL参考了并行的14nm工艺,不过有针对ePCM的低温技术,达成更高的效率。

其他器件相关关键特性,以及不同SRAM单元面积在表中都有列出;右边这张图也给出了低温BEOL金属堆栈不同维度的间距数据——这应该算是十分难得的珍贵一手数据了。

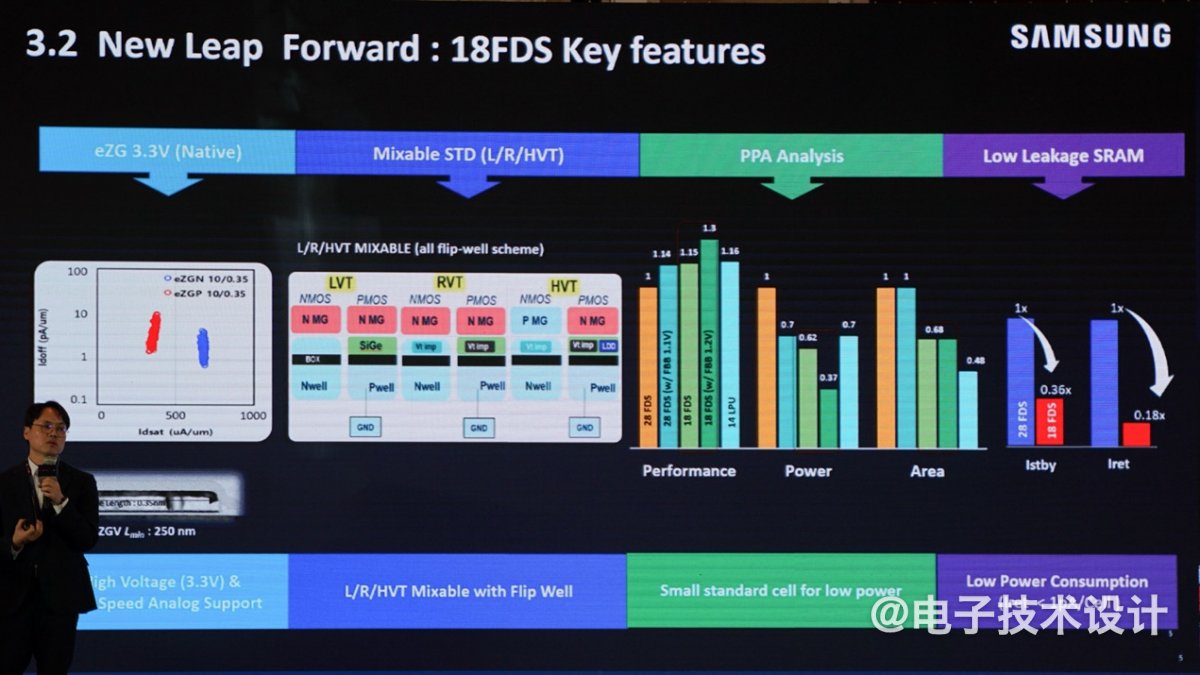

有关18FDS的关键提升,Jinha主要列了4点,分别是eZG 3.3V,据说达成了最佳性能(高速模拟支持);其次是可混用的标准单元库(mixable STD, LVT, RVT, HVT);以及PPA角度来看,从图中可见与28nm FDSOI, 14LPU等的对比数据,这里18FDS在body biasing的加成下,也能获得更出色性能和功耗成绩...

最后就是着重强调的低漏电特性,对于超低功耗设备的支持,相比28FDS在待机电流(Istby)和保持电流(Iret)方面都有十分显著的降低。

另外,Jinha也谈到了NVM解决方案从三星既有工艺的easy porting,也就是工艺的移植对三星而言也并不复杂——这一点大概也是为了表达18FDS效率上的信心。

从三星的计划表来看,18FDS一方面面向与ST的合作,推高性能、汽车、超低功耗与连接应用;另一方面三星似乎也在考虑面向更大市场的所谓general foundry通用代工服务——这一点就要求对应的foundation IP等生态构建能够跟上了。“我们考虑的时间线,是在2026年末,后续就可以开始真正进行生产了。”

不过这里Jinha针对路线图,在演讲中用的比较多的词是“consider(考虑)”,所以18FDS的“通用代工”服务全面启动,可能还是要看包括IP等配套周边的搭建情况。

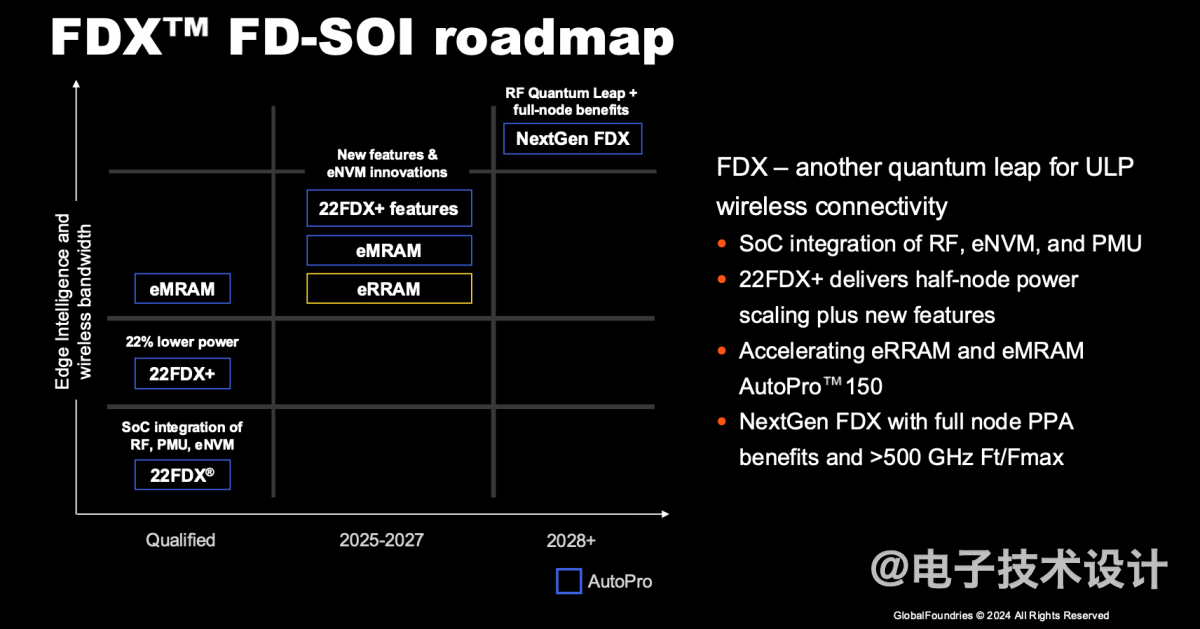

GlobalFoundries这边,12FDX也提了好些年了。今年再度提及12FDX,似乎时间线更明确了:Ruby Yan(格罗方德产品线总监)在圆桌环节说,计划中的首个PDK是2026年放出;生产则计划于2027年进行。

汽车似乎的确是FD-SOI的热门应用,图中的AutoPro指向车载质量级别的工艺

不过从演讲中洪启财(格罗方德亚洲区总裁兼中国区主席)展示的FDX路线图来看,应当是指代12nm的NextGen FDX被划到了2028+时间线。2025-2027区间内活跃的主要仍然是22FDX+——针对这一22FDX的改良工艺,我们去年的文章已经做过解读。

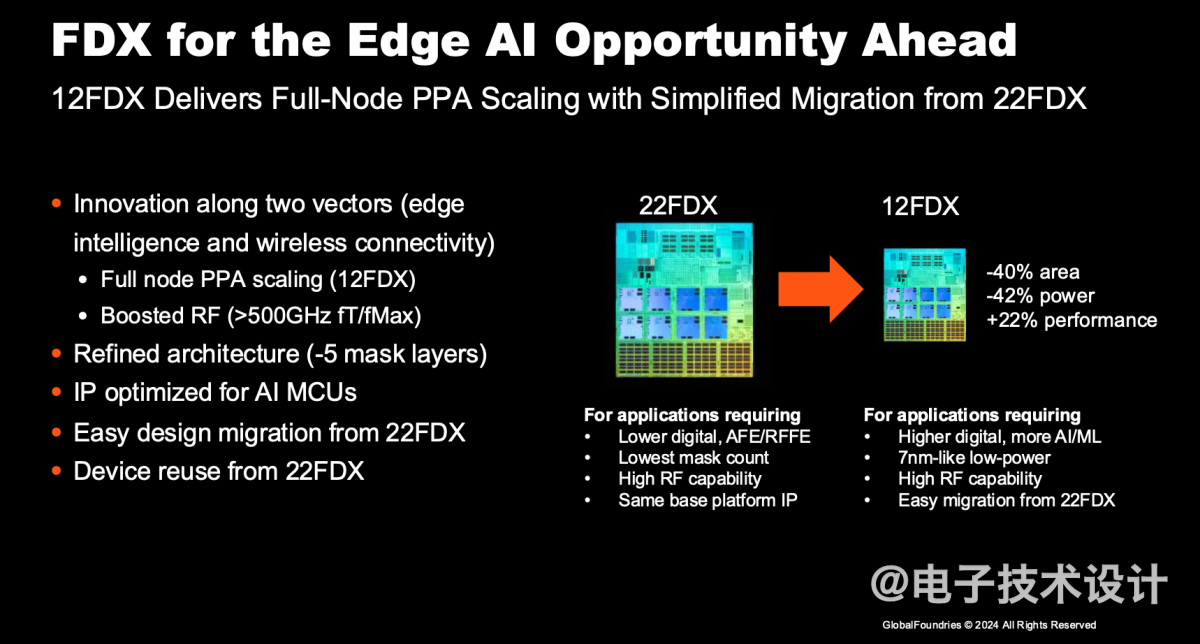

相关工艺提升更明确的信息是,GlobalFoundries认为12FDX会在边缘AI时代下发光发热,是22FDX之后的“完整工艺节点(full-node)”PPA提升,以及针对RF更高的fT/fMax;而且设计迁移比较容易——22FDX器件可复用。

虽然没有器件相关数据分享,不过PPA提升量级已然明朗:面积缩减40%,功耗降低42%,性能提升22%。

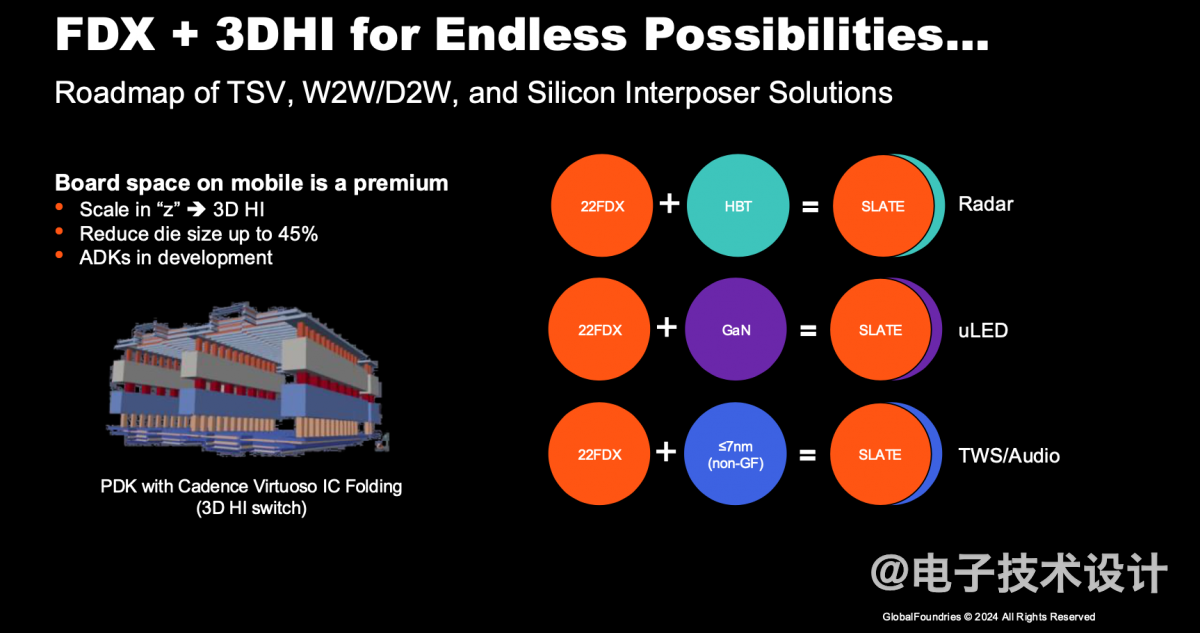

除此之外,在配套技术上,还有个关键信息——虽然不是专门针对12FDX的,即3D堆叠(FDX + 3DHI)。“比如现在已经有客户将我们的wafer(22FDX)用作base,其上再放GaN最后形成microLED。”如图所示,还有雷达、音频等方向的应用。Ruby说,基于3D封装,未来会驱动更多新的应用发展。

值得一提的是,在圆桌环节Jinha提到,12nm FDSOI应当也需要考虑到18nm FDSOI的部分关键技术特性。只不过这个时代背景下,foundry厂对节点的定义都有差异,所以这里的18与12很难同台竞技。

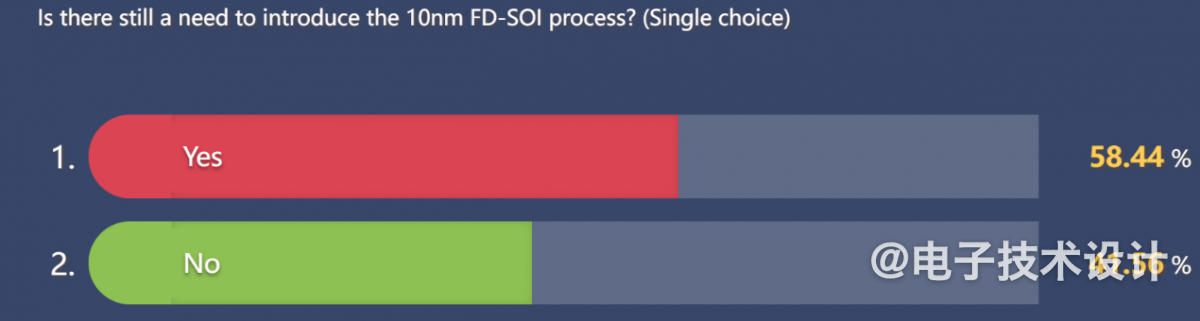

有关12nm之后更先进工艺的问题,圆桌环节有个观众投票问题:是否需要推出10nm FD-SOI工艺。James Zhang(Soitec边缘与人工智能部门高级业务发展经理)说,一方面对于FD-SOI产业而言,还是需要个明确的路线图,那么就不能只把眼光放在28nm, 22nm这样的工艺上,这也是出于市场方面的考量。

另一方面,““AI是行业的热门话题,行业需要更多的AI功能。”James说,“藉由body biasing,10nm的FD-SOI也许就能达到FinFET 7nm, 5nm的程度,这也会成为10nm研究项目的主要驱动力。”

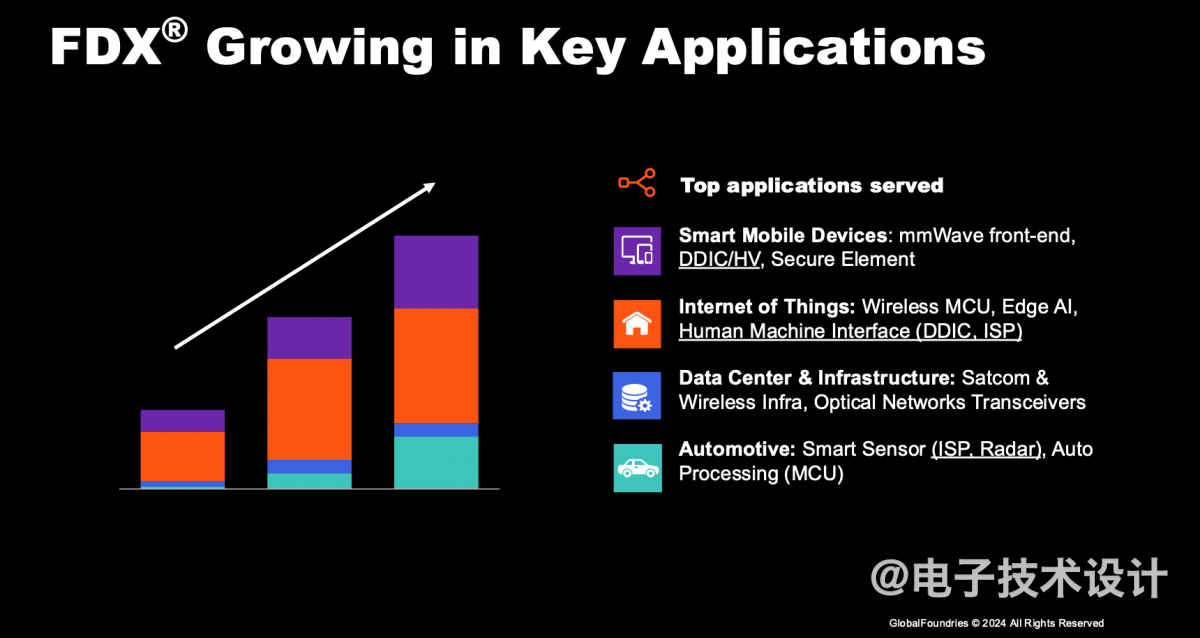

AI实际上也是会议现场Soitec, IBS, GlobalFoundries等都认定会推动FD-SOI接下来高速发展的关键驱动力。Soitec对于FD-SOI的乐观态度甚至有些令人惊异。Philippe Flatresse(Soitec产品市场经理)认为FD-SOI的三大市场驱动力分别是:智能设备、汽车、5G,而边缘AI是贯穿这几个驱动力的。

具体到应用类型,包括按需性能型(performance-on-demand)、电池驱动型、集成RF,以及eNVM存储。今年GlobalFoundries在更新的FD-SOI关键应用中格外强调了DDIC(显示驱动IC)——据说后续就会起量,成本相较FinFET也有显著优势…

基于市场驱动大方向,我们还是回到Soitec的视角。首先是智能设备,也就是边缘AI:“我们需要高效和低功耗技术。这是FD-SOI会在未来几年的市场中扮演重要角色的原因。”Philippe尤其提到了边缘AI推理的潜在市场需求,这类边缘AI设备的低功耗、低成本要求很高,“我们会成为下一代智能家居、可穿戴、医疗、环境智能传感等应用的一部分。”

其次是汽车,汽车电子在整车价值中的占比提升,驱动了对半导体产品的需求。汽车市场,“我们从10+年以前就以28nm技术开发视觉处理器。”且据说市场占比已经相当高,“还有面向IVI信息娱乐系统应用的MCU也实现了量产,未来20年还将持续这一趋势。”

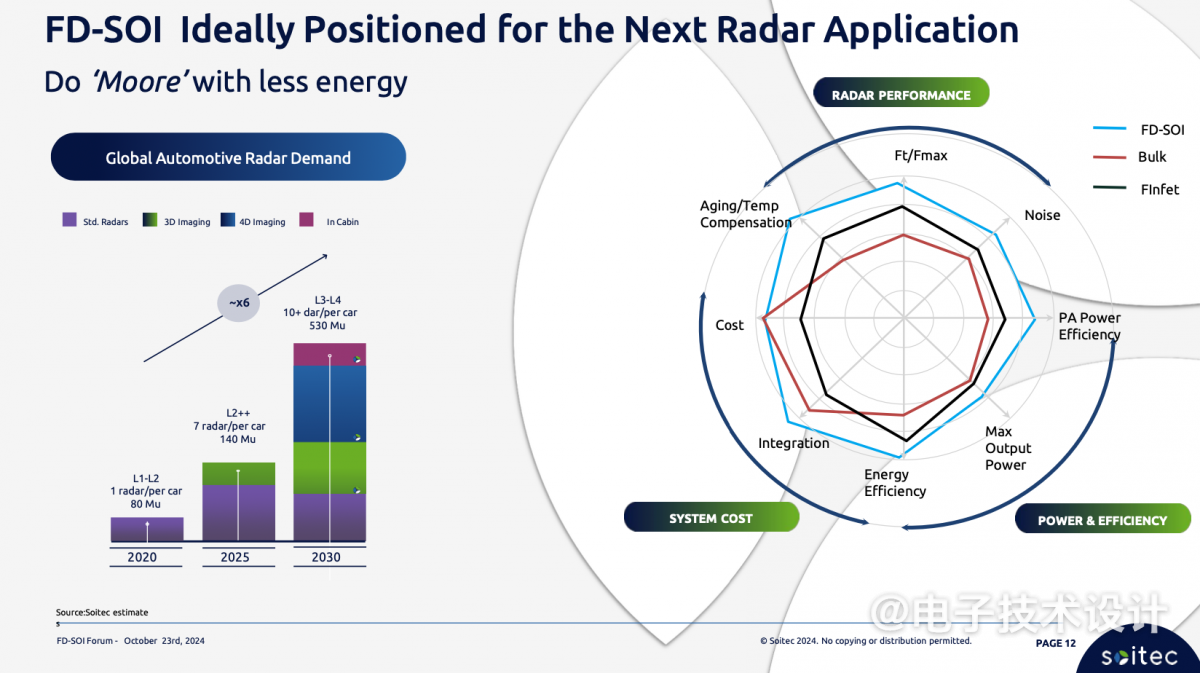

Soitec认为,汽车市场上FD-SOI的两个潜在市场机会在区域控制器(Zonal controller)和雷达上。尤其是雷达,L2+汽车现在每辆车已经装载有7个雷达,随着自动驾驶等级提升,加上4D成像雷达普及和舱内雷达需求进一步增加,2030年之前的市场需求超过5.3亿。

“由于FD-SOI出色的RF性能,更好的fT/fMax,以及噪声参数;借助body-biasing技术,我们还能补偿老化,应对温度变化。”加上FD-SOI在数字逻辑方面的表现,将RF和数字部分融合到一起,能达成更大的优势。Soitec对于FD-SOI就汽车应用的预期是,“transforming the automotive”,上升到了减小芯片面积、并在生产和使用环节节能减排的高度。

所以总的来说,在时代趋势需求更多毫米波应用、更多TOPS/W,更高的连接和效率要求的背景下,Soitec眼中的FD-SOI及其substrate将真正开始发光发热。包括在Soitec的展望中,相比现在+50% fT/fMax;降低40%的总体功耗;提升50%的逻辑密度,并对应的降低成本。

在我们看来,这很像是将FD-SOI摆在了“走向主流”工艺的语境下。

最后回到文首提到的Handel所说FD-SOI技术本身已经被证明是好的技术,优势也非常明确。“但我们需要生态系统,需要起量。”在论坛下午场的专题“FD-SOI的设计实现”探讨中,我们仍然可以看到芯原在提供FD-SOI工艺相关的IP与平台方面非常积极。

仅是芯原一家就已经在22nm FD-SOI工艺上,提供了59个模拟与混合IP,囊括基础IP, DAC, 接口协议等IP;RF与基带IP方面也基本涵盖了包括蓝牙、GNSS、Wi-Fi等在内的主流标准。而EDA工具方面,芯和也强调在22FDX工艺上与GlobalFoundries的合作,加速下游客户FD-SOI技术的采用...

圆桌论坛甚至都开始谈FD-SOI + chiplet的话题,或许也表明FD-SOI的确有进一步起量的大好前景。“对我来说,chiplet是FD-SOI的一次机会。”“但还是那句话,我们需要生态。”Handel总结说,“我们仍然只是市场的一小部分。”“FinFET仍然是供应链价值的大头。”

“我们需要开发IP生态,需要开发应用,需要去做设计,需要生产制造能力。FD-SOI发展了这么久,一部分原因就是生态始终还是太窄。我们走向12nm,就需要对应的wafer工厂产能;产能的确会提升,但是否已经足够,资金又从哪里来?”

“我们之所以能走向12nm,是因为我们在28nm, 22nm和潜在18nm上产生或能够产生高营收。”“但再往12nm以下去走,首先就需要12nm有足够的量,一步步来。”Handel谈到,FD-SOI要往chiplet走,对生态就提出了更高的要求,“即便我们都理解了技术的优势,生态还是需要建立起来,才有可能往下走。”

“我们还是要看到,FD-SOI在电池续航、生成式AI、可穿戴设备等领域的潜在发展机会,这些都会成为关键驱动力。”Handel在总结中说,“但走向10nm/7nm之路,我想我们还是需要好多年的。”

最后有个有趣的思考题,是戴伟民在圆桌环节提出,但最终没有讨论的一个议题,在此作为本文的结尾。我们知道GAAFET也有相当出色的模拟和RF特性。关注半导体尖端制造工艺的读者应该知道,GAA(Gate-All-Around)是埃米时代要走向主流的器件结构。所以问题是,“我们的未来究竟是直接迈向GAA,还是将FD-SOI技术推向极限?”

最前沿的电子设计资讯

最前沿的电子设计资讯