为了突破GPU内存的容量限制并维持其高性能,由韩国科学技术院(KAIST)支持的初创公司Panmnesia日前开发出号称全球首创的两位数纳秒级延迟CXL控制器IP,以及GPU内存扩展解决方案,可利用低成本存储介质进一步扩展GPU的系统内存至TB级。

随着大语言模型(LLM)的使用越来越普遍,数据中心对于内存的需求与日俱增,目前的当务之急是必须在维持合理性能的同时,以符合成本效益的方式扩展内存容量。

新的开放标准——Compute Express Link (CXL)提供了一个解决方案,通过连接多个可根据需求独立扩展的系统设备,部署可扩展的集成式内存空间。CXL控制器则可在硬件中自动处理缓存一致性管理等内存管理工作,这表示用户不需要担心手动管理集成的内存空间。

但最大的挑战在于延迟。相较于本机内存的存取,客户期望在扩展内存的同时不至于大幅降低性能,因此,如何让扩展内存所造成的额外延迟尽量降至最低至关重要。

Panmnesia表示,其新的CXL ASIC IP将在这方面发挥重要作用。该公司新开发的CXL控制器IP具备这种内存扩展能力,能以低延迟执行CXL的所有通信作业。该公司在其新闻稿中表示,采用其CXL IP的CXL控制器能够达到两位数纳秒级的往返延迟,比其他任何相关报导的时间都要短。该公司能够实现如此低延迟的方法是在所有相关层(包括物理层、链路层和事务层)全面优化控制器的操作。该CXL控制器IP可应用于各种系统设备,例如CPU、交换机、加速器和内存扩展器,从而自动化并加速一系列的内存管理操作。

因此,该公司推出了名为“CXL-GPU”的GPU存储扩展解决方案,可增加GPU的内存容量,同时优化AI服务的延迟。此解决方案通过CXL连接多个存储设备,构建出TB级的内存空间,并将其集成至GPU内存空间。大规模AI服务的数据与模型参数可存储在此集成内存空间中,让GPU存取并处理这些数据,以提供AI服务。这些低延迟的CXL控制器可处理内存管理作业,同时部署在GPU和存储设备中。

图1:CXL-GPU存储扩展解决方案不仅增加GPU内存容量,同时优化AI服务的延迟。 (来源:Panmnesia)

Panmnesia表示,虽然延迟优化是各行业的共同需求,但对于提供LLM和推荐系统等AI服务的公司来说尤其重要。这是因为延迟会直接影响用户满意度以及AI服务的营收。

Panmnesia表示,相较于购买多个高端GPU以确保内存容量的传统方法,这种基于CXL的存储扩展解决方案能够根据需求选择性地增加内存资源,因而能将AI服务的服务器建设成本降至最低。低延迟的CXL控制器可最大限度地减少内存扩展带来的开销,从而保持合理的性能。

Panmnesia表示,该公司已经集成其CXL控制器IP以及基于开源架构开发的定制GPU,打造出CXL-GPU的硬件原型。在此原型上的评估结果显示,其CXL-GPU解决方案可望超越传统的GPU内存扩展解决方案约3.23倍。

Panmnesia首席执行官Myoungsoo Jung说:“基于CXL控制器IP的GPU存储扩展解决方案有助于AI服务供应商显著降低其服务器建设成本。虽然推出这款解决方案是为了扩展GPU内存容量,但低延迟的CXL控制器IP也是云计算和高性能计算(HPC)中高效内存扩展的关键组件。”

为了展示其技术能力,Panmnesia采用了几种评估流程。首先,它比较了三种不同的GPU系统,以应对庞大数据的挑战。具体而言,UVM通过页面错误按需分配内存,提供主机与GPU共享的虚拟地址空间。

CXL-Proto采用CXL端点原型来扩展GPU存储空间,其延迟时间为250ns,符合三星(Samsung)和Meta的报告。

CXL-Opt也通过CXL实现GPU存储扩展,但采用Panmnesia CXL控制器和其他解决方案来优化读/写延迟。

下面的第一项评估是比较三种不同系统的运行时间,数值以UVM的运行时间为标准。

图2:核心运行时间。(来源:Panmnesia)

结果显示,在所有测试的GPU核心中,UVM的性能最差。Panmnesia表示,这是因为UVM在处理GPU页面错误时受到主机运行时间介入的影响。此外,由于UVM是以页面而非高速缓存行的粒度来迁移数据,因此数据传输量往往大于GPU核心的实际需求。相较之下,CXL允许GPU通过加载/存储(load/store)指令访问扩展的存储空间,因而免于受到主机运行时的干扰以及不必要的数据传输问题。这使得CXL-Proto的运行时间比UVM短1.94倍。通过采用优化的CXL控制器,Panmnesia的CXL-Opt将运行时间进一步缩短1.66倍。

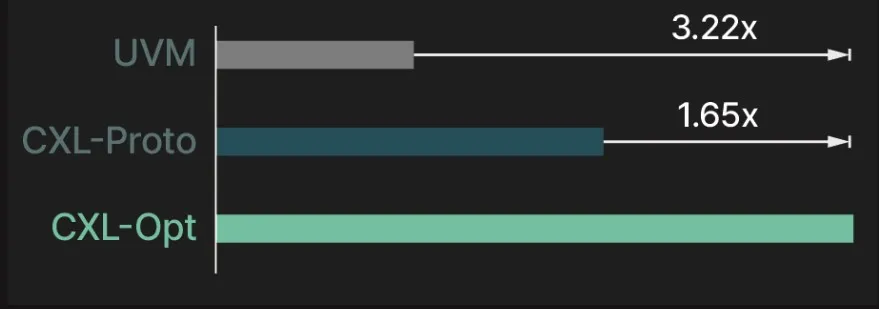

图3显示在GPU核心运行期间收集到的IPC (进程间通信)值。

图3:在GPU核心运行期间收集到的IPC值。(来源:Panmnesia)

图中显示Panmnesia CXL-Opt分别比UVM和CXL-Proto快3.22倍和1.65倍。

(原文刊登于EDN姊妹网站Embedded,参考链接:Two-digit nanosecond latency CXL IP addresses GPU memory expansion,由Susan Hong编译。)

最前沿的电子设计资讯

最前沿的电子设计资讯