基于电压频率转换器(VFC)与计数器经典组合的模数转换已经存在了几十年,主要是因为它具有一些经得起时间考验的持久优势。VFC的数字化是天然集成的,因此具有固有的高噪声抑制能力和可编程分辨率(如果您想要更多位数,只需计数更长时间)。遗憾的是,它的转换速度并不优秀。

有用的分辨率(8位或更多位)数十微秒的VFC转换时间需要数十兆赫的输出频率。现有的VFC设计可以达到这样的速度,例如Jim Williams令人惊叹的100 MHz King Kong和我自己设计的“带半回收电荷泵的20MHz VFC”。然而,这些可用的解决方案只会带来另一个潜在的棘手问题。该用什么做计数器?

通常VFC最理想且最具成本效益的伙伴是µC的板载计数器-定时器外设(CTP),它通常可提供16位分辨率,且无需增加任何额外组件成本。遗憾的是,由于需要通过板载CTP逻辑对每个输入脉冲周期进行多次(例如四次)采样,因此最大计数率被限制为µC内部时钟的一小部分(通常为¼)。

结果就是,对于20MHz的内部时钟,5MHz才是可实现的最快CTP计数率。

当然,外部硬连线计数器外设可以很容易地适应快速VFC(好吧,也许Kong不是那么容易),但是成本、组件数量和电路板面积使得这个选项相当没有吸引力。

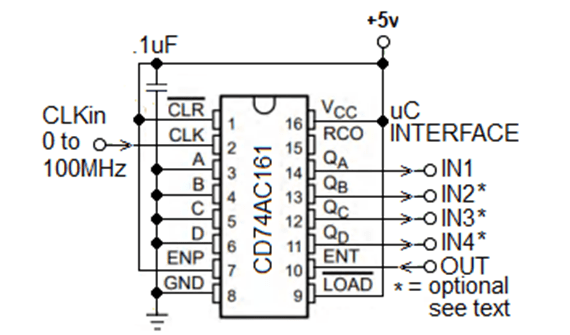

图1所示的是一种折衷拓扑,它将CTP的最佳功能(提供大量位)与单个外部4位MSI预分频器/累加器芯片相结合。这将外设的速度提高了16倍(因此在CTP 5 MHz的最高频率下可达到80 MHz),但代价是(最多)增加了四个通用I/O(GPIO)引脚。

它的工作原理如下。

图1:100MHz MSI计数器预分频并累积VFC LSB,以便笨重的CTP可以应对。

1.五个GPIO引脚已被编程,用于与预累加器连接:

a.四个输入(IN1至IN4)

b.一个作为输出(OUT)。

2.IN4也被编程为选定CTP的输入,该CTP被编程为16位累加。

每个VFC集成周期包括以下步骤:

请注意,如果最大VFC输出与最大CTP计数率之比小于8x,则只需为接口分配三个INx引脚(Xx=[ccc cccc cccc cccc ciii]),并将IN3编程为CTP输入。如果小于4x,则只需分配两个(Xx=[ccc ccc ccc ccc ccii]),依此类推。

如果简化算法比节省GPIO引脚更重要,则可以连接第六个输出引脚 并在转换开始时将其脉冲为低电平,以将INx位重置为零,同时对CTP位进行类似的预加载。这样就可以省去转换步骤中的第6和第10步。

并在转换开始时将其脉冲为低电平,以将INx位重置为零,同时对CTP位进行类似的预加载。这样就可以省去转换步骤中的第6和第10步。

(原文刊登于EDN美国版,参考链接:Preaccumulator handles VFC outputs that are too fast for a naked CTP to swallow,由Ricardo Xie编译)

最前沿的电子设计资讯

最前沿的电子设计资讯