最近的一个设计实例“简单又实用,一起看看这个不寻常的多功能ADC前端”,提供了一个非常特殊的ADC前端(见图1),它包括一个可编程增益(PG)仪表放大器(INA)。它使用PWM控制飞跨电容器来实现110dB CMRR、高阻抗差分输入和负时间常数指数放大,具有超过100个离散可编程增益级,内置的采样和保持(S&H)功能又为其锦上添花,因此可称其为PGINASH。

图1:PGINASH:具有INA输入、可编程增益和采样与保持功能的非常规ADC前端。

由于A1c的增益为(R3/R2+1)=2,在PWM=1增益积累阶段,从U1c的输出通过U2a和R1到C建立的连接产生正反馈,使得C上捕获的电压与(负)时间常数Tc(标称)呈指数倍增:

Tc = R1*(C + Cstray) =

= 14.3k*(0.001µF + (8pF (from U2a) + 1pF (from U1c)))

= 14.3k*1009pF = 14.43µs

= 10µs / ln(2)

G = gain increment of 20.1 = 1.0718 = 0.6021dB per us of accumulation time T

G10 = 2.0 = 6.021dB per 10µs of T

This combines with A1c’s fixed gain of two to total

Nominal net Gain = 2GT/10µs

当然,这里的关键词是“标称”。R1和C都具有非零公差,可能只有±1%,R2和R3也是如此。此外,由于U2开关到开关导通电阻不匹配,可能会产生进一步的时间常数误差,因此也会产生增益误差。最坏的假设所有时间常数组件公差的最坏情况相互叠加,A1c的增益可能会变化±2%,G的变化高达±3%。这对于精确的数据采集来说过于离谱!该怎么办?

建议使用以下步骤作为简单的基于软件的电路校准方法,使用连接的ADC,在校准过程中只需要将两个校准电压手动连接到IA输入端,即可消除导致前端误差的各种错误。

第一个校准电压(Vcal)用于明确测量原有增益因子。其工作原理如下:

Vcal = Vfs/Vheadroom

其中

Vfs = ADC full-scale Vin

Vheadroom = (2*1.02)*(2*1.04)2 = 8.8

举个例子如果Vfs = 5v, Vcal = 0.57v

Vcal的绝对精度并不是特别重要,+/-1%就足够了。但在校准过程中,它应该稳定在1 lsb以上。将Vcal连接到INA输入端,然后进行两次ADC转换:D1的增益累积时间T=10µs,D2的增益累积时间T=20µs。因此,如果2x=内置A1c增益且G=内置指数增益,则ADC的读数为:

D1 = ADC(2x *G10*Vcal)

D2 = ADC(2x*G10*G10*Vcal)

为了达到最佳准确度,对每个值进行多次(可能是16次)平均采集可能是一个好主意。下一步是一些运算:

D2/D1 = (2x*G10*G10*Vcal)/(2x*G10*Vcal) = G10

D1/ (G10*Vcal) = (2x*G10*Vcal)/(G10*Vcal) = 2x

G = (G10)0.1

那还不算太糟,对吧?现在,如果我们想设置任何(大多数)所需的Y转换增益,我们只需计算一个增益累积区间,即:

T(µs) = log(Y/2x)/log(G)

请注意,如果这个计算结果T<1µs,我们就需要增加Y,以获得额外的时间(和增益),以便电容器“飞跨”和信号采集。

但是,还有另一个我们尚未涉及的误差源:U1输入偏移。尽管TLV9164的典型偏移仅为200µV,但最大值可达1.2mV。如果不进行校正,三个输入放大器的偏移可能达到3.6mV。这将导致我们的放大器的上增益范围失去价值。为了解决这个问题,我们需要另一个输入电压参考(Vzero)、更多的运算和另一个ADC转换来测量Voff偏移允许软件将其减去。我们将使用大量增益来获得足够的分辨率。理想情况下,Vzero应准确且稳定到<10µV,以充分利用9164出色的0.25µV/℃漂移规格。

设Vzero = 4.00mV

N = log(Vfs/(.008v * 2x))/log(G)

D3 = ADC(2x*GN*(Vzero + Voff))

Voff = D3/(2x*GN) – Vzero

就是这样。为了准确地将所有原始ADC结果转换为产生该结果的实际Vin输入:

Vin = (ADC(Vin)/(2x GN)) – Voff

但要避免GN>Vfs/(2x*Voff)。否则A1c和ADC可能会因放大偏移而进入饱和状态。此外,还可能会产生噪声。

漏电流难题源于这样一个事实:从U1c流经R1的负时间常数电流并不是C增益相位电荷的唯一来源。不幸的是,来自U2的X引脚和U1的非反相输入的漏电流也贡献了一部分有害电流。U1的贡献约为10pA,可以忽略不计,但U2的贡献可能大到足以造成问题。

亟待解决的问题是:HC4053开关的漏电流到底有多大?数据表提供的帮助出奇地少,答案似乎在百万分之一(pA到µA)的范围内。

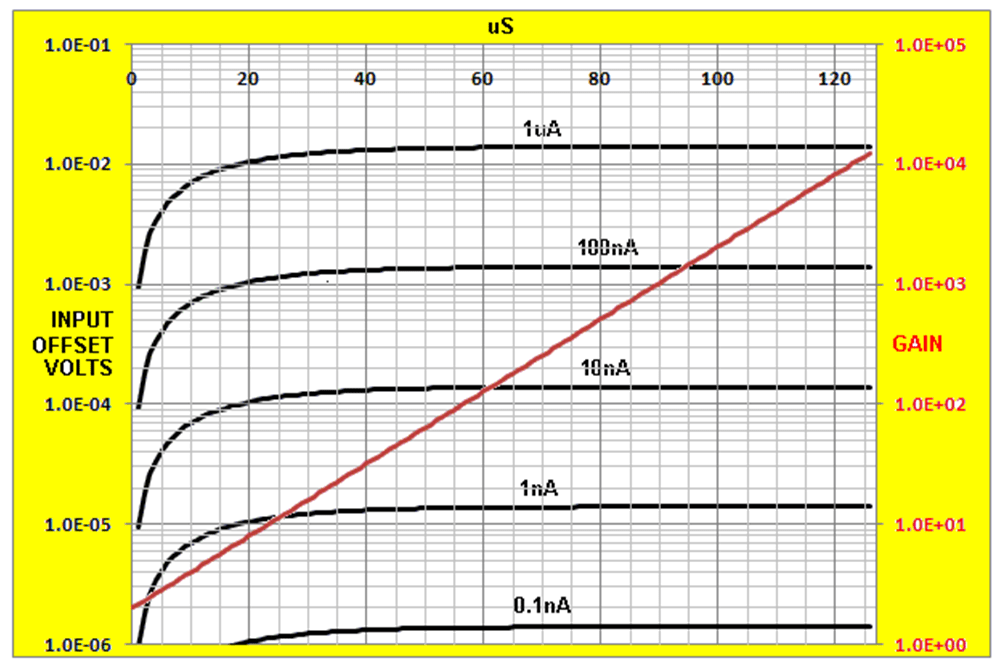

图2量化了一些可信的100pA至1µA的结果。

图2:输入参考电流-等效电压偏移。

我很感谢Christopher R.Paul和eldercosta慷慨、深刻、专业和有益的评论,这极大地促成了我写出这个设计实例。谢谢你们!

(原文刊登于EDN美国版,参考链接:In-situ software calibration of the flying capacitor PGINASH,由Ricardo Xie编译)

最前沿的电子设计资讯

最前沿的电子设计资讯