行业背景:目前3nm工艺的晶体管已经进入了消费市场,各家厂商也在持续推进2nm甚至1nm的工艺,根据行业规划,1nm级芯片预计将在2027年至2030年实现量产,例如台积电的1nm厂预计最快能够在2026年动工,2027年试产,2028年量产,英特尔的最新晶圆代工蓝图也显示,其10A(1nm制程)将于2027年底投入生产/开发。而在距1nm晶体管量产还很遥远的2024年,比1nm还小的亚纳米级晶体管已经出现了。

技术思路:在传统半导体制造工艺中,由于光刻分辨率的限制,将栅极长度减小到几纳米以下几乎是不可能的,韩国基础科学研究所(IBS)的研究团队利用一种天然的一维金属——二维半导体二硫化钼(MoS₂)的镜面孪晶边界(MTB),成功的突破了这一限制。

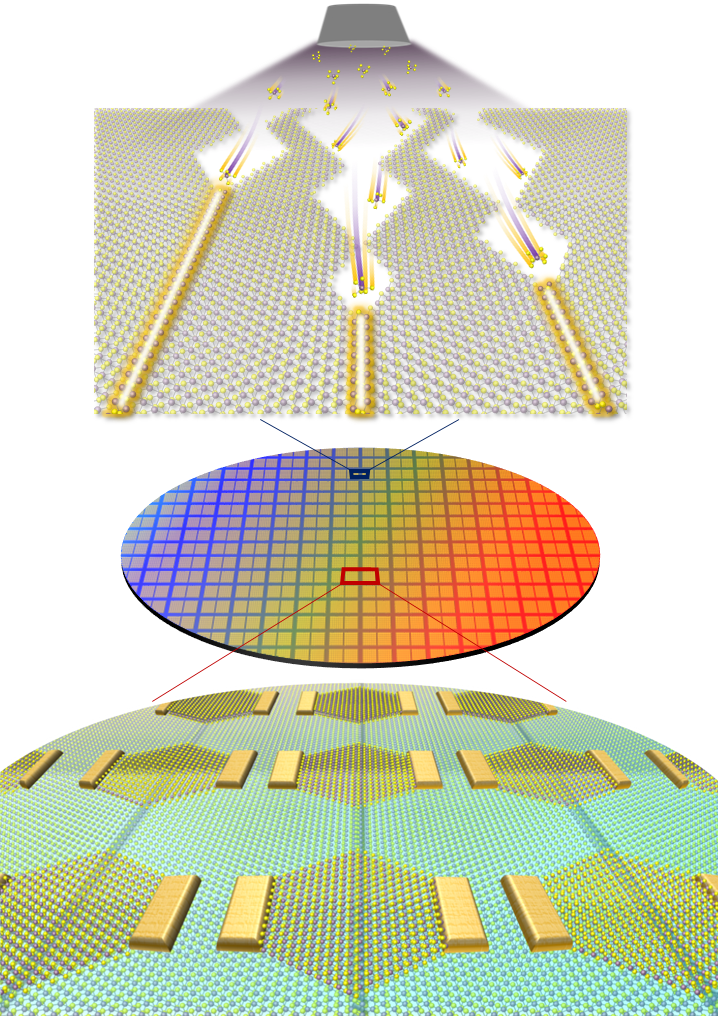

图5:基于该工艺的1D镜面孪晶边界金属及2D集成电路生长。(图片来源:韩国基础科学研究所)

该团队通过在原子水平上控制现有二维半导体的晶体结构,将其转化为一维MTB,实现了一维MTB金属相,这种金属相的宽度仅为0.4纳米,而由其制造的晶体管栅极长度仅为3.9纳米。

未来应用:这种新型材料工艺,可应用于超小型半导体工艺,有望成为未来开发各种低功耗、高性能电子器件的关键技术。

技术突破性:★★☆☆☆

商业化进展:★★☆☆☆

这样写得我以为还是中国科学家

这样写得我以为还是中国科学家 最前沿的电子设计资讯

最前沿的电子设计资讯