几十年来,计算架构一直依赖动态随机存取存储器(DRAM)作为主存储器,来为处理单元提供临时存储,以便检索数据和程序代码。DRAM的高速、高集成度、高性价比和出色的可靠性,促使DRAM技术在许多电子设备中得到了广泛应用。

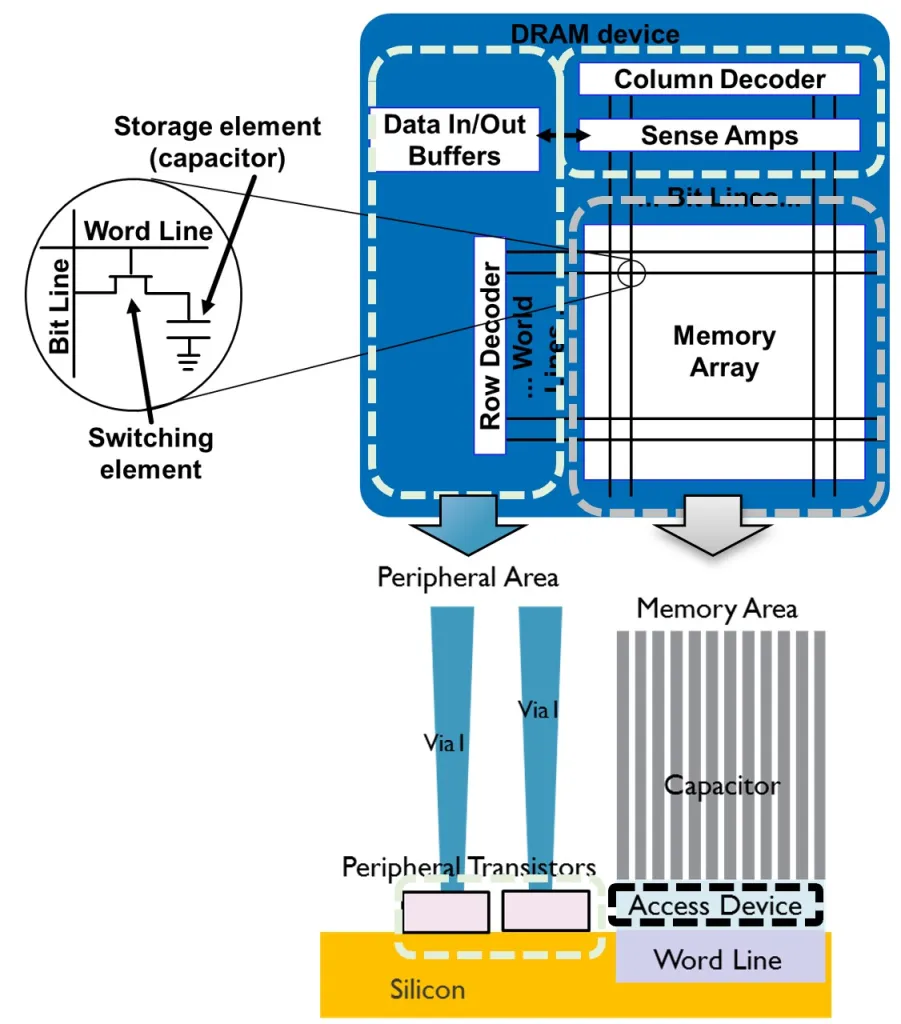

DRAM位单元(存储一位信息的元件)具有一种非常基本的结构,由一个电容器(1C)和一个集成在电容器附近的晶体管(1T)组成。电容器的作用是存储电荷,而晶体管则用于访问电容器,以读取存储的电荷量或存储新电荷。

1T-1C位单元排列成包含字线和位线的阵列,字线连接到晶体管的栅极,控制对电容器的访问。通过位线感测电容器上存储的电荷,可以读取内存的状态。

多年来,得益于位单元密度的持续扩展,存储器界推出了一代又一代的DRAM技术。当前的DRAM芯片属于“10纳米级”(表示为D1x、D1y、D1z、D1a……),其中内存单元阵列中有效区域的半间距从19纳米到10纳米不等。然而,人工智能驱动的对性能更好、容量更大的DRAM的需求正在推动研发10纳米以后的新技术。

这就需要在电容器、存取晶体管和位单元架构方面进行创新。此类创新的例子包括高纵横比柱状电容器,以及从马鞍形(基于FinFET)存取晶体管到垂直栅极架构的转变,还有从6F2到4F2单元设计的过渡(F是给定技术节点的最小特征尺寸)。

为了实现DRAM芯片的全部功能,除了存取晶体管之外,还需要几个其他晶体管,这些额外的晶体管起到地址解码器、感应放大器或输出缓冲器等作用。它们被称为DRAM的外围晶体管,传统上是紧靠DRAM存储器阵列区域制造的。

图1:DRAM芯片内部基于1T-1C的DRAM存储器阵列和DRAM外围区域。来源:imec

DRAM外围晶体管可分为三大类。第一类是常规逻辑晶体管:反复打开和关闭的数字开关。第二类是感应放大器——一种模拟类型的晶体管,可感测两位单元之间的电荷差异。微小的正向变化被放大为高电压(代表逻辑1),微小的负向变化被放大为零电压(代表逻辑0)。然后,这些逻辑值被存储在被称为行缓冲器的锁存器结构中。感应放大器通常位于靠近存储器阵列的位置,占用了DRAM芯片的很大一部分面积。第三类则是行解码器:将相对较高的偏置(通常约为3V)传递到存储器元件以支持写入操作的晶体管。

为了跟上存储器阵列节点到节点的改进,DRAM外围元器件也在缩小面积和提高性能方面进行了相应的改进,从长远来看,未来可能会出现更具颠覆性的解决方案,打破传统的“2D”DRAM芯片架构。有一种方案是在单独的晶圆上制造DRAM外围器件,然后将其粘合到包含有存储器阵列的晶圆上,就像在3D NAND中所采用的方法一样。

这三类外围晶体管各有其要求。常规逻辑晶体管必须具有良好的短沟道控制、高导通电流(Ion)和低关断电流(Ioff)。仅在这些特性上,它们与典型片上系统(SoC)中的逻辑晶体管非常相似,不过它们还需要启用多个阈值电压(Vth)以满足不同的设计要求。

另外两类则具有更多不同的特性,在典型的逻辑SoC中并不存在。模拟感应放大器需要良好的放大性能,这得益于低阈值电压(Vth)。此外,由于信号被放大,两个相邻感应放大器之间的不匹配必须尽可能小。因此,理想的感应放大器必须是一种具有良好模拟功能的可重复性极高的晶体管。

最后,行解码器是一种数字晶体管,与先进的逻辑节点相比,它需要非常厚的栅极氧化物来维持更高的偏压,这使得晶体管更可靠,但运行速度却较慢。

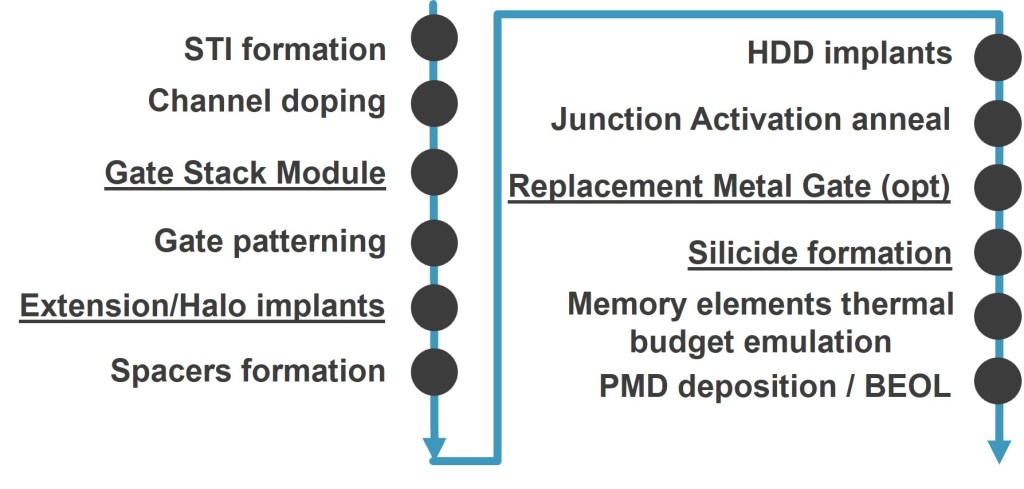

图2:以下是制造用于DRAM外围应用的晶体管所需的主要步骤,需要特定开发的关键模块已加下划线。来源:PSS

除了这些特定要求外,所有外围晶体管都还存在许多限制。其中的一个关键问题就是热稳定性。在当前的DRAM工艺流程中,DRAM存储器阵列紧靠外围,外围晶体管在DRAM存储器元件之前制造。因此,外围需要接受存储电容器、存取晶体管和存储器后端生产线制造过程中施加的若干种热处理。

因此,外围晶体管必须能够承受数小时的高达550-600°C的“DRAM存储器退火”温度。其次,还必须保持DRAM芯片的成本效益,这就促使集成商选择比逻辑流通常使用的工艺更简单的工艺解决方案。

为了降低成本,存储器行业也倾向于为各种外围晶体管采用单一的技术平台——尽管它们的需求各不相同。此外,对低漏电和低功耗的要求也更加严格,这对多种DRAM用例都很有利,尤其是移动用例。

所有这些规格要求使得不可能直接复制标准逻辑工艺流程,需要对特定模块进行优化,包括晶体管的栅极堆栈、源/漏结和源/漏金属触点。

(原文刊登于EDN美国版,参考链接:DRAM basics and its quest for thermal stability by optimizing peripheral transistors,由Ricardo Xie编译)

最前沿的电子设计资讯

最前沿的电子设计资讯