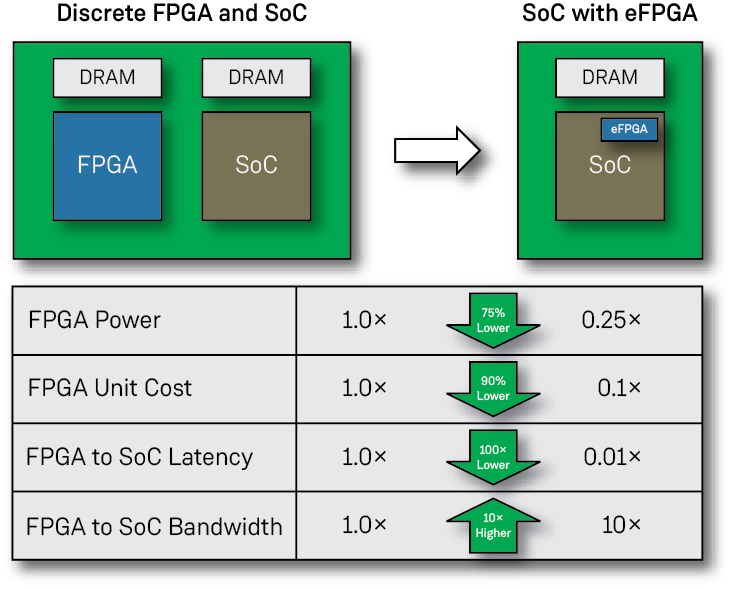

嵌入式FPGA (eFPGA)由于可为人工智能(AI)工作负载提供支持与灵活度,这项业务正开始掀起波澜。如今,在将FPGA功能整合至SoC设计时,eFPGA让设计人员能够定义FPGA逻辑的数量、内存以及DSP的处理能力。

图 1:相较于独立的FPGA 解决方案,eFPGA有助于使组件成本减少达90%,功耗降低高达 75%。(数据源:Achronix Semiconductor)

根据来自业界的两项最新消息显示,eFPGA能够添加新的产品功能,并针对特定的子市场或相邻市场量身打造SoC,这使其成为离散式FPGA的可行替代品。首先,QuickLogic宣布赢得了一份价值200万美元的合约,将为一家不具名的客户提供eFPGA IP。

几乎就在同一天,即 2021年9月1日,eFPGA IP供货商Achronix Semiconductor宣布与Signoff Semiconductors建立合作伙伴关系。Signoff Semiconductors 是一家位于印度班加罗尔的FPGA和ASIC设计服务供货商,可提供从规格、设计、验证、试产到量产(Spec. to Silicon)的FPGA和ASIC完整解决方案。因此,Signoff未来将可以直接使用Achronix的芯片、IP和支持服务。该设计服务公司并计划使用Achronix的FPGA和eFPGA IP技术,开发AI和深度学习加速器、推论解决方案以及边缘物联网(IoT)处理器。

早在今年3月,Achronix即宣布累积销售1,000万个采用客制ASIC出货的Speedcore eFPGA IP核心。Speedcore eFPGA IP使用类似于标准ASIC IP模块的设计流程,并针对5G无线基础设施、网络、运算储存以及先进驾驶辅助系统(ADAS)芯片进行了优化。

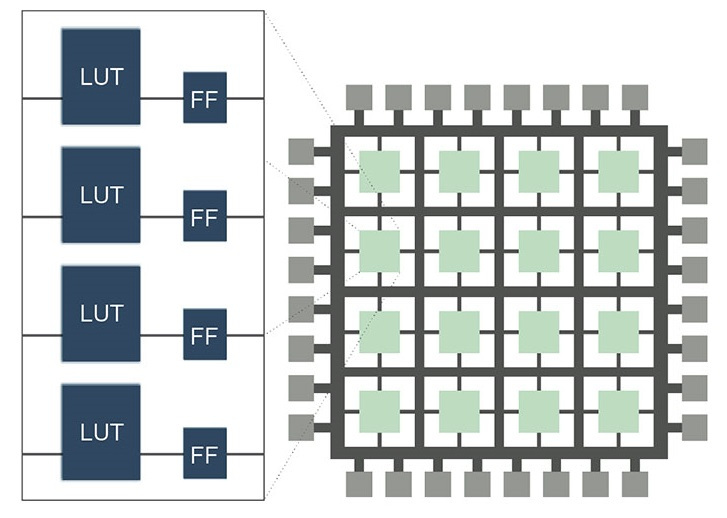

图2:ArcticPro 2 eFPGA架构使用分层布线机制,实现高运算量、电池供电或其他功耗敏感产品所需的最佳性能和功耗平衡。(数据源:QuickLogic)

正如 QuickLogic执行长Brian Faith所说的,实施eFPGA对于SoC设计来说风险非常低。其eFPGA IP已导入众多的SoC、MCU和离散式FPGA了。现在,当可编程逻辑固有的灵活性被视为极其适于加速 AI 应用时,离散式FPGA对于大量应用来说通常仍过于昂贵。因此,将eFPGA整合到SoC中可以节省BOM成本和功耗。

eFPGA固有的低功耗使其适用于广泛应用,包括手持和穿戴式装置以及IoT端点。对于以AI为中心的设计,eFPGA IP提供了整合固定功能区块(例如嵌入式RAM和可分解乘法累加(MAC)的选项,以便能有效地为神经网络和其他运算密集型AI与机器学习(Machine Learning;ML)应用实现硬件加速器。

图3:得力于eFPGA技术的进展,FPGA如今已能落实于穿戴式设计中。(数据源:QuickLogic)

为了确保芯片制造商能够将eFPGA IP无缝地整合于其SoC设计,QuickLogic已在格芯科技(Globalfoundries;GF)的22FDX平台上对其ArcticPro 2 eFPGA IP进行了验证。接下来,该公司将在三星(Samsung)的28nm FD-SOI制程上提供其ArcticPro 3 eFPGA IP。

(原文发表于ASPENCORE旗下EDN姐妹媒体Planet Analog,参考链接:Has the time for embedded FPGA (eFPGA) IP finally come?,编译:Susan Hong)

责编:Demi

最前沿的电子设计资讯

最前沿的电子设计资讯