三星电子(Samsung Electronics)宣布,该公司名为'3GAE'的3奈米(nm)环绕式闸极(gate-all-around;GAA)制程技术发展顺利,并已于今年4月推出其0.1版制程设计套件(PDK)。三星目前正于其3nm制程节点中导入GAA架构,以克服FinFET架构的实体微缩和性能限制。

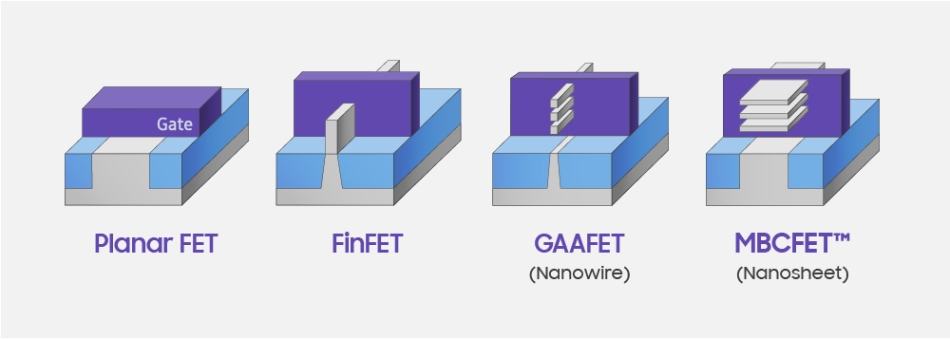

三星的晶圆厂高层指出,基于奈米线的传统GAA——也称为GAAFET,由于其有效通道宽度较小,因而需要更多的堆栈。另一方面,三星的多桥通道FET (MBCFET)技术采用奈米片架构以增强闸极控制,而这又使得每个堆栈获得更大电流。

图1:制程节点的演变标志着芯片制造方式的根本变化。(数据源:Samsung Electronics)

另一个关键区别在于:现有的FinFET结构必须分别地调节鳍片数量。MBCFET技术在此由于控制奈米片宽度,而提供了更大的设计灵活度。相较于5nm制程,三星声称,其首度采用MBCFET的3nm GAA制程节点面积最多可减少35%、性能提高30%,功耗也降低了50%。此外,3nm的逻辑良率能够达到与目前量产的4nm制程相当的程度。

三星的晶圆厂计划于2022年上半年开始量产其首批3nm芯片设计,并于2023年开始生产第二代的3nm芯片。三星技术蓝图的下一步是采用MBCFET架构的2nm制程节点;该技术目前处于开发的早期阶段,目标是在2025年实现大规模量产。

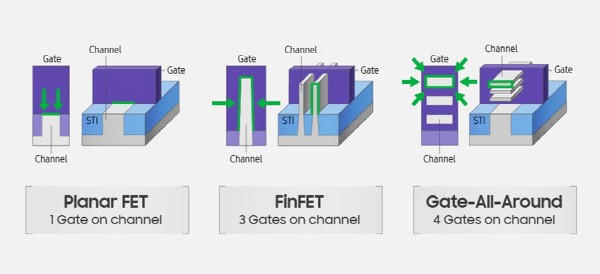

三星在晶圆代工方面的劲敌——台积电(TSMC)也声称其3nm制程节点的开发正顺利进展中,并计划在2022年下半年实现量产。值得注意的是,台积电的3nm制程节点采用的是FinFET晶体管结构,这意味着半导体公司将不需要采用新的EDA工具以及开发新IP。

然而,Samsung高层指出,MBCFET架构兼容于FinFET制程,这意味着工程师可以为这两种技术采用相同的制造技术和设备。而这也将有助于加速制程发展以及提升产能。

图2:三星领先台积电于3nm制程节点实施GAA技术。(数据源:Samsung Electronics)

全球晶圆龙头台积电则预计将从2nm处理器节点中开始采用GAA FET技术。因此,在市占率方面仍远落后于台积电的三星,尽管较台湾晶圆代工大厂领先一代导入GAA技术,但同时也承担了巨大的技术风险。

三星已经与合作伙伴共同开发原始设计工具,并在其2021年第五届年度三星晶圆代工论坛(Samsung Foundry Forum;SFF)中发布了转向基于GAA的3nm制程技术过渡计划。这家韩国巨擘一向以押重注于先进制程技术并挑战常规商业智慧而闻名。如今,观察三星的GAA技术赌注如何在与全球芯片代工龙头的大型晶圆厂业务竞争中取得成果,这将会十分有趣。

(原文发表于ASPENCORE旗下EDN美国版,参考连结:From FinFET to GAA: Samsung’s fab journey to 3 nm,by Majeed Ahmad;编译:Susan Hong)

责编:Demi

最前沿的电子设计资讯

最前沿的电子设计资讯