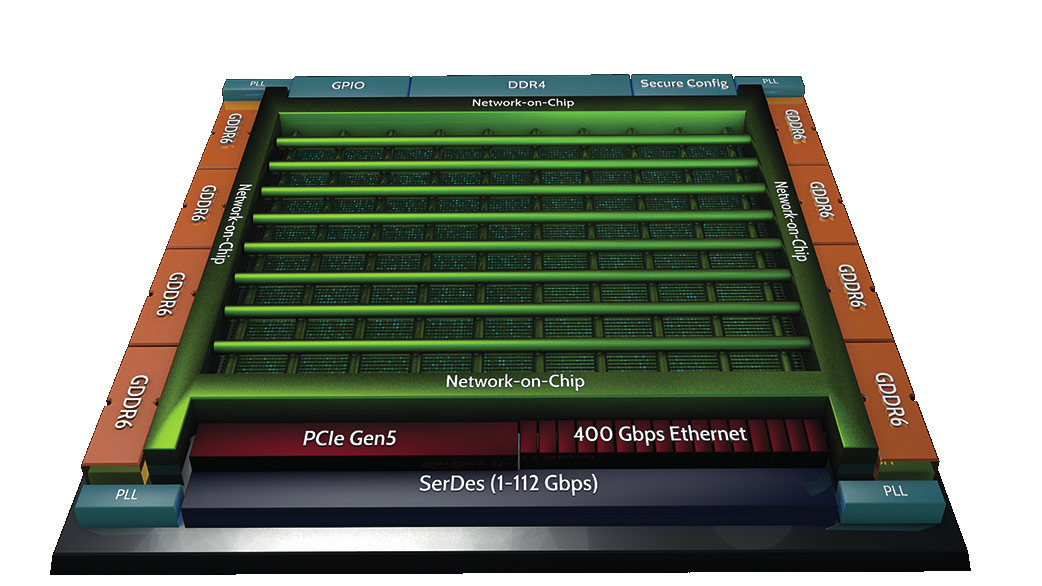

Achronix 最新基于台积电(TSMC)的7nm FinFET工艺的Speedster7t FPGA器件包含了革命性的新型二维片上网络(2D NoC)。2D NoC如同在FPGA可编程逻辑结构上运行的高速公路网络一样,为FPGA外部高速接口和内部可编程逻辑的数据传输提供了超高带宽。

如图1所示。

图1 Speedster 7t FPGA结构图

日益增长的数据加速需求对硬件平台提出了越来越高的要求,FPGA作为一种可编程可定制化的高性能硬件发挥着越来越重要的作用。 近年来高端FPGA用了越来越多的Hard IP去提升FPGA外围的数据传输带宽以及存储器带宽。但是在逻辑阵列密度不断提升的同时,通信性能的提升并没有那么明显,所以FPGA内部数据的交换越来越成为数据传输的瓶颈。

Achronix将此挑战视为一个开发全新架构的机会,以消除传统FPGA的设计挑战并提高系统性能。Achronix的解决方案是在传统FPGA布线结构之上,创新地使用了革命性的二维(2D)高速片上网络(NoC)。Speedster7t NoC连接到所有片上高速接口:400G以太网、PCIe Gen5、GDDR6和DDR4 / 5的多个端口。

Speedster 7t FPGA上的二维片上网络(2D NoC)不是由可编程逻辑搭建,而是固化的ASIC逻辑实现,固定运行频率为2GHz,NoC使用一系列高速的行和列网络通路在整个FPGA内部分发数据,从而在整个FPGA结构中以水平和垂直方式分发数据流量。NoC中的每一行或每一列都有两个256位的、单向的、行业标准的AXI通道,可以在每个方向上以512 Gbps(256bit x 2GHz)的传输带宽运行。总带宽高达27Tbps。

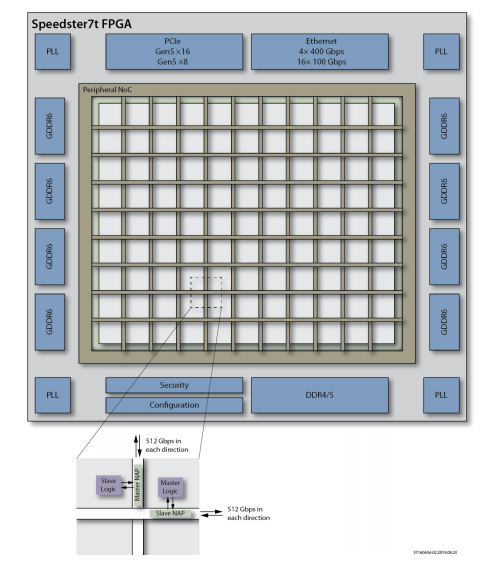

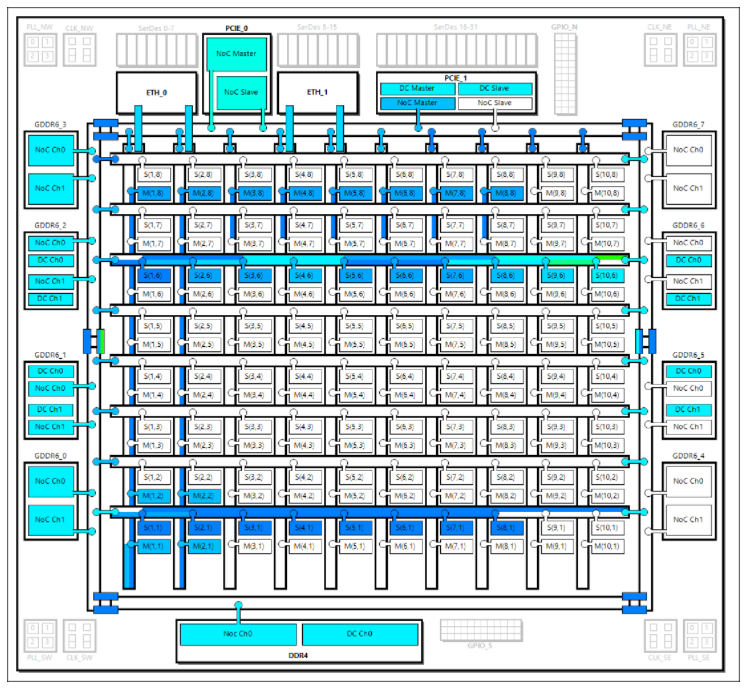

图2 Speedster 7t FPGA NoC 和 接入点NAP

在Speedster 7t的二维片上网络中,每个交叉节点都有两个网络接入点(NAP),如图2所示,一个是master,一个是slave。整个器件总共有160个这样的接入点,这样可以保证无论逻辑放置在器件的任何地方,工具都能找到最近的NAP,使之走上二维片上网络。数据在二维片上网络上传输也会有延迟,数据没经过一个网格的长度,延时会增加2~3个时钟周期,也就是1~1.5ns(时钟固定为2GHz,所以一个周期为0.5ns)。

由此可见,二维片上网络给高端FPGA带了巨大的性能优势,但是如何高效的利用这种优势给自己的应用带来实质性的性能提升至关重要。

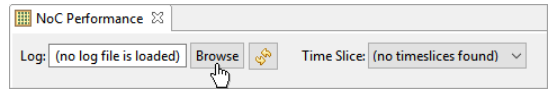

Achronix在新版ACE工具中提供一个可视化的NoC性能分析工具,只用导入simulation的log文件就可以直观的看到在不同的时间片,NoC上面的带宽占用情况,以便于设计者能更好地规划NAP的位置,均衡NoC的带宽利用,使其工作地更为高效。

工具使用起来非常简单,在ACE工具中点击 图标,就可以进入NoC Performance View的页面,在这个页面中点击Browse,导入仿真的log文件。

图标,就可以进入NoC Performance View的页面,在这个页面中点击Browse,导入仿真的log文件。

图3 导入仿真log文件

在NoC Performance View页面的右边有一个选项列表,可以显示不同条件下NoC占用情况。第一个选项是选择显示的协议,Flit还是AXI。第二个选项是选择显示哪种AXI Type。第三个选项是选择显示模式,Throughput模式还是Blockage模式。

图4 NoC Performance View选项

在Throughput模式下,绿色代表高吞吐量,浅蓝色代表中等吞吐量,深蓝色代表低吞吐量,如图5所示。

图5 NoC Performance View的throughput模式

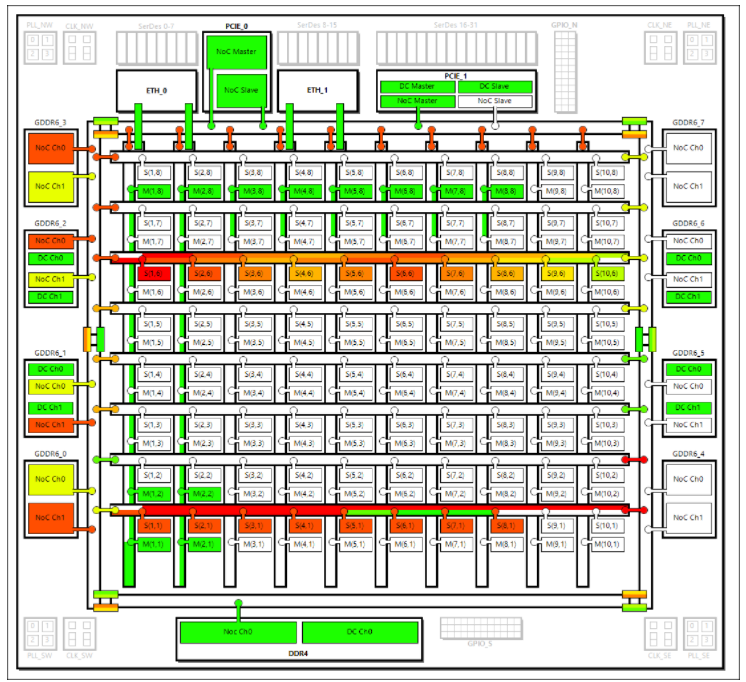

在Blockage模式下,红色代表拥塞程度最高,黄色代表拥塞程度中等,绿色代表拥塞程度低。如图6所示。

图5 NoC Performance View的Blockage模式

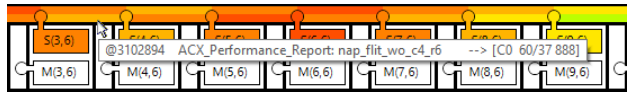

在图中用鼠标悬停在有颜色的部分,在悬浮的窗口中会显示图中对应的具体的log文件中的信息,包括时间点以及哪条会话。

图6 鼠标悬浮显示

所以通过NoC Performance View的工具,我们可以很直观的看到二维片上网络的使用情况,哪里利用率比较高,哪里利用率比较低,根据这个工具我们可以更容易的为逻辑指定更适合接入点NAP去接入到而且片上网络,从而使二维片上网络更高效的运行。

后面我们会继续深入了解Speedster 7t FPGA各种特性,并且会用一些例子来说明如何更高效的利用这些特性,敬请期待。 如需更多信息或者有任何疑问您可以通过Achronix公众号里联系方式联系我们,也可访问Achronix公司官方网站 http://www.achronix.com

参考文献:

Achronix网站:www.achronix.com

使用带有片上高速网络的FPGA的八大好处(WP020)

责编:Demi

最前沿的电子设计资讯

最前沿的电子设计资讯