随着市场需求将内存技术推向更高密度与效能、新材料、3D堆栈、高深宽比(HAR)蚀刻和极紫外光(EUV)微影,半导体设备业者正积极探索在进行生产前的三至五年可能会遭遇的挑战,以期为晶圆厂提供更具成本效益的解决方案。

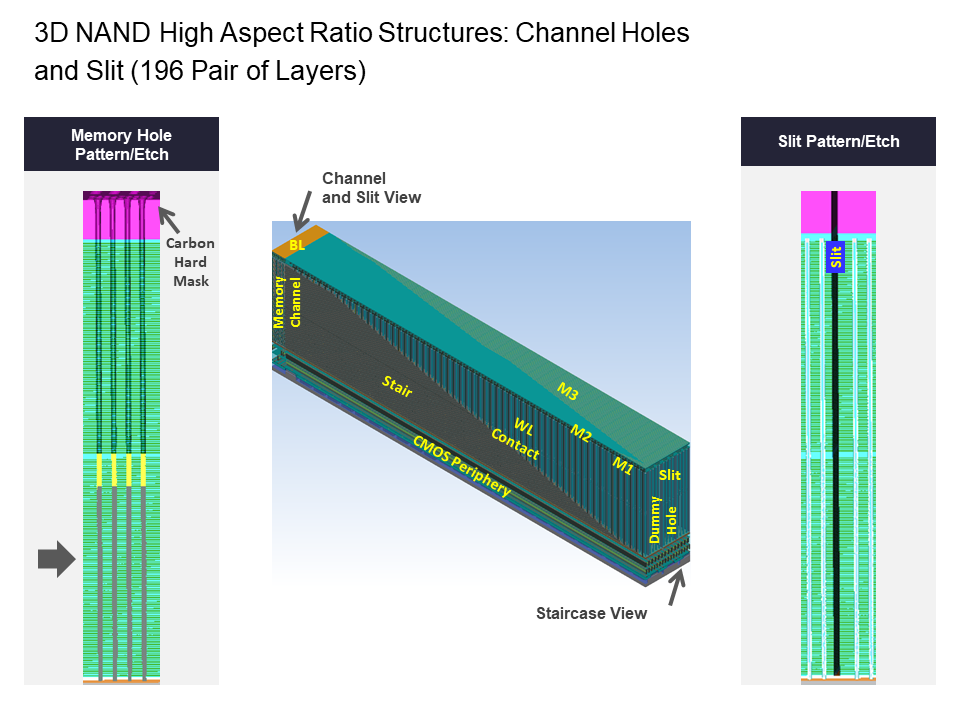

增加堆栈层数,是提升3D NAND闪存储存容量的一个途径,但此举会引起堆栈加高的重大挑战。尽管最明显的难题是结构稳定性,但增加层数代表得使用更深入的通道以存取每条字符线,与更加狭窄的狭缝沟槽(slit trenches)以阻绝和位线相连的信道(图1)。

图1:由于3D NAND堆栈超过128层,造成堆栈高度将近7µm,所需的通道孔和狭缝转变为具深高宽比(HAR)特征。

3D NAND制程始于氧化物与氮化物薄膜的交替沉积,接着做硬屏蔽沉积并在其上开孔,则垂直通道可被蚀刻出来。这就是高深宽比(HAR)蚀刻挑战的起点。随着业界朝向128层甚至更多层发展,堆栈深度接近7µm,硬屏蔽约为2~3µm,而通道孔深宽比则接近90至100。

之后,在挑战于大量层数中构成狭缝之前,建立出图1所示的“阶梯”结构。进行硬屏蔽层沉积、开孔图形化、并执行单一步骤的蚀刻以形成穿过所有层的狭缝。最后,必须去除氮化物层,并产生钨字符线。

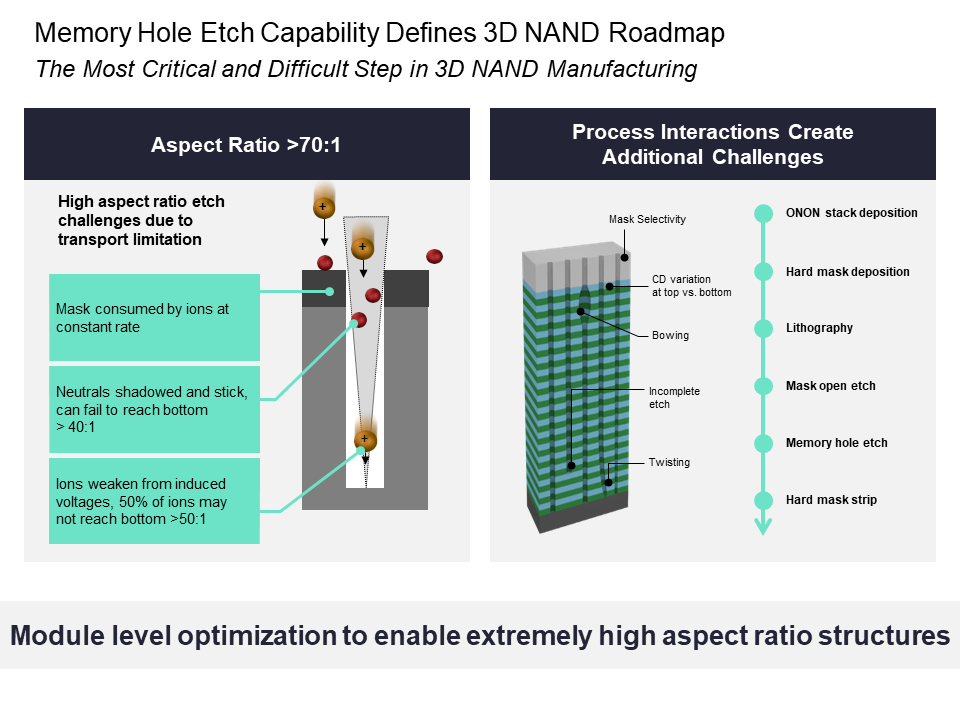

为了让高深宽比结构的反应离子蚀刻(RIE)发挥作用,离子和中性物质之间必须有协同作用。然而,在处理高深宽比结构时,协同作用会因受到数项机制所阻碍而容易耗失。

首先,高压可能导致离子消散于电浆鞘中,并散布离子能量或通常为非等向性的角度分布。所以,离子会错过孔洞,或者以更大的角度入射法线,撞击特征的顶部或侧壁。这种离子“遮蔽”造成离子-中性通量比偏离协同作用(图2)。

图2:离子与中子遮蔽及深长宽比取决与传导,就如同离子角度分布,扮演着造成例如CD变化、不完全蚀刻、弯曲和扭曲等缺点的要角。

为了在高深宽的结构特征下将离子往下推,可以将离子能量提高,但此举会增加光罩消耗,反而又需要将光罩加厚或者改良硬屏蔽材料。

除此之外,还有离子轰击通道的侧壁、会引起通道某些地方的关键尺寸(Critical dimension,CD) 大于所需尺寸的问题。当这个通道“弯曲”(图2) 变得太大时,可能导致两个孔洞连在一起。而另一个重大问题是沿着孔洞的“扭曲”,此现象系由起于RF电浆系统中高阶失真之电荷效应导致离子角度分布有些微的改变。

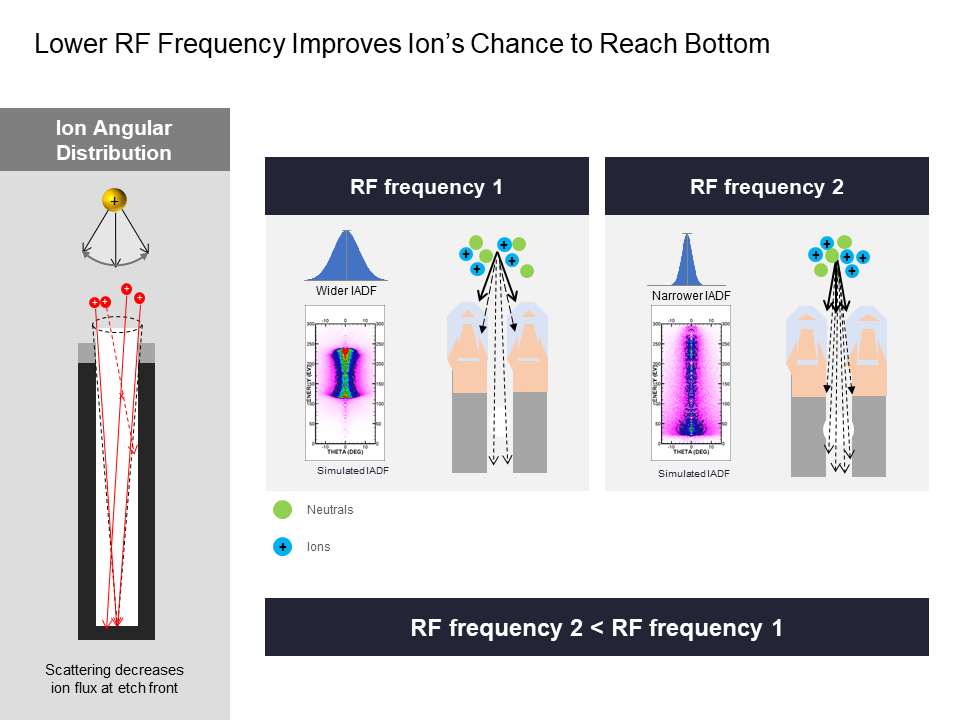

仔细观察电浆系统就能找出解决方案,尤其是RF子系统。事实证明,只要降低频率,使得加速通过高电压鞘的离子传送时间接近半周期,此时,施加的RF功率会得到离子能量。较低的频率与较高的离子能量峰值会导致较小的离子角度散布,令离子更可能到达HAR特征峰值最大化的底部(图3)。

图3:降低电浆频率会减少离子的散布,提高其到达高深宽比特征底部的可能性。

所以,硬件设计中的重大努力集中在采取较低频率、较高功率以及较少的工作周期上。尽管改变了硬件设计,但要将一个深度达6.9µm的通道孔及多达128层或更多层的氧化物-氮化物-氧化物-氮化物(ONON)进行蚀刻,仍然是非常困难的。

为此,Lam Research正在尝试不同的方法以达到所需的蚀刻深度,并已制定出一套方法,当中先以设定好例如5µm的蚀刻来蚀刻出通道孔,接着保护内垫沉淀在侧壁上,以避免过度的侧面蚀刻。在后续步骤中,一直不停将通道孔向下蚀刻至6.9µm的程度。

增加内垫能额外增多1µm的蚀刻而不会加大整个结构的关键尺寸。尽管这个制程仍需大幅优化,但测试展示出一条大有可为、能够蚀刻出较小且较深孔洞的途径。

逻辑与内存的图形化,可能是芯片制造商成本裁减与效能改善优先次序清单中的最首要的项目。目前,都是要以最小的变化来将线宽缩减为较小的结构。边缘放置误差(Edge placement error,EPE)可测量出这项变化。

举例而言,对齐孔洞会面临到数个变化性挑战,例如线边缘粗糙度、曝光机覆盖误差以及关键尺寸变化,包括EUV曝光随机误差所引起的局部关键尺寸变化。组件的设计通常受限于变化的极端程度而非变化的方法。处理这些变化以调和最坏的情况方案,可能会占用逻辑后端中50%的区域,并大幅增加制造成本。

透过制程间协作优化是控制变化的一个办法,其通常代表着在蚀刻期间针对微影中的误差进行补偿。要让协作优化发挥作用,蚀刻工具必须有合适的可调性,方能将跨晶圆与晶圆到晶圆的蚀刻行为控制得更好。

因为在晶圆上总是会发现不同的电浆条件、气体分布及温度控制上的种种差异,换言之,建立制程的可调性,则可以补偿不仅是腔中、还有来自微影的变化。

因此,在晶圆座和晶圆上建立可调温度区,是控制温度与蚀刻率的一种方法。过去十多年间,晶圆座已经从2000年代初期的单区装置进化成双区,然后是放射状多区,而近来,Lam Research的Hydra Uniformity系统中更发展出非放射状多区。

在DRAM、PCRAM以及某种程度的3D NAND中为使用主流的多重图形,不断面对来自关键尺寸变化的挑战。图形化方案增加了制程步骤数,而这种增加代表有更大量的变化源。

在自校准四重图形(SAQP)中,来自微影、沉淀和蚀刻的变化会导致三种不同的关键尺寸。举例来说,在间隔层蚀刻期间,可能会有挖入底层的情况。这类的变化导致所谓的“间距偏差”,其对多重图形化而言已成为重大难题。

如果,间隔层能在蚀刻过后成为正方形,就能克服这道难关。这就是Lam Research利用新金属氧化物材料的创新使用而达成的成果。利用非常微小的挖入,该方案将SAQP流程从8层简化为5层。

EUV微影被预期很快会成为逻辑与DRAM的主流,也需要仔细考虑因此制程而来的变化。EUV 微影使用高能量光子,而制程容易受到无规则或随机变化所影响。

随机行为会对孔洞造成局部关键尺寸变化。在线与空间情况下,来自例如线边缘粗糙度(Line edge roughness,LER)和线宽度粗糙度之缺点的影响,是十分严重的。

例如,随机效应限制住导孔的产量,且规模随着导孔的关键尺寸而不良。即使是一台250W曝光机,其在小导孔关键尺寸处的功率也可能不足,因此需要进一步材料和后处理的创新,以控制因功率增加而攀升的EUV成本。

过去数年间,Lam Research在原子层蚀刻(ALE)上的成就已然证明了克服此挑战的制程能力。原子层蚀刻包括在修改表面以及后续蚀刻期间的自限制步骤。当重复进行此作业多个周期后,原子层蚀刻很显著地平缓了高频时的粗糙度特性。

在与合作伙伴所进行的测试中,Lam Research已测量过这项效应,结果显示EUV透过56%的局部关键尺寸均匀度(Local critical dimension uniformity,LCDU)改善可超过3nm变为1.3nm,对于某些芯片制造商而言,更可能降低到1nm。

局部关键尺寸均匀度的提升对上游具有重要的影响:对于EUV曝光机而言,因为利用Lam Research的蚀刻和沉淀制程,所以能减轻随机诱发变化,所以允许使用较少的能源。这项微影-蚀刻的偕同优化能藉由两个成因的其中之一来降低EUV成本。

现在,Lam Research 已经针对高深宽比结构以及原子层制程开发出模块级解决方案,以便在内存技术蓝图上处理边缘放置误差。然而,想要沿着技术蓝图自信前进,仪器供货商、材料供货商和芯片制造商必须在制程开发的早期阶段即携手合作,以具成本效益和时间效益的方式,满足内存技术蓝图的所有要求。

本文由Lam Research供稿并同步刊登于《电子工程专辑》杂志2021年11月号

责编:Demi

最前沿的电子设计资讯

最前沿的电子设计资讯