适当的控制环路相位和增益测量应由拥有(昂贵的)设备和相应经验的工厂专家进行。如果缺少其中一个或两个都没有,则还有另一种选择。

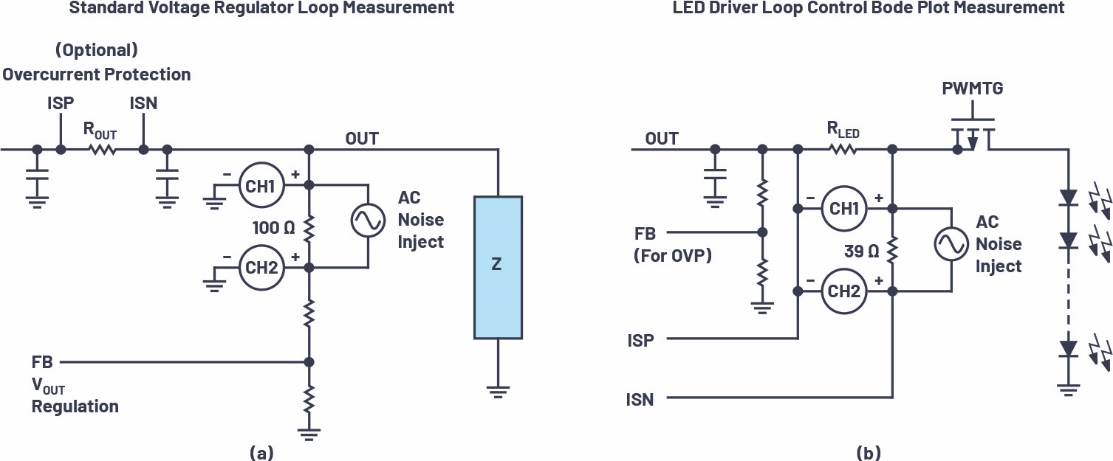

闭环增益和相位图是用于确定开关调节器控制环路稳定性的常用工具。正确完成增益和相位测量需熟悉高级网络分析仪。测量包括断开控制环路、注入噪声,以及测量一定频率范围内的增益和相位(见图1)。这种测量控制环路的做法很少应用于LED驱动器。

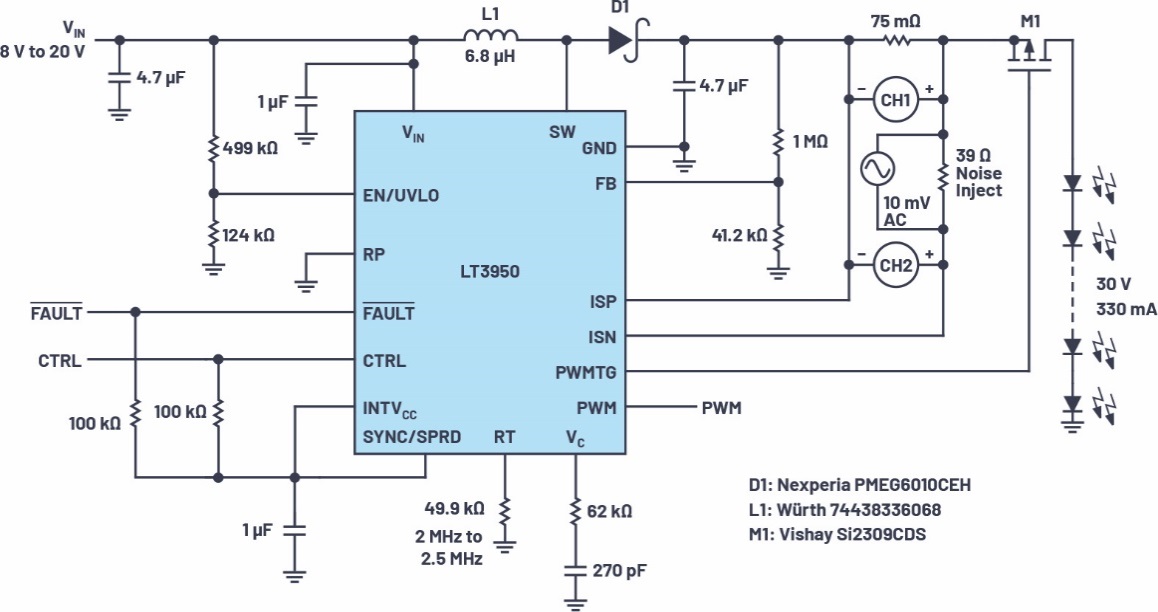

LED驱动器控制环路相位和增益测量需要采用一种不同的方法(见图1)——从典型的电阻分压路径到GND电压调节器注入和测量点的偏差。在这两种情况下,台式控制环路相位和增益测量是保证稳定性的最佳方法,但并非每个工程师都有所需的设备和经验丰富的工厂应用程序团队加持。工程师们该怎么办呢?

一种选择是构建LED驱动器,查看它瞬态的响应。瞬态响应观察需要应用板和更常见的台式设备。瞬态分析的结果缺乏波德图基于频率的增益和相位数据——可用于保证稳定性,也可作为一般控制环路稳定性和速度的指示器。

大信号瞬态可用于检查绝对偏差和系统响应时间。瞬态扰动的形状表示相位或增益裕量,因此可用于了解一般环路稳定性。例如,临界阻尼响应可能表示45°至60°的相位裕度。或者,瞬态期间的大尖峰可能表示需要更多的COUT或更快的环路。较长的建立时间可能表示需要加快环路的带宽(和交越频率)。这些相对简单的系统检查能够在运行中描绘开关调节器的控制环路,但增益和相位波德图需要进行更深入的分析。

LTspice®仿真可用在组装或生产电路之前生成开关调节器输出的瞬变波形和波德图。这有助于大致了解控制环路的稳定性,以便开始选择补偿元件和确定输出电容大小。LTspice的使用过程基于1975年Middlebrook的最初建议(请参阅“LTspice:生成SMPS波德图的基本步骤”)。目前,Middlebrook的方法中列出的实际信号注入位置并不常用,但经过多年的调整,得出了如图1a所示的常用注入位置。

此外,带有高边检测电阻和复杂交流电阻LED负载的LED驱动器,在反馈路径中应有一个不同于目前的注入点或Middlebrook最初建议的注入点,LTspice此前未予说明。这里介绍的方法是展示如何在LTspice和实验室中生成LED驱动器电流测量反馈环路波德图。

标准开关调节器控制环路波德图产生三个关键测量值,用于确定稳定性和速度:

一般认为,稳定的系统需要45°至60°的相位裕度,而为保证环路稳定性则需要–10 dB的增益裕量。交越频率与一般环路速度有关。图1显示了使用网络分析仪进行这些测量的设置。

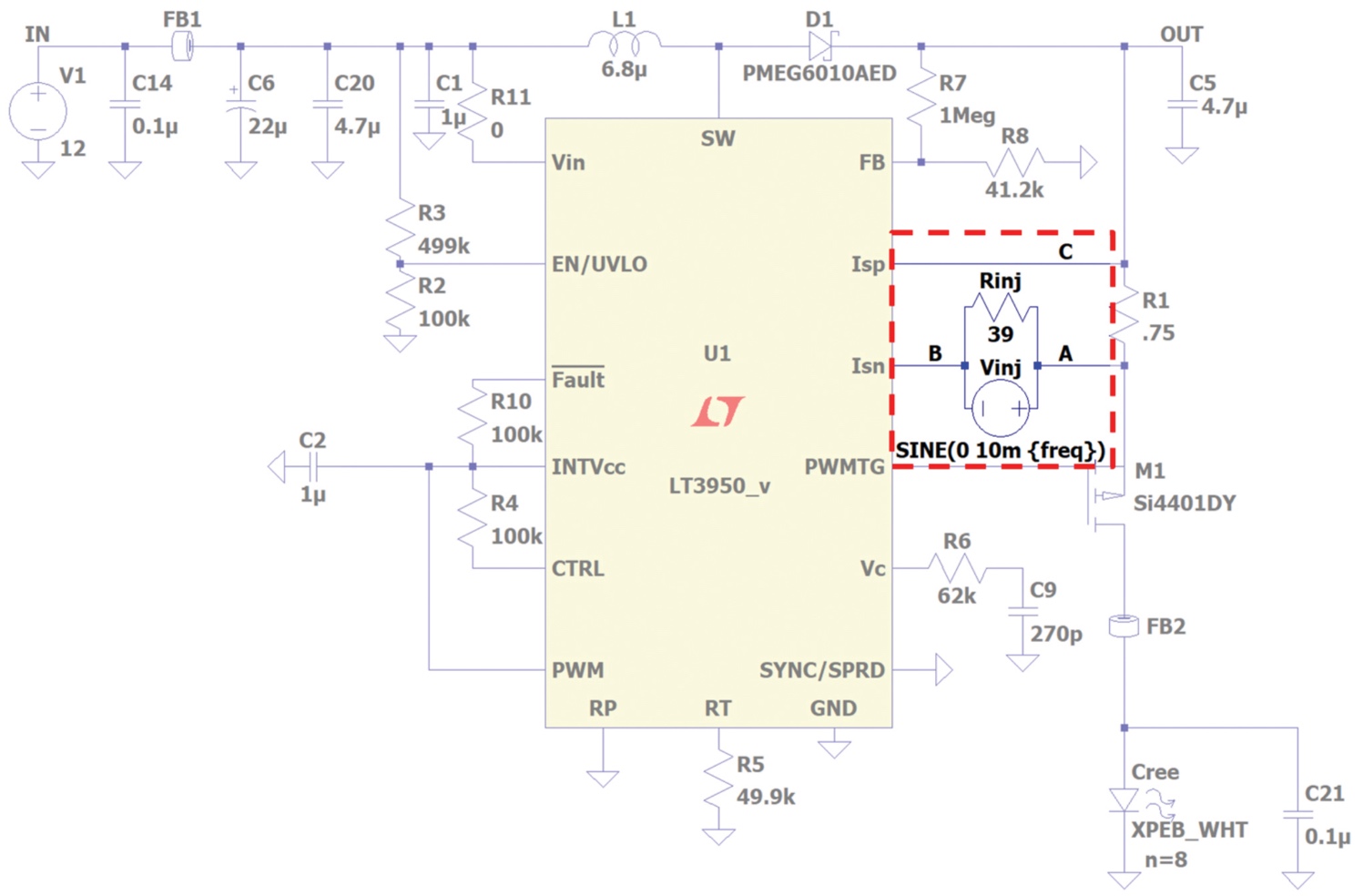

LTspice模拟可用在LED的控制环路中创建类似的注入和测量。图2显示了一个LED驱动器(LT3950),给定频率(f)的理想正弦波直接注入到负感测线(ISN)的反馈路径中。测量点A、B和C用于计算注入频率(f)下的增益(dB)和相位(°)。为了绘制整个控制环路的波德图,必须在大频率扫描范围内重复该测量,并在fSW/2(转换器开关频率的一半)处停止。

图1.开关调节器控制环路波德图测量,带有网络分析仪,用于(a)电压调节器和(b)LED驱动器。为了进行测量,控制环路断开,正弦波扰动进入高阻抗路径,同时测量由此产生的控制环路增益和相位,使设计人员能够量化环路的稳定性。

图2.LT3950 DC2788A演示电路LED驱动器LTspice模型,带控制环路噪声注入和测量点

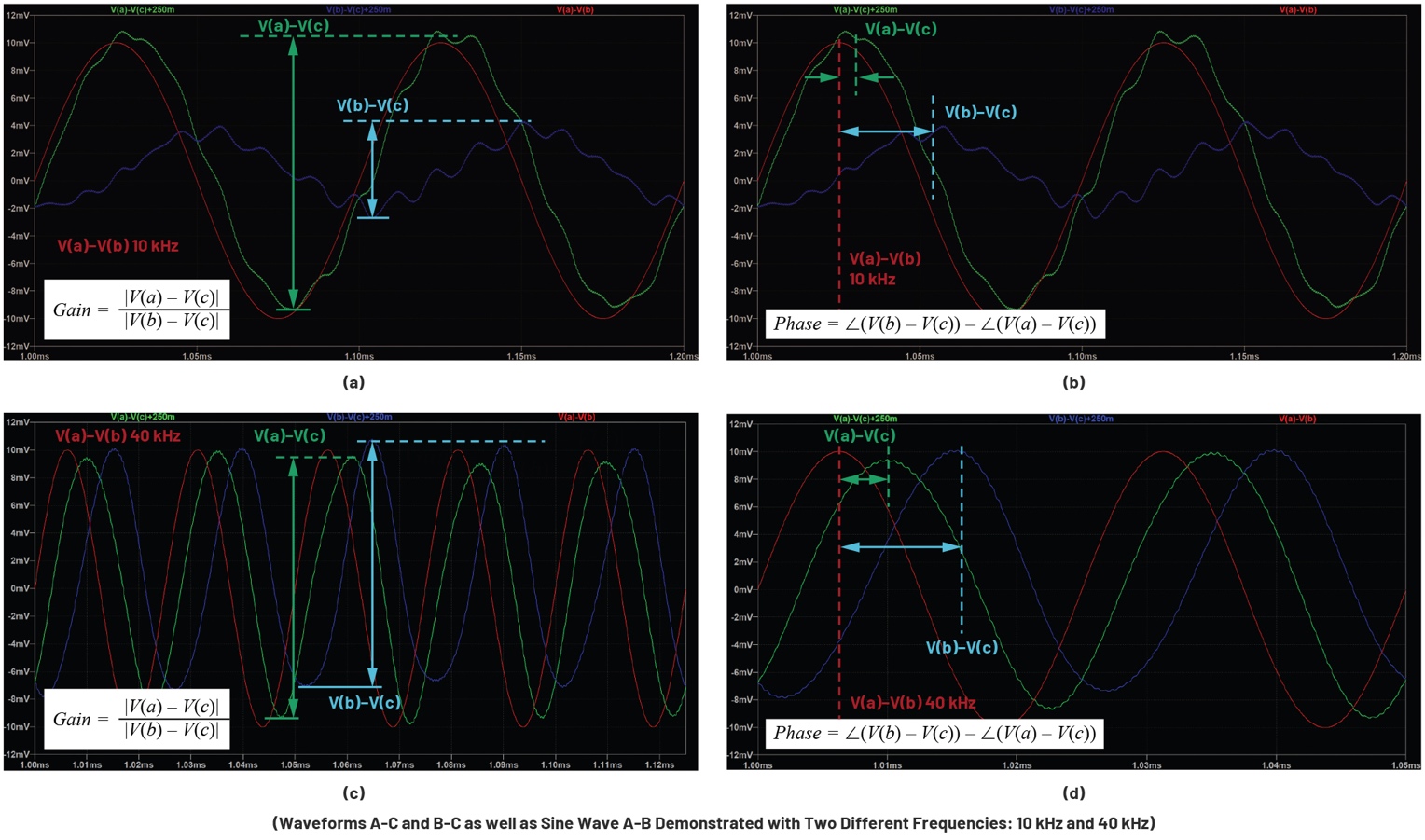

图2中点A、点B和点C的测量值决定了注入频率(f)下控制环路的增益和相位。不同的注入频率产生不同的增益和相位。总之,为了解它的工作原理,可以设置注入频率,并测量A-C和B-C的增益和相位。这会产生控制环路波德图的单个频率点。图3a和3b显示了10 kHz±10 mV AC注入的增益和相位。图3c和3d显示了40 kHz±10 mV AC注入的增益和相位。

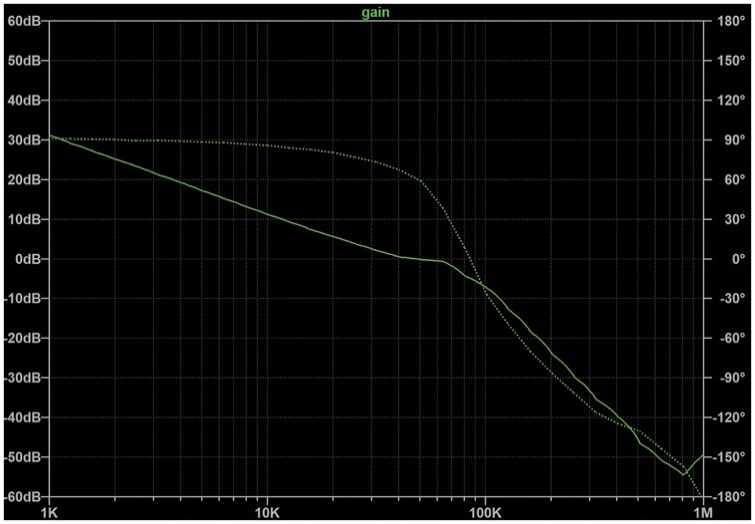

频率扫描以及B-C和A-C之间的增益和相位测量生成整个闭环波德图。如摘要中所述,这通常是在工作台上使用一台昂贵的网络分析仪来完成的。在LTspice中也可进行这种扫描,如图4所示。通过与使用网络分析仪的台式测试结果进行比较,证实这些结果(见图8)。

图3.图2中点A、点B和点C的测量值决定了注入频率(f)下控制环路的增益和相位。不同的注入频率产生不同的增益和相位。图3a和3b显示了10 kHz±10 mV AC注入的增益和相位。图3c和3d显示了40 kHz±10 mV AC注入的增益和相位。频率扫描以及B-C和A-C之间的增益和相位测量生成闭环波德图。

图4.用LTspice中的LT3950进行波德图测量,显示增益(实线)和相位(虚线)

要在LTspice中为控制环路创建全部波德图、增益和相位的图形扫描,请按照下列步骤操作。

在LTspice中,插入±10 mV AC注入电压源和注入电阻,并标记节点A,B和C,如图2所示。交流电压源值SINE(0 10m {Freq})设置10 mV峰值并扫描频率。用户可以使用1 mV至20 mV的正弦峰值来进行计算。注意:许多LED驱动器的感应电压分别为250 mV和100 mV。较高的注入噪声会产生LED电流调节误差。

在原理图上将测量描述作为.sp(SPICE)指令插入。这些指令执行傅里叶变换公式,并以dB和相位计算LED驱动器的复数开环增益和相位。

各指令如下:

还需要一些小的指令。首先,为进行正确的测量,电路必须处于模拟的稳定状态(启动后)。调整t0,或测量的开始时间和停止时间。通过模拟和观察启动时间来估算或得出开始时间。达到稳定状态后,停止时间定为10/freq,即10个周期,通过对每个频率的10个周期求平均值来减少误差。

各指令如下:

.step命令设置执行分析的频率分辨率和范围。本例中,使用每倍频程3点的分辨率,模拟1 kHz到1 MHz。波德图测量可以精准到fSW/2,频率上限设置为系统开关频率的一半。显然,点越多,分辨率越高,仿真时间越长。每倍频程3点是最低的分辨率,但以最小分辨率运行仿真可节省一些时间。从总体设计周期看,5分钟的仿真比设计、组装和测试印刷电路板快几个数量级。基于这点,以更高的分辨率运行,例如每倍频程5点或以上,生成更完整且更容易查看的结果。

这会比较直观,但LTspice需要多个步骤制作波德图。第一步是运行仿真,暂不生成图,只显示正常范围的电压和电流测量值。按照以下步骤生成波德图。

右键单击原理图窗口,打开“SPICE错误日志” ,选择Plot .step’ed .meas data。从“画图设置目录”中选择“可见曲线”,然后选择“增益”来绘制数据。或者,可通过单击文件,然后选择将数据导出为文本,产生波德数据的CSV文件,导出测量数据,

在仿真之后,使用网络分析仪进行波德图确认。

控制环路的仿真不像真实的那样可靠,它不能完全保证环路的稳定性和裕度。在设计过程的某个阶段,应在实验室使用网络分析仪工具验证控制环路。

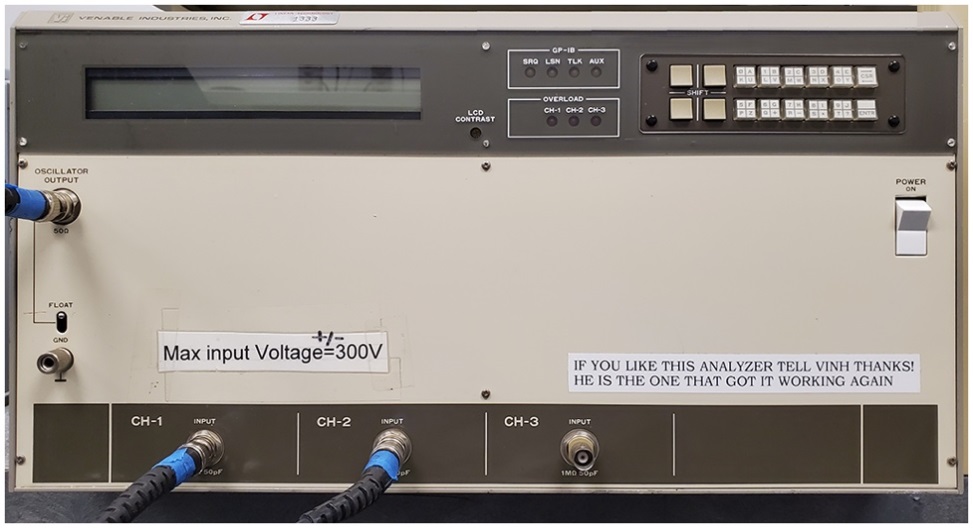

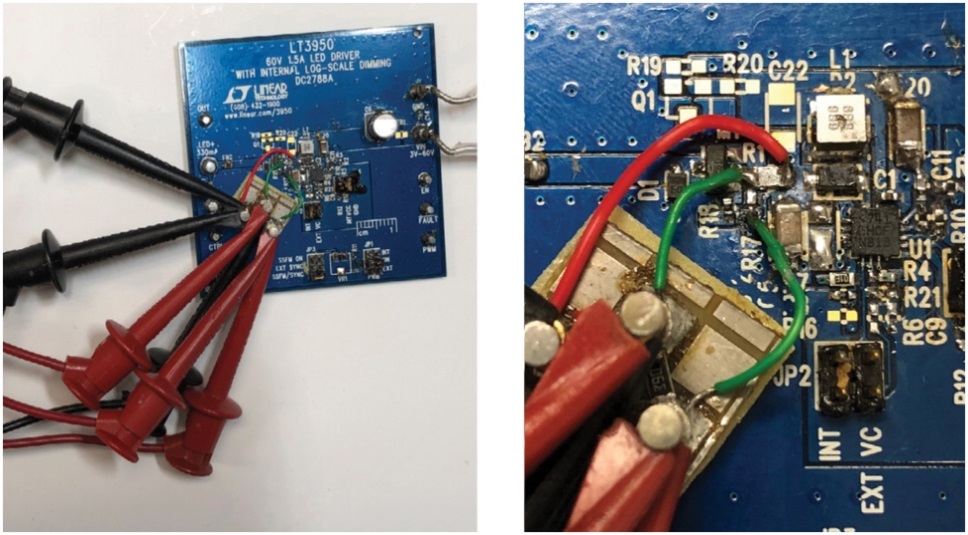

LTspice中生成的波德图可以与网络分析仪的波德图测量结果比较。类似放真,通过将噪声注入反馈环路并测量和处理A-B和A-C的增益和相位来捕获实际的环路测量结果。测量设置示意图和照片如图5至图7所示。

图5.网络分析仪的LED驱动器控制环路波德图测量设置

图6.Venable System Model 5060A老式网络分析仪,用于高边浮动噪声注入和LED驱动器的测量

图7.LT3950 LED驱动器上的噪声注入和测量点

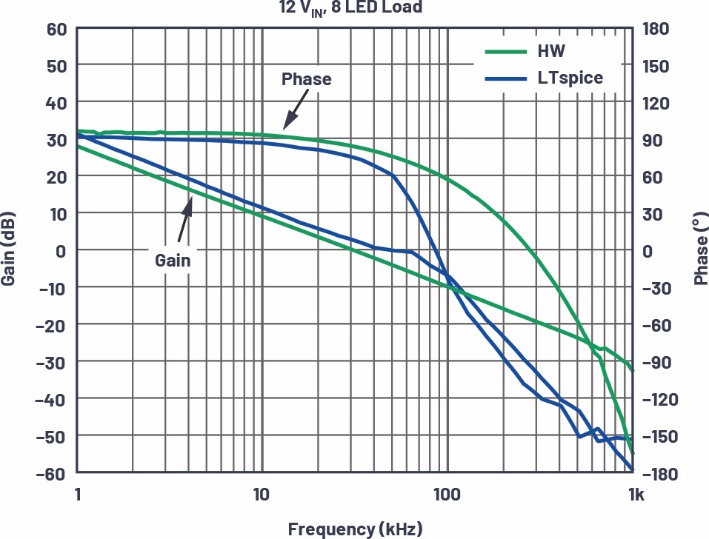

图8.DC2788A演示电路板上的LT3950 LED驱动器的波德图。通过LTspice模拟生成的图(蓝线)与使用网络分析仪生成的图(绿线)相关性强。

表1.LT3950 LED驱动器的波德图测量数据比较,LTspice vs.网络分析仪

Ltspice仿真结果显示与网络分析仪数据的强相关性,证明LTspice是LED驱动器设计中的有效工具——产生大概的参考,帮助工程师缩小元件选择范围。较低频率下的增益和相位与硬件非常相近,较高频率下的仿真数据和硬件数据之间的差异更大。这可能代表了对高频极点、零点、寄生电感、电容和等效串联电阻建模的挑战。

LTspice建模用于测量控制环路增益和相位,生成LED驱动器的波德图。Ltspice仿真数据的精确度取决于所使用的SPICE模型的精确度,精确地建模每个元件以解决现实情况会增加仿真时间。就LED驱动器设计而言,没有完善的元件建模,LTspice数据也可用于相对较快地缩小元件范围并预测总体电路性能。仿真有助于在过渡到硬件设计之前指导设计工程师,节省总体设计时间。粗略地选择元件后,使用内置板和网络分析仪的测量可以确认或对比仿真结果,作为开发期间硬件验证的一种手段。

1 Gabino Alonso.“LTspice:生成SMPS波德图的基本步骤。Analog Devices, Inc.

Keith Szolusha是ADI公司应用总监,工作地点位于美国加利福尼亚州圣克拉拉。自2000年起,Keith任职于BBI Power Products Group,重点关注升压、降压-升压和LED驱动器产品,同时还管理电源产品部的EMI室。他毕业于马萨诸塞州剑桥市麻省理工学院(MIT),1997年获电气工程学士学位,1998年获电气工程硕士学位,专攻技术写作。联系方式:keith.szolusha@analog.com.

Brandon Nghe是Analog Devices的应用工程师。2020年获得加利福尼亚理工州立大学电气工程硕士学位。Brandon负责为汽车应用设计和测试升压、降压-升压和LED驱动器的低电磁干扰DC/DC变换器。联系方式:brandon.nghe@analog.com.

(原文标题:How to Use LTspice to Produce Bode Plots for LED Drivers)

最前沿的电子设计资讯

最前沿的电子设计资讯