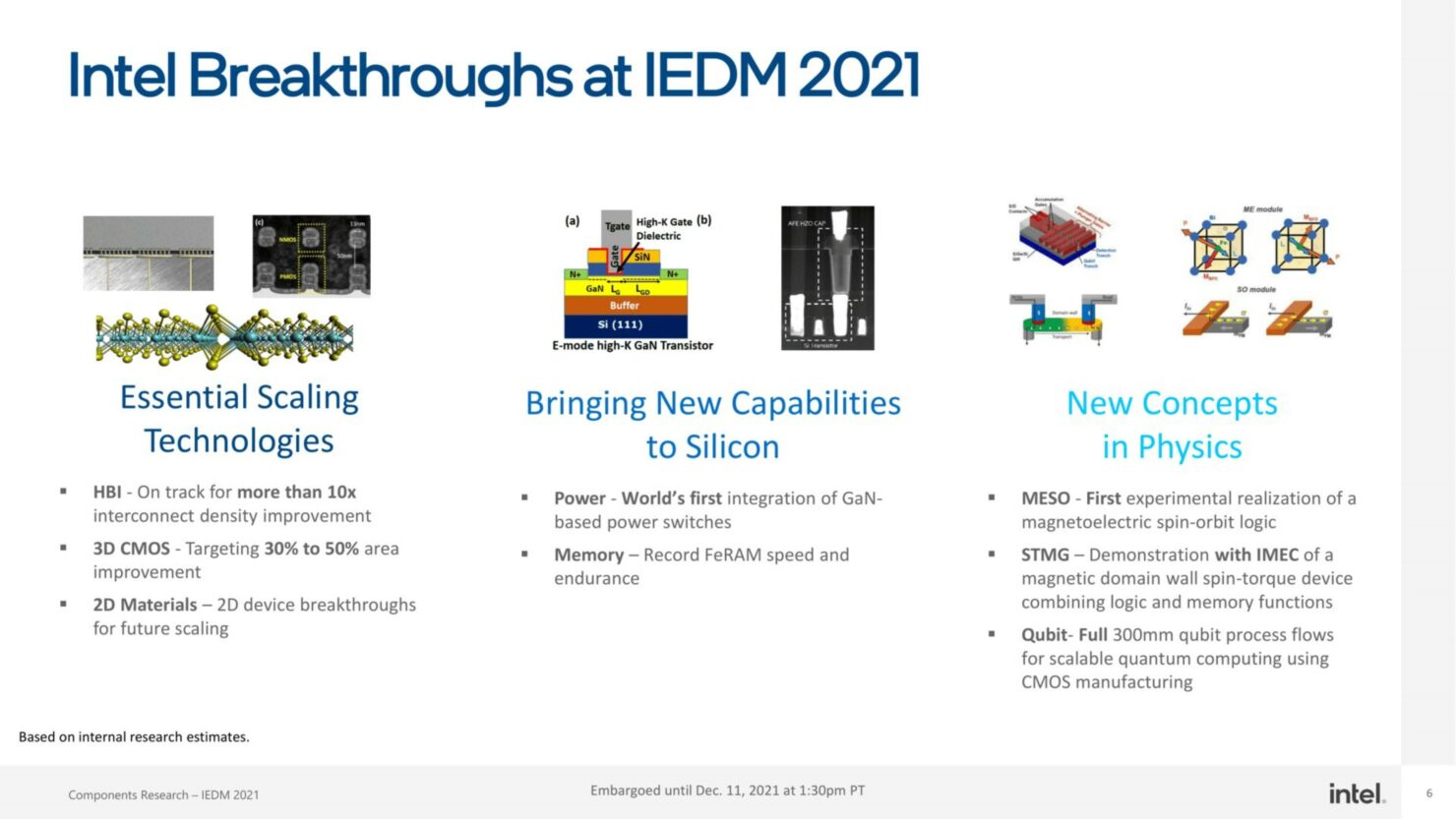

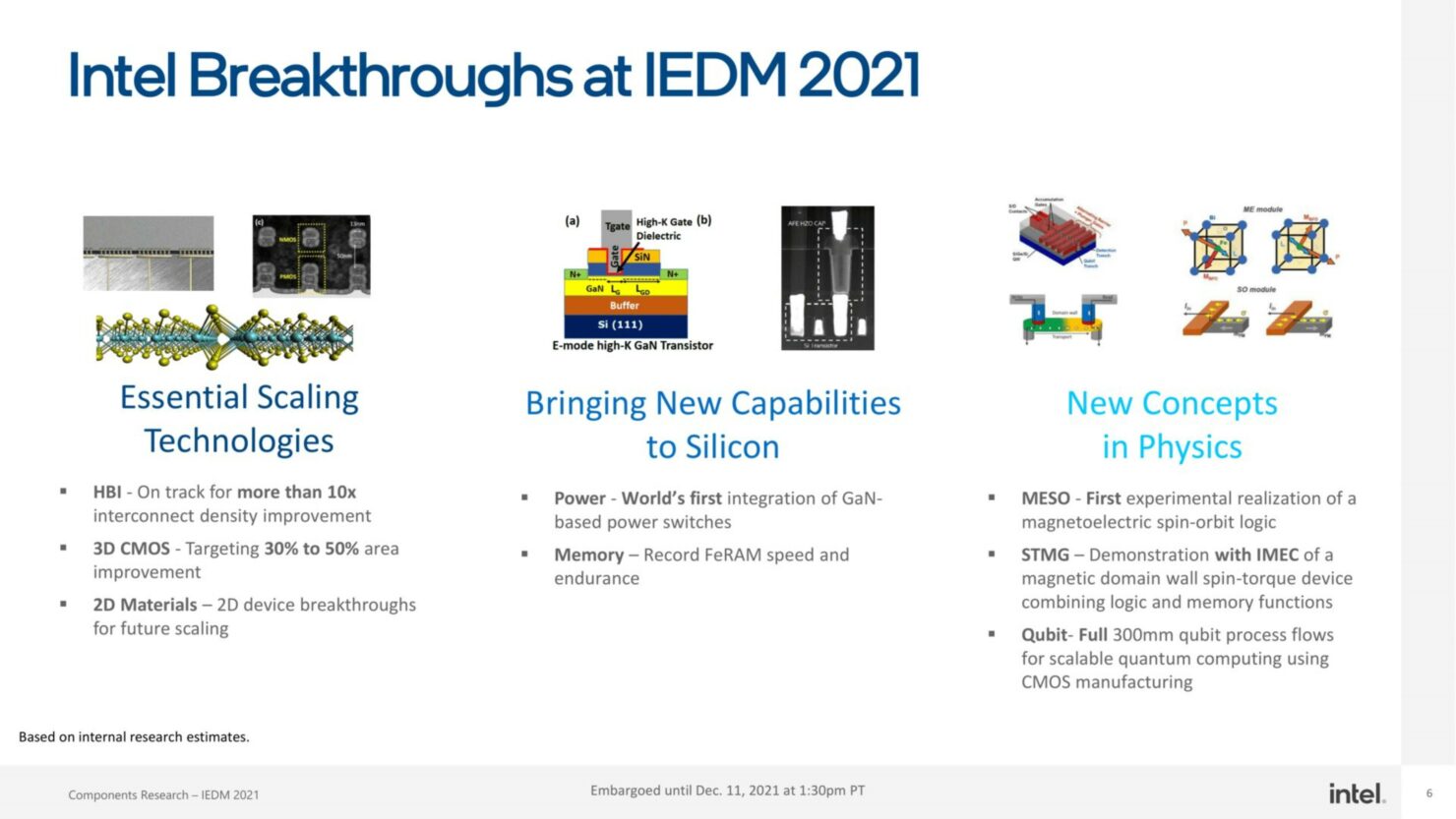

在对摩尔定律的不懈追求中,英特尔推出了关键的封装、晶体管和量子物理突破,这些突破对于推进和加速计算进入下一个十年至关重要。在 2021 年IEEE 国际电子设备会议(IEDM) 上,英特尔概述了其实现混合键合封装互连密度提高 10 倍以上、晶体管缩放面积提高 30% 至 50%、新电源和存储器技术的重大突破以及新的物理学中的概念可能有一天会彻底改变计算。

英特尔高级研究员兼组件研究部总经理Robert Chau表示:“在英特尔,推进摩尔定律所需的研究和创新从未停止。我们的组件研究小组将在 IEDM 2021 上分享关键研究突破,带来革命性的工艺和封装技术,以满足我们行业和社会对强大计算的永不满足的需求。这是我们最优秀的科学家和工程师不懈努力的结果。为了延续摩尔定律,他们继续走在创新的最前沿。”

重要性: 摩尔定律一直在跟踪计算创新,以满足从大型机到移动电话的每一代技术的需求。随着我们进入一个拥有无限数据和人工智能的计算新时代,这种演变今天仍在继续。

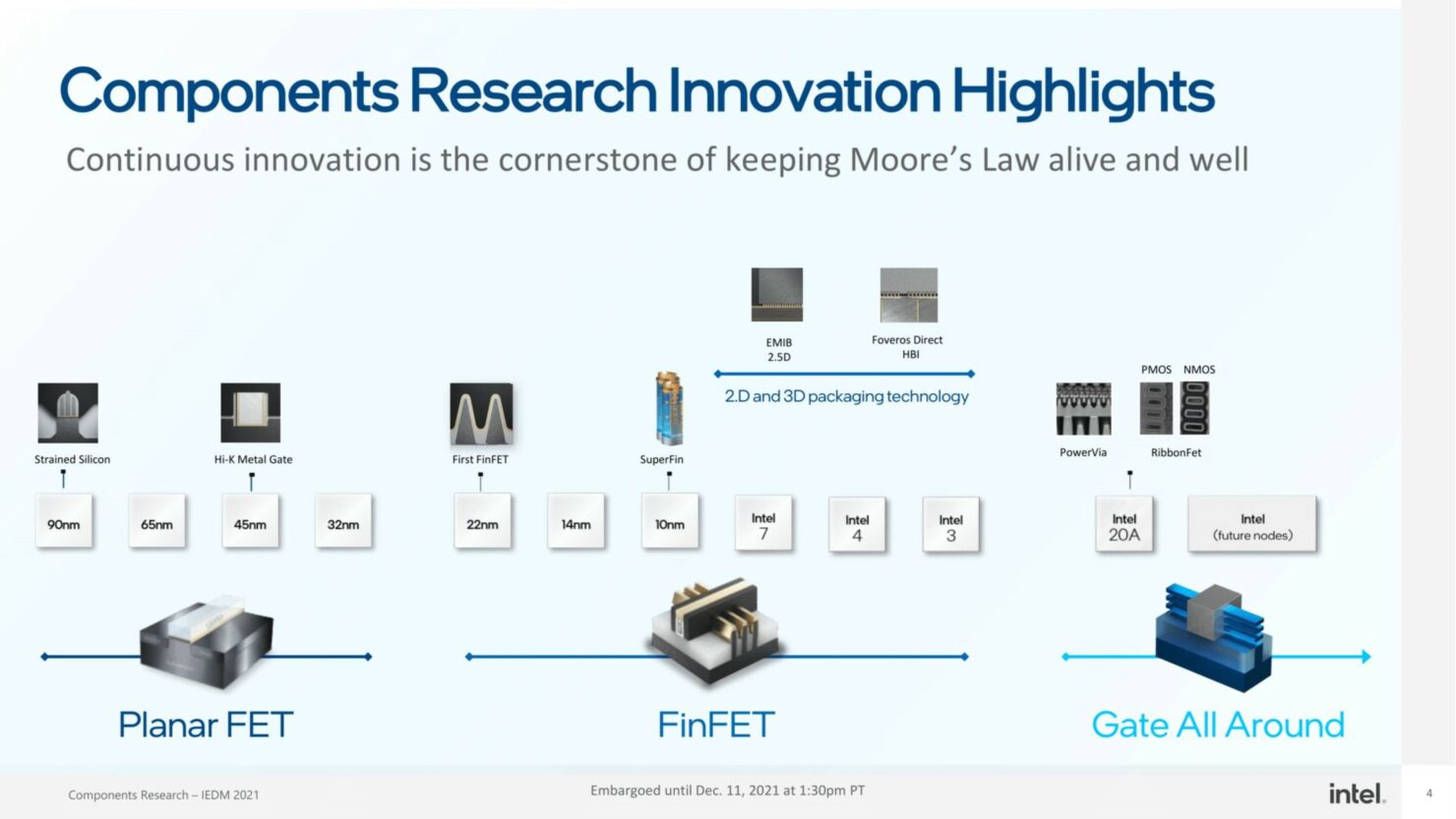

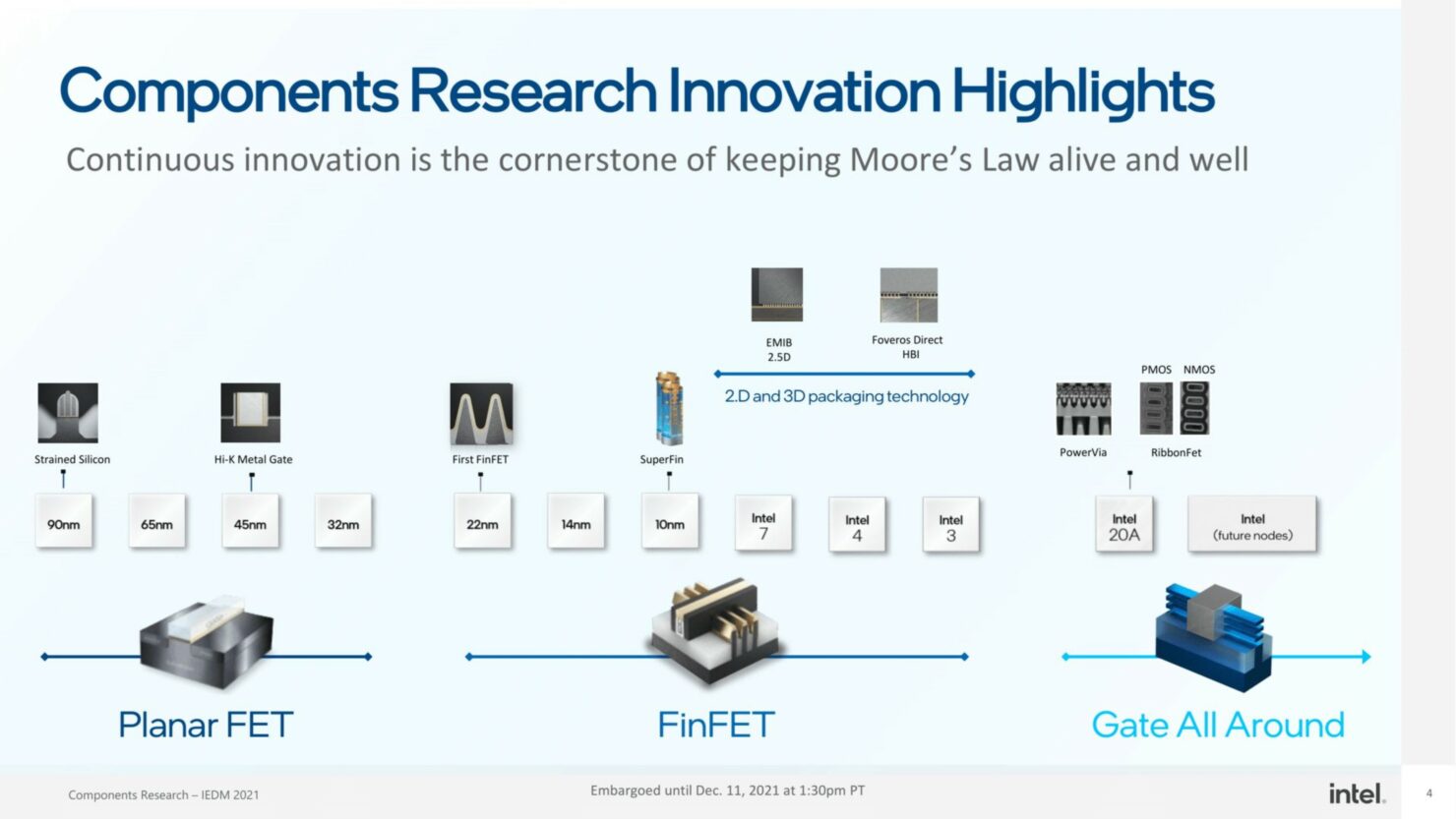

持续创新是摩尔定律的基石。

英特尔的组件研究小组致力于在三个关键领域进行创新:用于提供更多晶体管的基本缩放技术;用于功率和内存增益的新硅功能;探索物理学中的新概念,以彻底改变世界的计算方式。许多突破先前摩尔定律障碍并出现在今天产品中的创新都始于组件研究的工作——包括应变硅、Hi-K 金属栅极、FinFET 晶体管、RibbonFET,以及包括 EMIB 和 Foveros Direct 在内的封装创新。

在 IEDM 2021 上揭示的突破表明,英特尔有望通过其三个探路领域,在 2025 年之后继续推动摩尔定律的进步和优势。

1.英特尔正在对基本缩放技术进行重要研究,以在未来产品中提供更多晶体管:

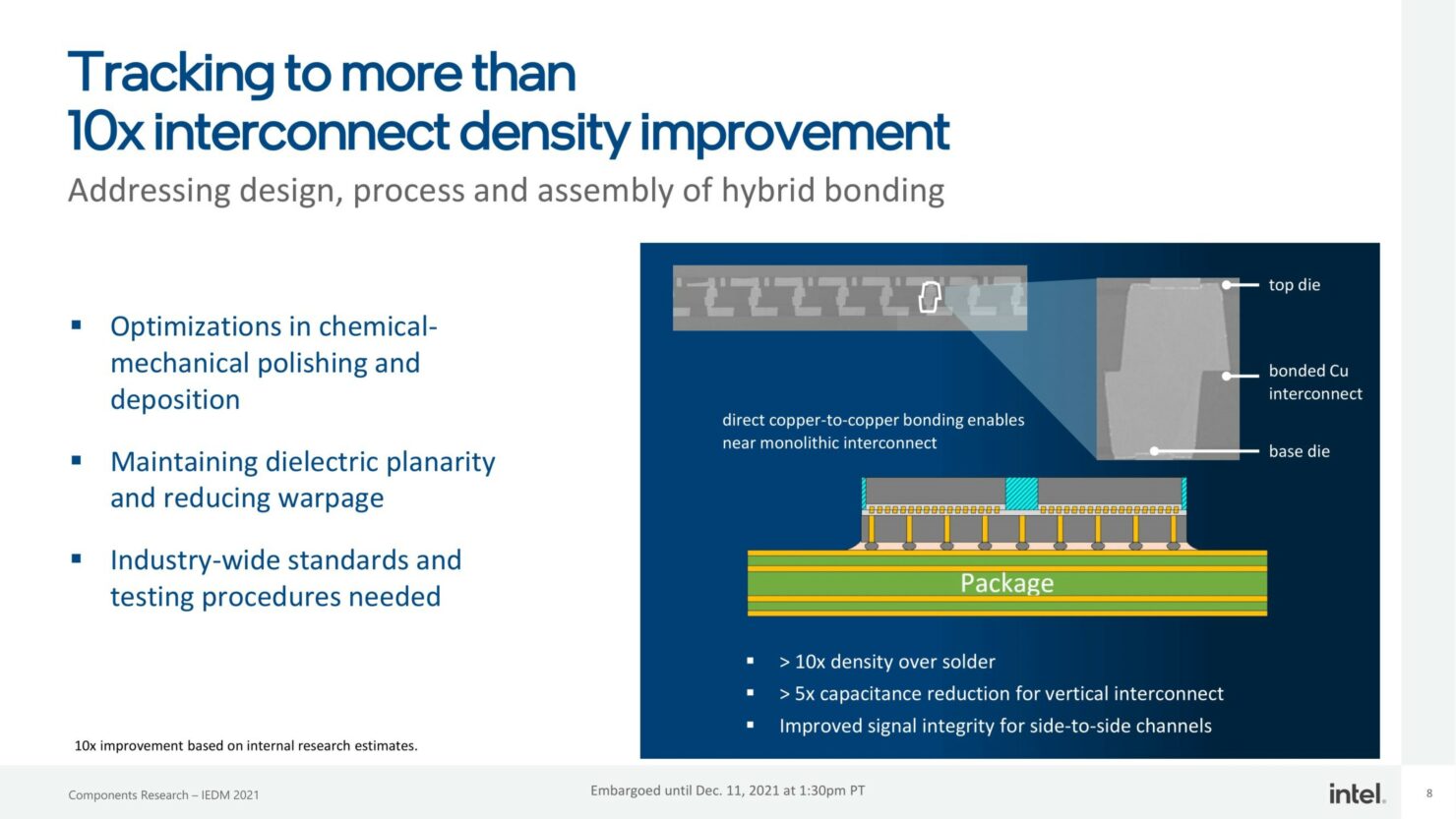

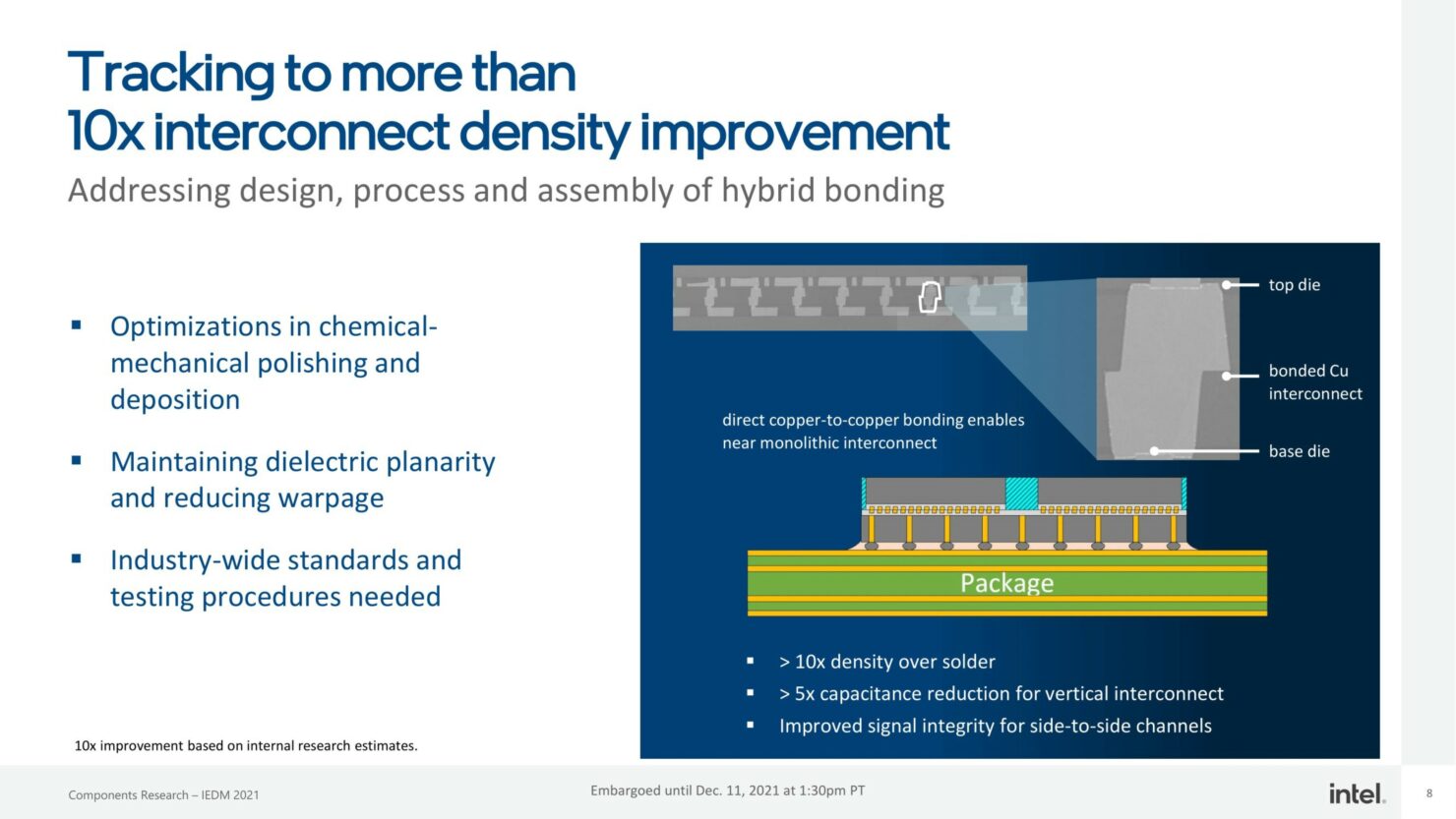

该公司的研究人员概述了针对混合键合互连的设计、工艺和组装挑战的解决方案,预计封装互连密度提高 10 倍以上。在 7 月的 Intel Accelerated 活动中,Intel 宣布了推出 Foveros Direct 的计划,支持亚 10 微米的凸点间距,为 3D 堆叠的互连密度提供一个数量级的增加。为了使生态系统能够从先进封装中获益,英特尔还呼吁建立新的行业标准和测试程序,以实现混合键合小芯片生态系统。

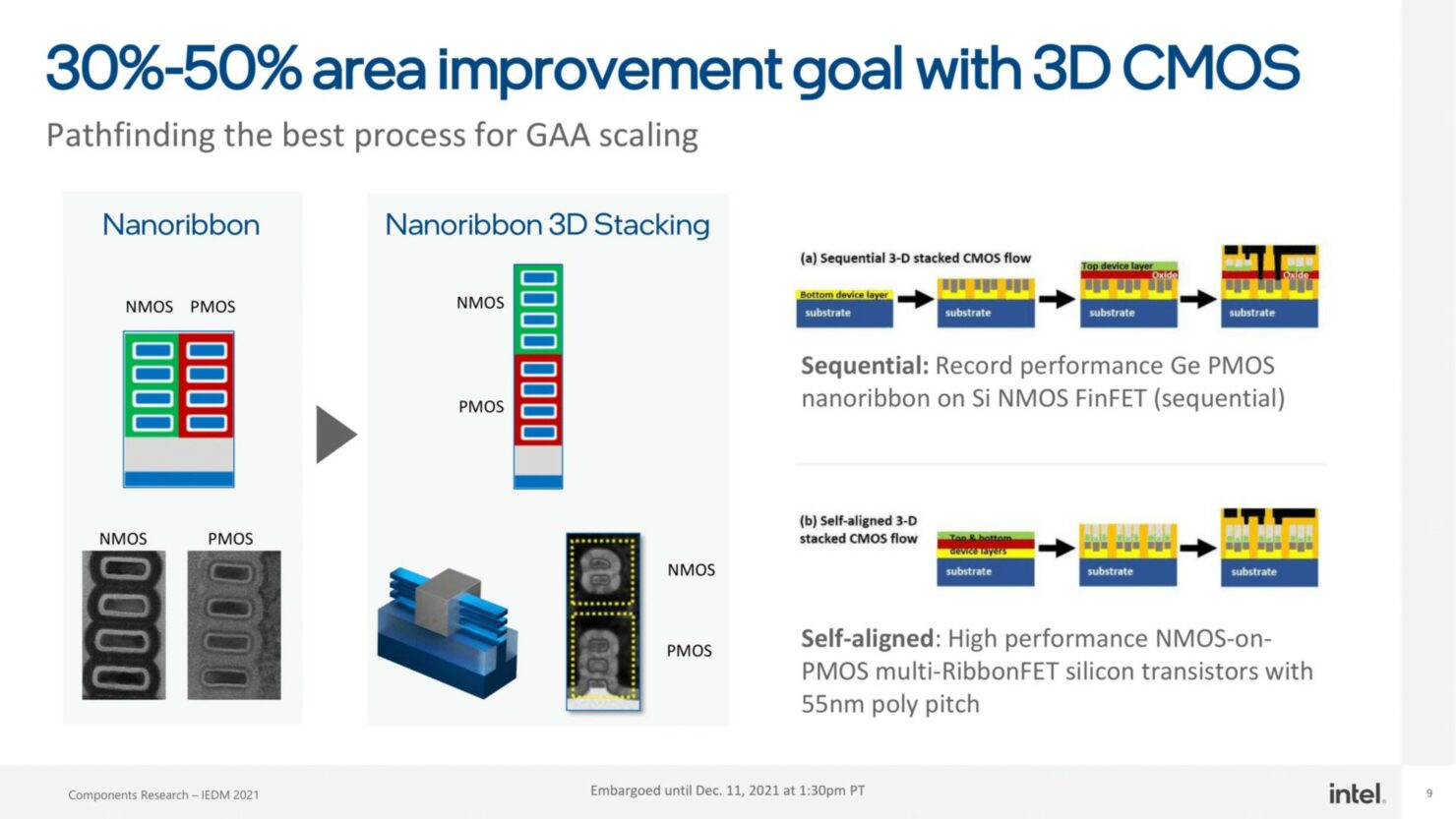

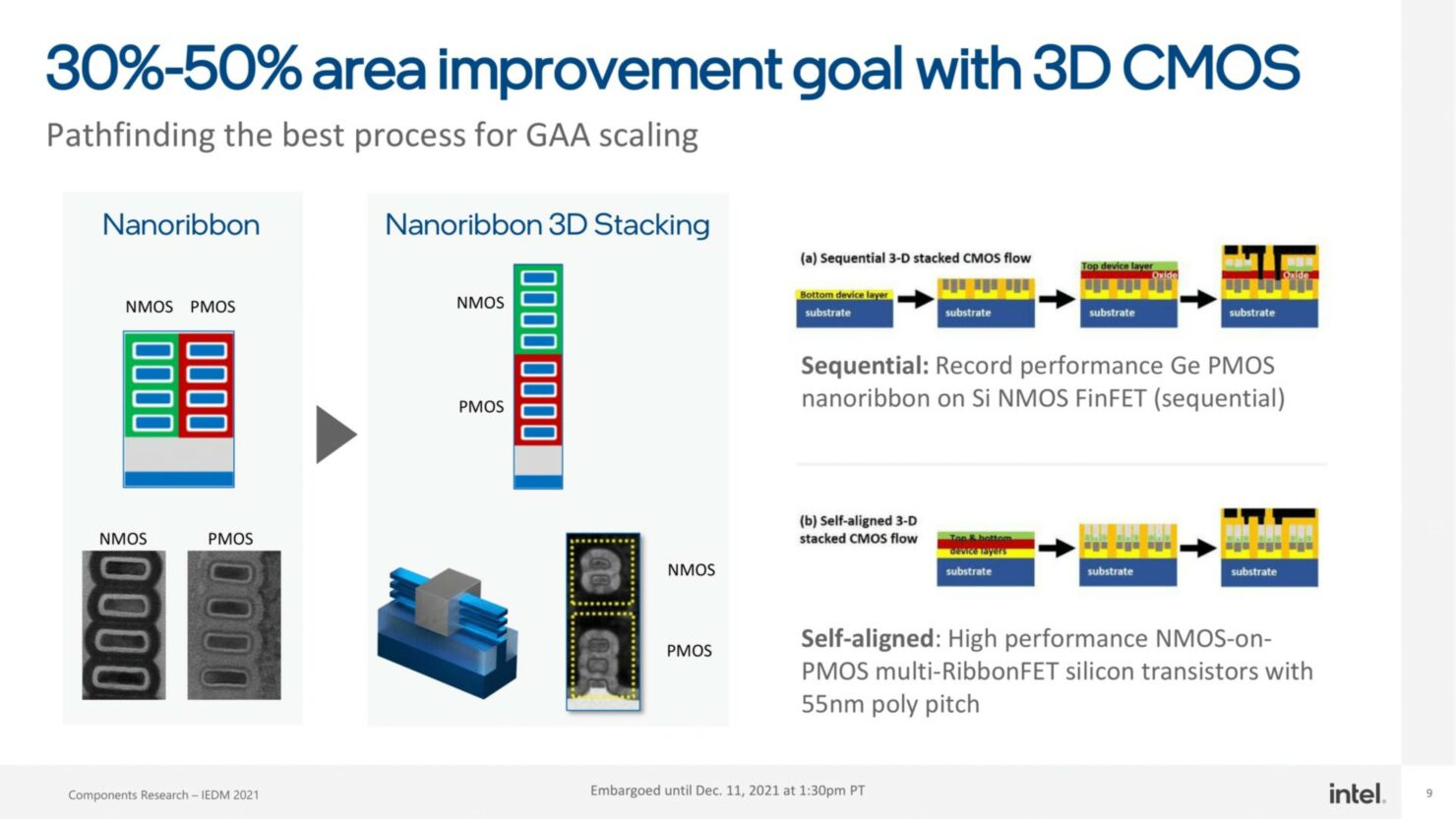

超越其全栅极 RibbonFET,英特尔正在通过堆叠多个 (CMOS) 晶体管的方法掌握即将到来的后 FinFET 时代,该方法旨在实现最大 30% 至 50% 的逻辑缩放改进,以推动摩尔定律的不断发展通过每平方毫米安装更多的晶体管。

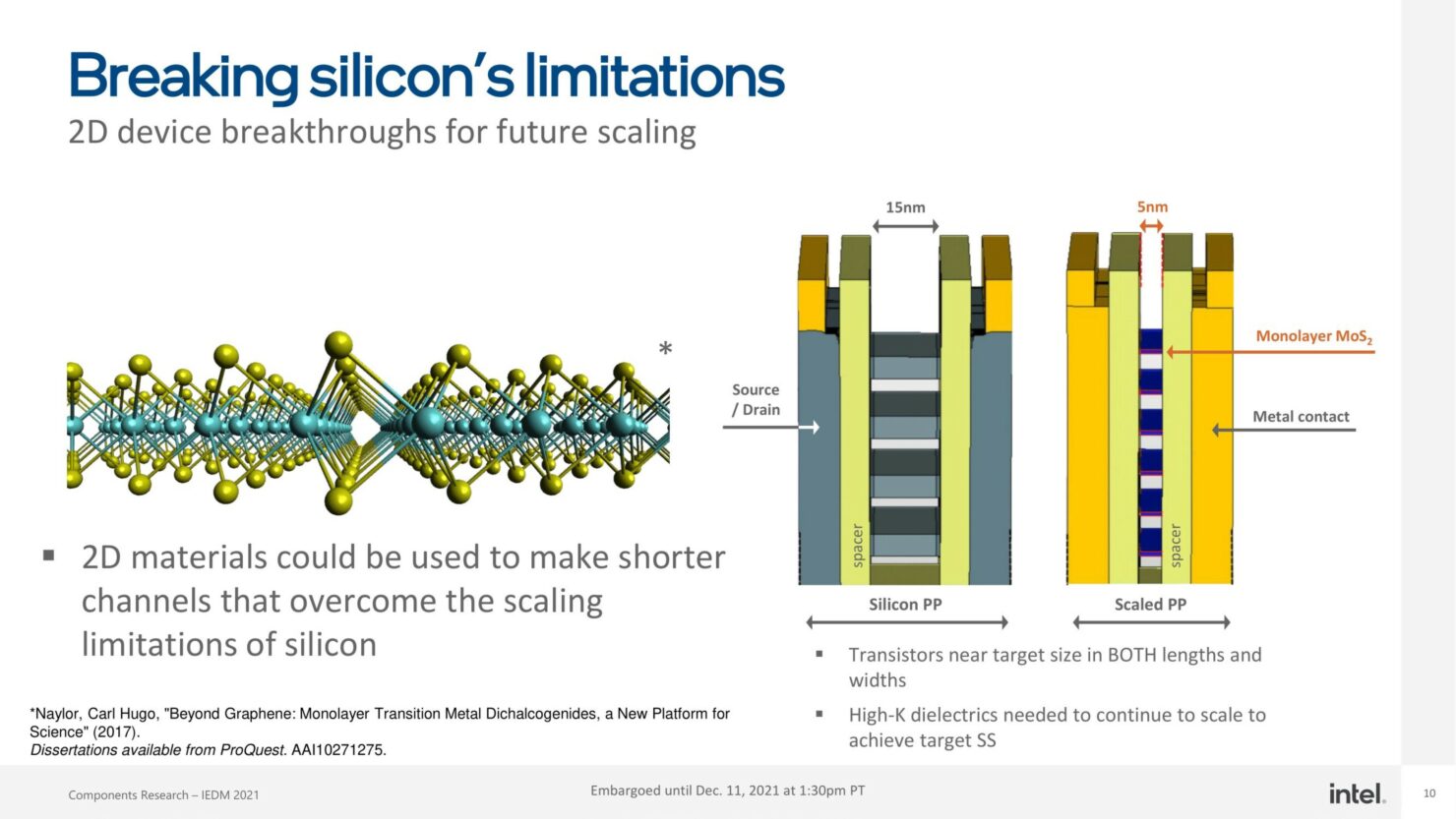

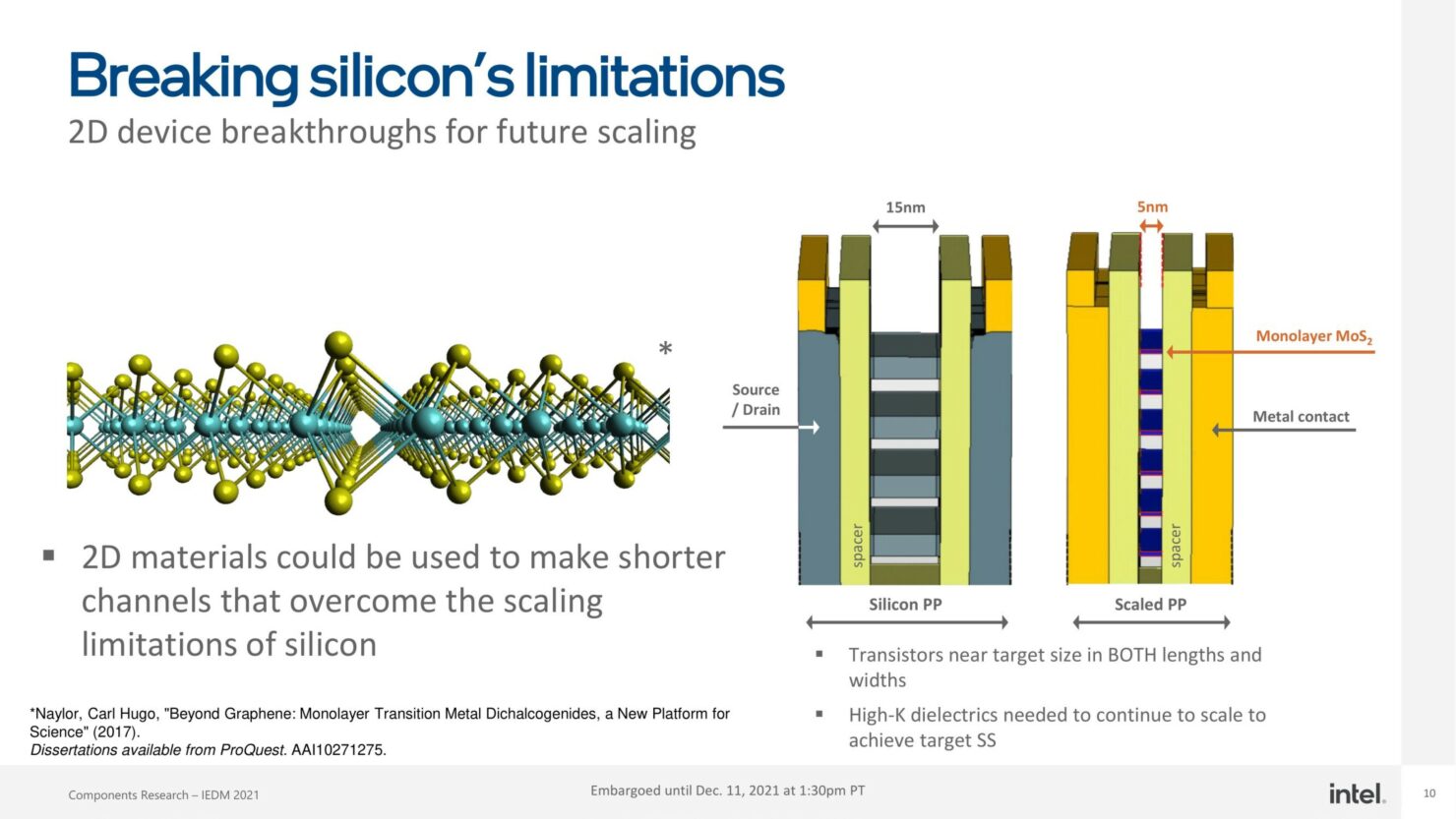

英特尔还通过前瞻性研究为摩尔定律进入埃时代铺平了道路,该研究展示了如何使用只有几个原子厚的新型材料来制造克服传统硅通道限制的晶体管,从而使每个芯片面积上增加数百万个晶体管为未来十年更强大的计算。

2.英特尔正在为芯片带来新功能:

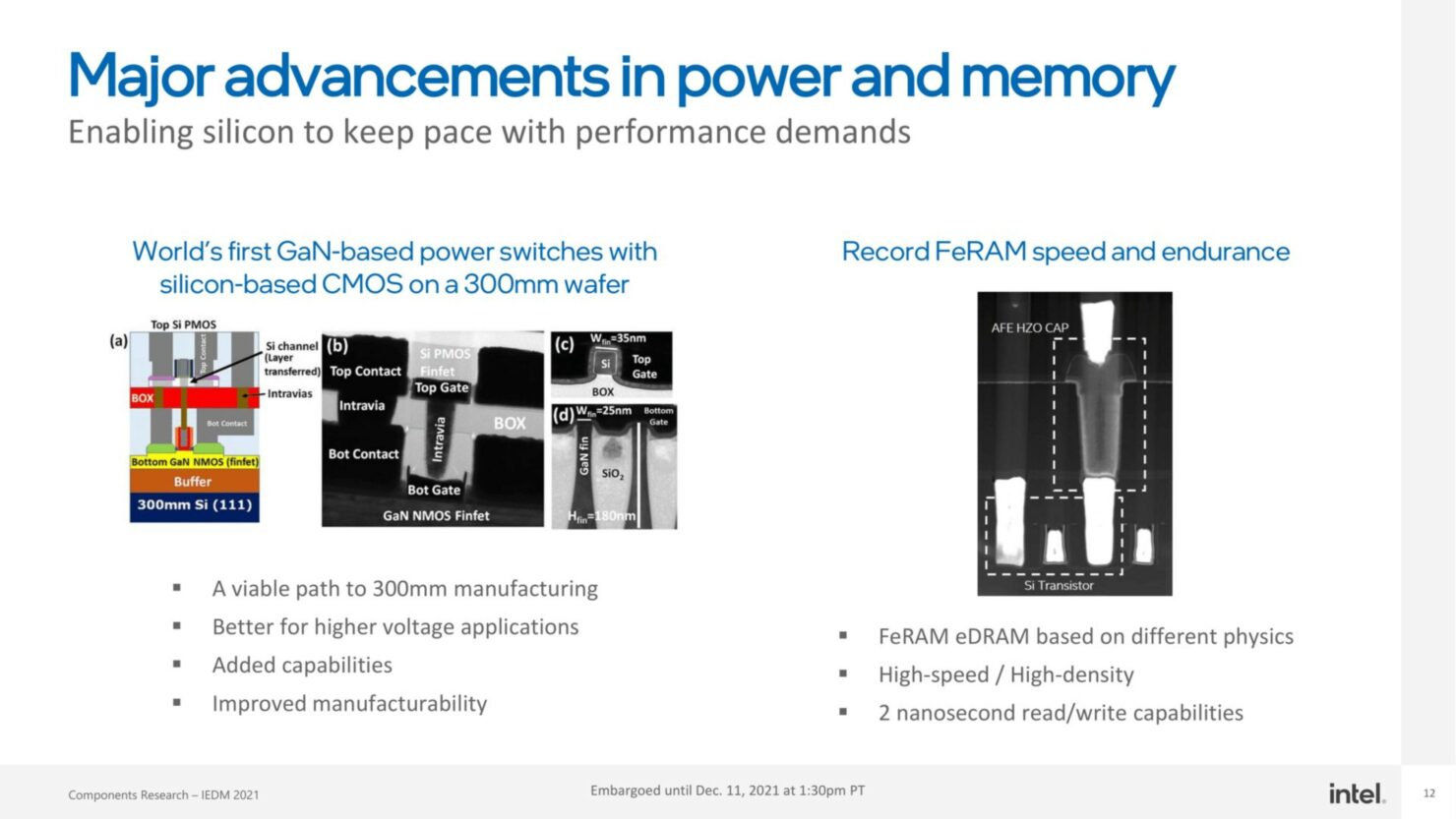

通过在 300 毫米晶圆上实现基于 GaN 的电源开关与基于硅的 CMOS 的全球首次集成,正在推进更高效的电源技术。这为向 CPU 提供低损耗、高速供电奠定了基础,同时减少了主板组件和空间。

另一个进步是英特尔行业领先的低延迟读/写功能,它使用新型铁电材料实现下一代嵌入式 DRAM 技术,该技术可以提供更大的内存资源,以解决从游戏到人工智能的计算应用程序日益复杂的问题。

3.英特尔正在通过基于硅晶体管的量子计算以及全新的开关来追求巨大的性能,以通过新型室温设备进行大规模节能计算。未来,这些启示可能会通过使用全新的物理学概念来取代经典的 MOSFET 晶体管:

在 IEDM 2021 上,英特尔展示了世界上第一个在室温下实现磁电自旋轨道 (MESO) 逻辑器件的实验性实现,这展示了基于开关纳米级磁铁的新型晶体管的潜在可制造性。

英特尔和 IMEC 正在自旋电子材料研究方面取得进展,以使器件集成研究接近实现全功能自旋扭矩器件。

英特尔还展示了用于实现与 CMOS 制造兼容的可扩展量子计算的完整 300 毫米量子位工艺流程,并确定了未来研究的下一步。

参考链接:https://wccftech.com

Demi Xia编译

责编:Demi

最前沿的电子设计资讯

最前沿的电子设计资讯