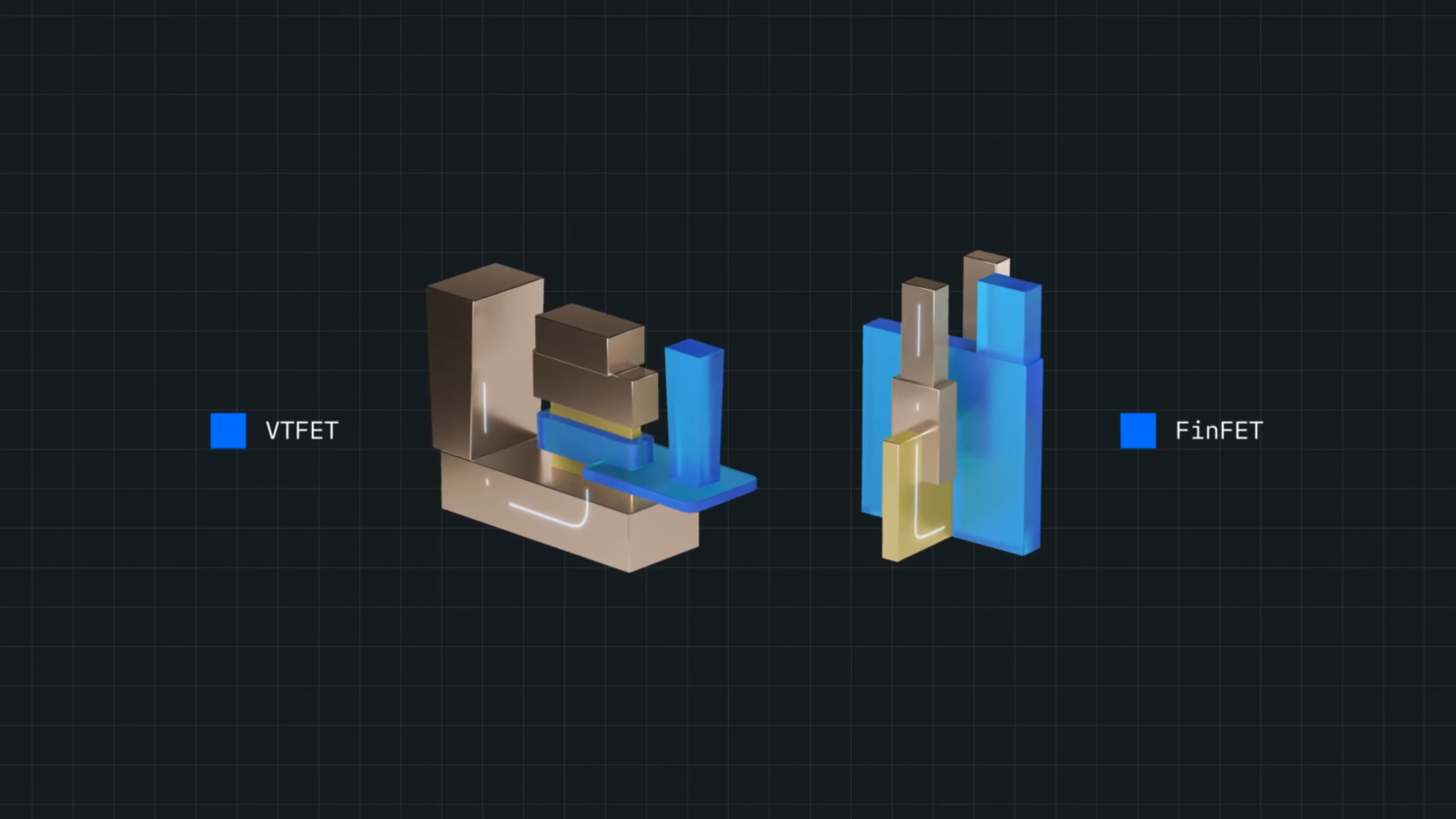

在2021 第 67 届 IEEE国际电子器件会议(IEDM)上,三星和 IBM 在他们关于“设备级 3D”的讨论中宣布共同推出垂直传输场效应晶体管(VTFET),两家科技公司合作在设计技术上取得了重大突破,这项突破性的新技术允许晶体管垂直堆叠,与按比例缩放的FinFET相比,性能可实现翻倍,或将耗能降低85%。

在谈话中,两家公司解释了如何通过将电流从水平方向重定向到垂直方向,不仅可以减小半导体芯片的尺寸,还可以使它们更加强大和高效。

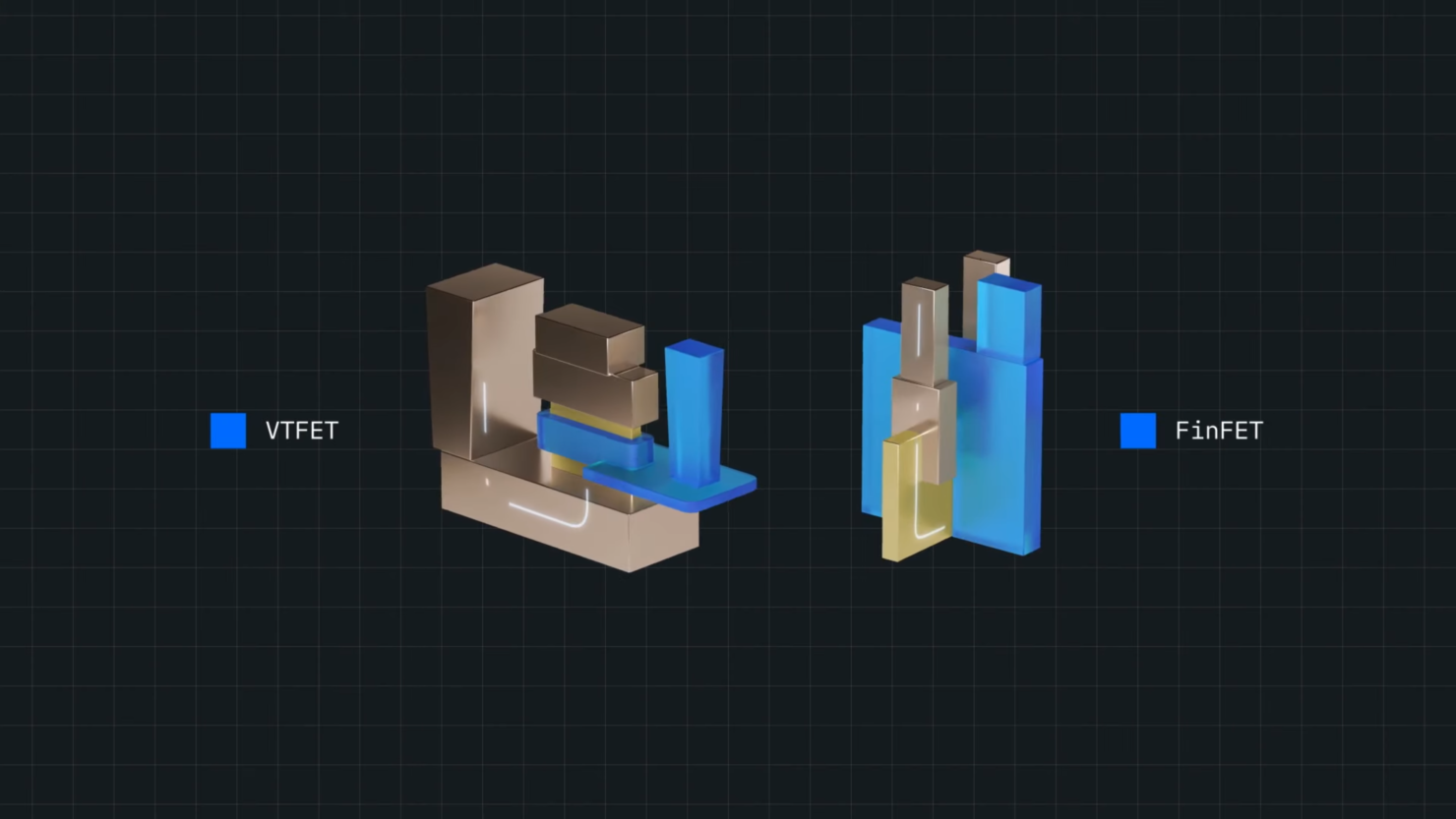

根据摩尔定律的预测,CMOS 晶体管以横向或横向方式构建,几十年来无数次的进步缩小了它们的尺寸,因此现在可以将数十亿个晶体管放入芯片中。但是进一步缩小晶体管以提高芯片性能和增加新功能是困难和昂贵的。将它们垂直放置而不是水平放置会节省空间并更容易延长摩尔定律的寿命吗?受基于沟槽的 DRAM 垂直存取晶体管的启发,IBM 和三星的一个团队将描述他们如何改变晶体管架构,在体硅上使用所谓的垂直传输纳米片 (VTFET) 和 45 纳米栅极构建 CMOS 设备沥青。

— 论文 #26.1,“用于横向传输器件之外的 CMOS 扩展的垂直传输纳米片技术”,H. Jagannathan 等人,IBM/Samsung

以前,半导体芯片将平放在硅表面上,而电流则水平流动。这种新设计允许晶体管垂直放置,而不是平行于半导体芯片的表面。新技术将使制造公司能够绕过摩尔定律的限制性能,从而因低功耗而节省能源。

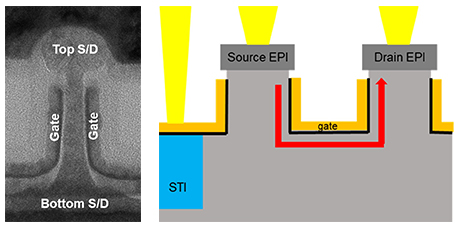

VTFET 纳米片晶体管的横截面 TEM(为了设计灵活性,源极可以位于顶部或底部),旁边是与 VTFET 共同集成的 I/O 器件 FET 的示意图。来源:IEDM 论文 26.1,“设备级别的 3D”

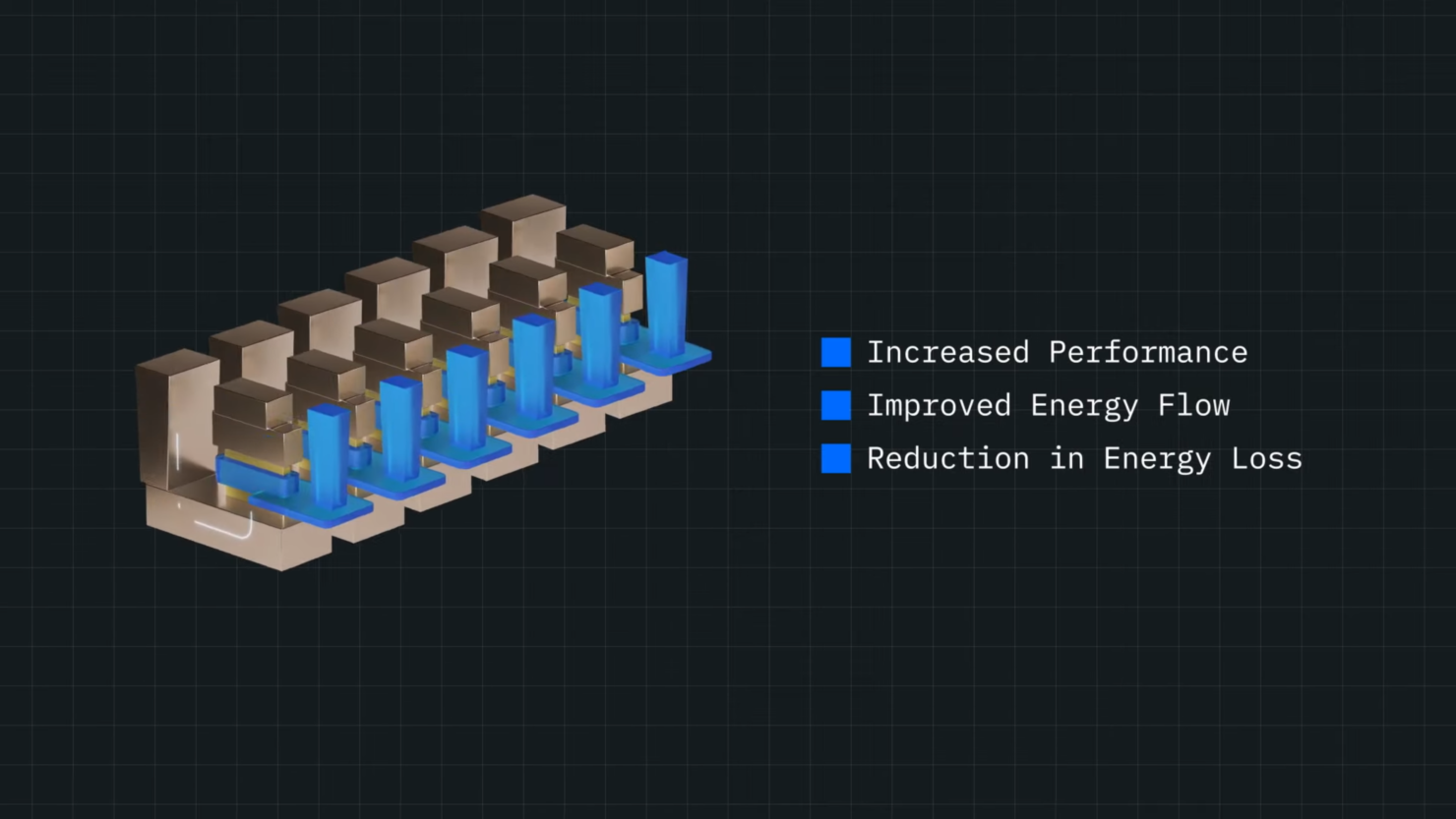

三星和 IBM 为提高效率和性能而垂直堆叠晶体管的努力被称为垂直传输场效应晶体管,或 VTFET。与当前的 FinFET 结构设计相比,两家公司之间的合作有望提供两倍的性能,或高达 85% 的功率效率提高。加密货币矿工将看到能源效率的提高,环境的影响也将从本质上得到改善。

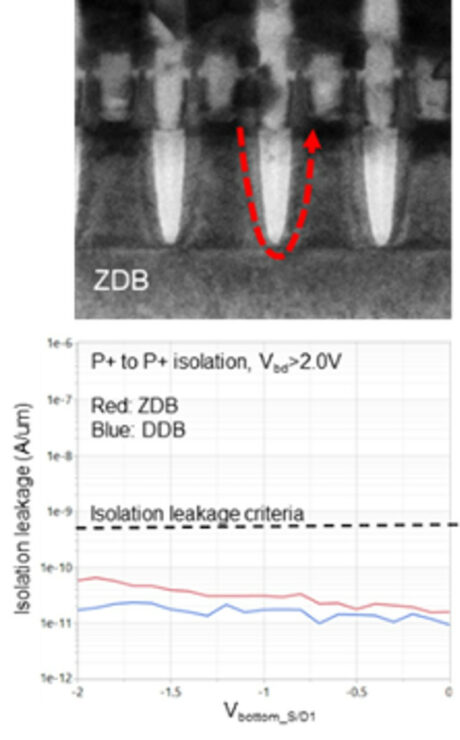

垂直器件提供了持续缩放的机会,因为栅极长度和间隔尺寸——决定栅极间距(晶体管之间的距离)的两个关键因素——可以以水平无法实现的方式进行优化。此外,由于降低了静电和寄生损耗(SS=69/68 mV/dec 和 DIBL= <30mV),VTFET 器件有望提供出色的工作电压和驱动电流。为了验证这一概念,研究人员使用 VTFET 来制作功能性环形振荡器(测试电路),与横向设计参考相比,这表明电容减少了约 50%。

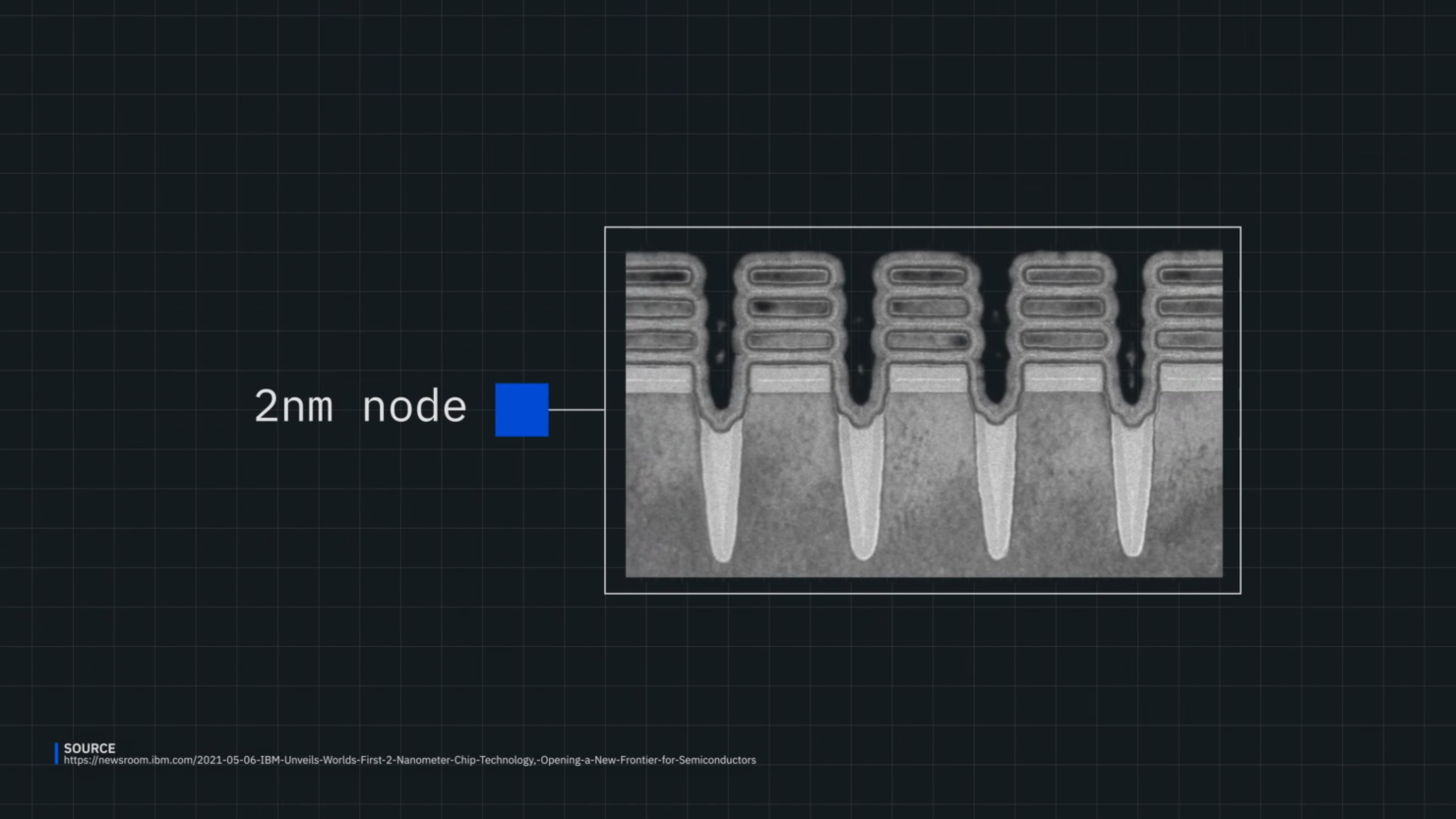

零扩散断裂形成结构的 TEM,表明它在高电路密度下满足隔离标准。来源:IEDM 论文 26.1“设备级别的 3D”

参考链接:https://www.ieee-iedm.org/call-for-papers-overview;Demi Xia编译

责编:Demi

最前沿的电子设计资讯

最前沿的电子设计资讯