处理器的计算速度比内存单元的速度快得多的问题多年来一直是众所周知的。用技术术语来说,这被称为“冯诺依曼瓶颈”。出现瓶颈是因为内存和计算单元是分开的,通过所谓的数据总线来回发送信息需要时间,这限制了速度。

日前,瑞典隆德大学的研究人员提出了一种将存储单元与处理器集成的新解决方案,该解决方案可以实现更快的计算,可用于克服冯诺依曼瓶颈——需要在单独的内存和计算单元之间打乱数据——并有助于提高计算性能。

该研究结果发表在Nature Electronics 上。

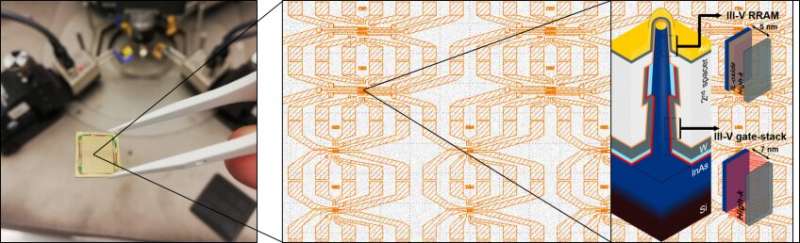

研究人员展示了一种新的配置,其中存储单元与垂直晶体管选择器集成在一起,所有这些都在纳米级。与当前的大容量存储解决方案相比,这带来了可扩展性、速度和能源效率的改进。

任何需要处理大量数据的事物,例如人工智能和机器学习,都需要速度和更大的容量。为了成功,内存和处理器需要尽可能靠近。此外,必须能够以节能的方式运行计算,尤其是当前技术会在高负载下产生高温。

隆德大学

传统上,限制一直存在于电路板的构造中,其单元在平面上彼此相邻放置。现在的想法是在 3D 配置中垂直构建并集成内存和处理器,计算发生在内存电路本身内。

“我们的版本是底部有一个晶体管的纳米线,还有一个非常小的存储元件位于同一根线上的更远位置。这使它成为一个紧凑的集成功能,其中晶体管控制存储元件。这个想法之前已经存在,但事实证明,实现性能很难。然而,现在,我们已经证明这是可以实现的,而且效果出奇的好,”纳米电子学教授 Lars-Erik Wernersson 说。

研究人员正在使用 RRAM(电阻式随机存取存储器)存储单元,这本身并不是什么新鲜事,新的是他们如何成功地实现了功能集成,从而产生了巨大的可能性。它最终在从人工智能和机器学习到普通计算机的所有领域开辟了潜在的新研究领域和新的改进功能。例如,未来的应用可能是各种形式的机器学习,例如基于雷达的手势控制、气候建模或各种药物的开发。

Demi Xia编译

最前沿的电子设计资讯

最前沿的电子设计资讯