英特尔可能会将目光重新投向晶体管的设计上,以便在2nm或以下等级的半导体工艺上使用。

近期,一项新的专利似乎指明了英特尔前进的方向,即“堆叠叉片式晶体管(stacked forksheet transistors)”技术,以保持摩尔定律前进的动力。专利并没有提供太多的细节,而且英特尔也没有提供PPA的改进数据作为参考。

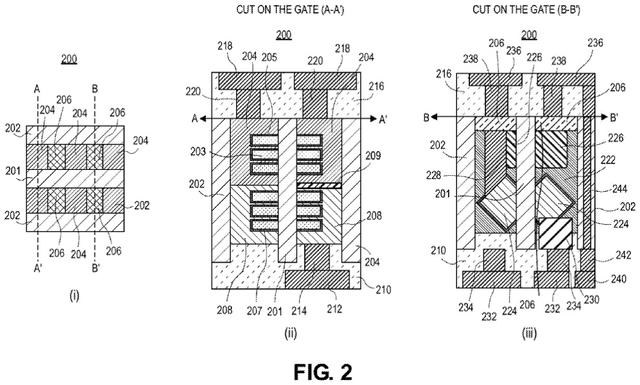

英特尔表示,新的晶体管设计最终可以实现3D和垂直堆叠的CMOS架构,与目前最先进的三栅极晶体管相比,该架构允许增加晶体管的数量。在专利里,英特尔描述了纳米带晶体管和锗薄膜的使用,后者将充当电介质隔离墙,在每个垂直堆叠的晶体管层中重复,最终取决于有多少个晶体管被相互堆叠在一起。

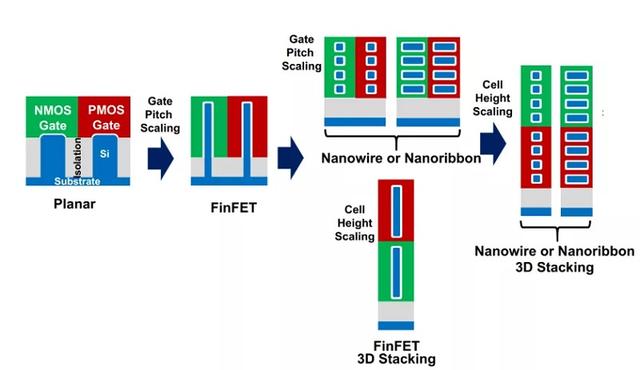

英特尔早在2019年就在IEDM活动上展示了3D逻辑集成方面的研究,当时称为堆叠纳米片晶体管技术。至于相关技术如何提高晶体管密度、性能和能效的具体数据,英特尔至今都没有公开。

值得一提的是,英特尔并不是第一家引用这种制造方法的公司。

位于比利时的研究小组Imec在2019年曾宣布,开发出第一个相关技术的标准单元模拟结果,显示当应用于2nm制程节点的时候,会比传统方法显著提供晶体管密度。其寄望于恒定速度下10%的速度提升或24%的能效提升,同时会有20%的单元面积减少。此外,静态随机存取存储器(SRAM)占用的空间将显著减少30%。

根据 Imec 的第一个标准单元模拟结果,当应用于 2nm 技术节点时,与传统的纳米片方法相比,该技术可以显着提高晶体管密度。我们希望在恒定速度下提高 10% 的速度或提高 24% 的能效,同时“减少 20% 以上的电池面积”。此外,静态随机存取存储器 (SRAM) 占用空间(通常构成 CPU 的高速缓存并且是芯片面积的最重要贡献者之一)显着减少了 30%。

与台积电宣布的 3nm 节点相比 5nm 的改进:性能提升 10% 到 15%(在相同的功率和晶体管数量下),最多降低 30% 的功率(在相同的时钟和复杂性下),最多 70%逻辑密度增益(适用于内核)和高达 20% 的 SRAM 密度增益。

事实上,英特尔与Imec在纳米电子学领域有着密切而长久的联系,后者的研究成果也是英特尔新专利的基础。

目前尚不清楚英特尔是否会在 2nm 工艺中选择堆叠叉板架构,或者是否希望更早地获得其设计优势。但英特尔提交了专利申请,这最终意味着该设计具有一定的价值。不幸的是,该公司似乎比我们更了解这项技术的可行性。

Demi Xia编译

最前沿的电子设计资讯

最前沿的电子设计资讯