半导体存储器是一种能存储大量二进制信息的半导体器件,半导体存储器种类很多,一般按功能来分,可以分为只读存储器(ROM)和随机存储器(RAM)。

ROM结构简单,断电以后数据还保留着;重新上电,读出来的数据还能恢复成原来的样子。

图1 ROM重新上电信息保留

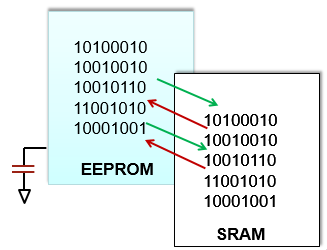

RAM就不一样了,每次上电之后,上一次的信息无法保留。

图2 RAM重新上电信息丢失

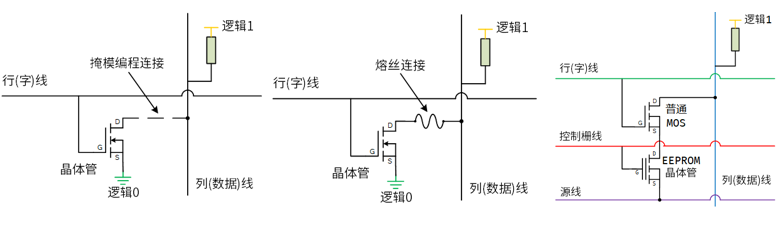

只读存储器主要分为掩膜存储器、可编程存储器(PROM)、电可擦写可编程存储器(EEPROM)和Flash等等。

掩膜只读存储器:定制产品,按照用户要求来,内部数据在出厂时就被设定好,后续无法修改。

可编程只读存储器:也叫“反熔丝”,比掩膜存储器高级点,出厂时可以烧写一次,但如果烧错了,只好作废换下一个。

EEPROM(E2PROM):为了重复利用,这代产品首先研究了第一代通过紫外线擦除的EPROM产品。这代产品是将电荷通过浮栅雪崩注入MOS管(FAMOS)、或者叠栅雪崩注入MOS管(SIMOS),通过雪崩效应编程。这种产品擦出复杂,而且擦写速度很慢。

后来经过改良升级,改采用浮栅隧道氧化层MOS管注入,取名“EEPROM”,也称作“E2PROM”。为了提高擦写可靠性,并保护隧道氧化层,EEPROM还会再加一个选通管。程序读写时,主要通过字线和位线施加脉冲来实现操作。

图3 掩膜存储器、反熔丝存储器、EEPROM一览

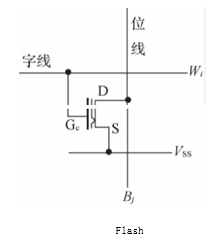

快闪存储器Flash是在EPROM和EEPROM的基础上做了一些改进,它采用一种类似于EPROM的单管叠栅结构的存储单元,只用一个单管来实现。

图4 Flash存储器单元结构

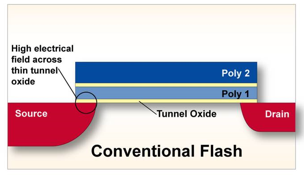

快闪存储器Flash的结构与EPROM的SIMOS管类似,主要差异为浮栅与衬底氧化层的厚度不同,下图是一个Flash的叠栅MOS管结构。

图5 普通Flash的叠栅MOS管结构

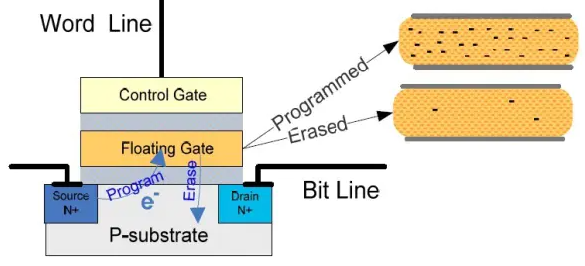

快闪存储器究竟是怎么保存数据的呢?Flash擦写是通过改变浮栅上的电荷来实现的。写入时,漏极经过位线接正压,并将衬底接地,在字线上加脉冲高压(18~20V),源级和漏极之间会发生雪崩击穿,部分电子会穿过氧化层到达浮栅,形成浮栅充电电荷。

擦除即是将电子从浮栅移出来实现。擦除时,将字线接地,同时,在P阱和N衬底上偏置一个正的脉冲高电压(约20V)。这时,浮栅上面的电荷又会通过隧道效应被移出。

读取Flash时,一般在字线加正常逻辑电平(一般3.3V或者5V),源级接地,当浮栅上存在电荷时,MOS管截止,输出1状态信号。反之,浮栅上没有电荷,MOS管导通,输出0状态信号。

图6 Flash单元擦写示例

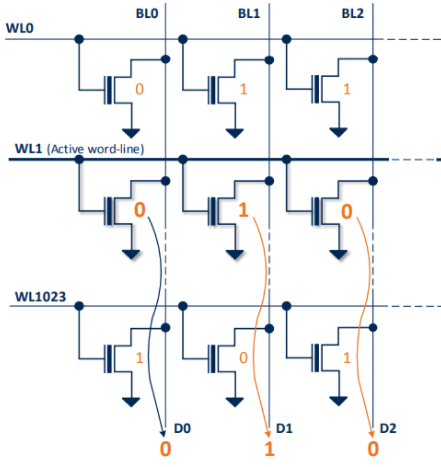

快闪存储器的本质是存储阵列,通过对浮栅上的电荷与字线逻辑电平作比较来判断的。以Nor Flash为例。按照正常的工作方法,字线工作,会加正常逻辑(3.3V或5V);字线不工作,通常是悬空或者输入0V电平。

正常情况,当字线不工作时,无正常逻辑(3.3V或5V)施压到栅极,不论浮栅上有无电荷,MOS管都要求截止。

如果Flash出现过擦除,这时,浮栅上会表现为高压,输出电压值不确定。如果电压值刚好能使该单元的MOS管导通,此时,无论选择哪个字线,该位线的读值都是0V,从而影响其他单元的读写,这被称为“单元泄露”。因此,为了让Flash避免过擦除,对擦除的时候会非常小心,从而让擦除时间变长。

图7 Nor Flash操作示意图

前面提到,快闪存储器的功能很强大,但擦除速度太慢。针对这一问题,Wolfe Yu介绍了世健代理的Microchip旗下SST发明的一种全新超级快闪存储SuperFlash®技术。

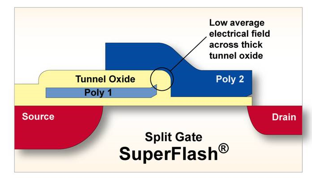

图8 SuperFlash®闪存的叠栅MOS管结构

在SuperFlash闪存中,控制栅被分成两部分,只覆盖一部分浮栅,它可以直接控制流入漏极的电流。

过度擦除留下的正电荷会产生单元泄漏路径,导致闪存无法正确读取数据。对于SuperFlash闪存来说,由于控制栅直接管理漏极边缘,过度擦除无法使浮栅的泄漏路径的达到漏极。所以,SuperFlash闪存不会考虑过度擦除问题,相对来说,擦除时间就会短很多。

随机存储器,可以随时随地读写数据,读写方便,操作灵活。但是,RAM存在数据易失性的缺点。RAM主要分为动态随机存储器DRAM和静态存储器SRAM两大类。

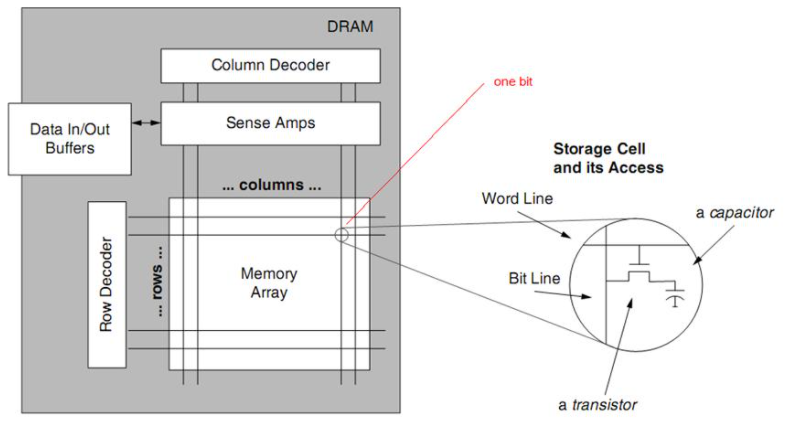

动态随机存取存储器(Dynamic Random Access Memory,DRAM)是一种半导体,主要的作用原理是利用内存储来代表一个(bit)。由于在现实中晶体管会有漏电电流的现象,导致电容上所存储的电荷数量无法判别数据,从而造成数据毁损,因此DRAM需要周期性地充电。由于这种定时刷新的特性,因此被称为“动态”存储器。

图9 DRAM结构示意图

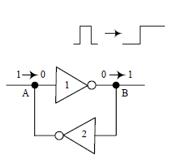

静态随机存取存储器(Static Random Access Memory,SRAM)是在静态触发器的基础上构成,靠触发器的自保功能存储数据。

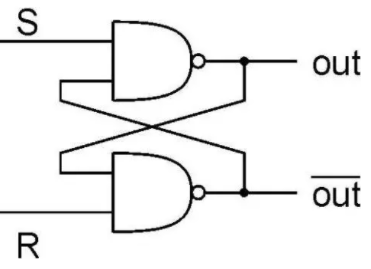

SRAM的存储单元用六只N沟道MOS管组成,其中四个MOS管组成基本RS触发器,用于记忆二进制代码;另外两个做门控开关,控制触发器和位线。

图10 SRAM结构示意图

RS触发器,是最常见的基本数字锁存单元, FPGA的LUT的主要组成部分,结构简单,操作灵活,RS触发器有一个致命的缺陷,容易产生竞争冒险。

图11 SRAM构造RS触发器数字逻辑示意图

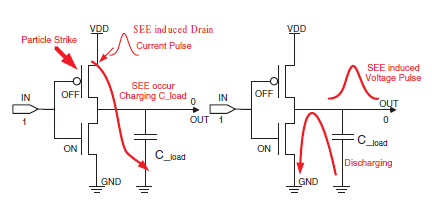

RS触发器有着非常好的锁存性能,但也有一个设计缺陷。在实际应用中,特别是在空间环境存在辐射的一些场景,会出现带电粒子穿过P管漏区有源区。此时,在粒子径迹上电离产生大量电子空穴对,形成“瞬态电流”。

图12 单粒子翻转事件充电原理

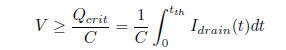

当上管出现一次电离辐射,通过建模,可以大致算出输出电压脉冲和累积电荷、以及存储电容存在一定关系。

假设,如果前级输入是逻辑1,输出是逻辑0,存储单元电容为100fF,只要累积电荷达到0.65pC-0.7pC时,输出电压脉冲幅值>0.7V,就很容易判断为输出为高电平。在输出端电压脉冲恢复到零电平之前,通过反馈,将逻辑0写入输入,从而造成输出端电压固定在高电平,变成逻辑1,出现粒子翻转效应。这也是我们常说的数字电路的竞争冒险现象。

图13 RS触发器引起竞争冒险现象

单粒子翻转会造成存储数据的改写,特别是行业多数FPGA芯片,大多是基于SRAM型的产品。一旦工作在恶劣环境下,极有可能引发产品工作异常,最终导致整个系统失灵。

一般来说,通过三模冗余、时间冗余和错误检测与纠正等电路结构设计加固方法,可对其进行改善。

不过最好的解决方法是采用Flash型FPGA。由于Flash型FPGA和基于锁存器原理的SRAM FPGA的存储原理完全不同,所以很难发生通过简单的电离辐射改写逻辑单元的情况,从而提高了可靠性。同时,Flash技术的产品的功耗也比SRAM的功耗低很多。

目前,基于Flash工艺的FPGA主要是Microchip。它拥有基于反熔丝和Flash技术的FPGA,目前市场上主流产品是第三代SmartFusion® ProASIC®3/IGLOO®、第四代SmartFusion® 2/IGLOO2和第五代PolarFire/PolarFire SoC系列。

相对于传统的主流半导体存储器,非易失性只读存储器(ROM)和易失性随机存储器(RAM),还有一些速度较快,而且非易失性存储器,比如铁电存储器(FRAM)、和非易失性随机存储器(EERAM)。

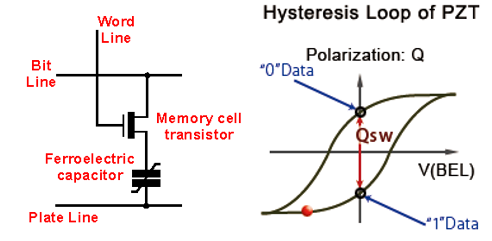

上文有提到,EEPROM是通过电荷泵对浮栅操作来做数据存储,浮栅的擦写需要时间,还会破坏浮栅单元,存在次数限制。铁电存储器(FRAM)是采用一种特殊工艺的非易失性的存储器,是采用人工合成的铅锆钛(PZT) 材料形成存储器结晶体。

当一个电场被加到铁电晶体时,中心原子顺着电场的方向在晶体里移动。当原子移动时,它通过一个能量壁垒,从而引起电荷击穿。内部电路感应到电荷击穿并设置存储器。移去电场后,中心原子保持不动,存储器的状态也得以保存。铁电存储器不需要定时更新,掉电后数据能够继续保存,速度快而且不容易写坏。

铁电存储器是个好东西,不过有一个致命的弱点,贵。用在低成本的工业和消费场合性价比不高。

图14 铁电存储器原理

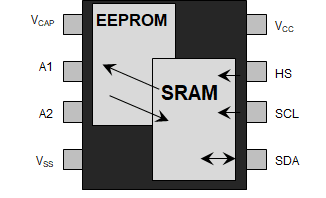

除了上文提到的FRAM,还有一种新型非易失性随机存储器(EERAM),这个产品是Microchip的独家秘籍。

图15 非易失性随机存储器架构

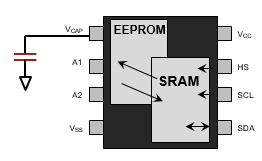

EERAM的工作原理非常简单,灵感来源于采用后备电池供电的SRAM,它的本质就是不需要外部电池,而是通过一个很小的外部电容器,SRAM和EEPROM之间通过IC监测共集极的电压,一旦电源电压较低,就通过电容供电,把SRAM的数据搬到EEPROM里面,防止信号丢失。

对于需要不断更新的存储数据,EERAM采用了一种特殊的工作方式,在监测到供电电压异常的时候,通过Vcap作为备用电源,把数据从SRAM转移到EEPROM,自动完成数据的安全转存。

当供电重新恢复正常,EEPROM的数据又自动导出到SRAM。而且,你也可以手动刷新数据到EEPROM。

图16 非易失性随机存储器用电容为SRAM转移数据提供电源

EERAM的优势包括: 自动通过断电可靠地保存数据、无限次写入数据、 低成本方案和 接近零时间的间隔写入。这个器件性能较高,而且价格也没有铁电那么昂贵,非常适合防数据丢失,成本敏感的客户。

图17 非易失性随机存储器工作原理

随着5G通信等市场的快速爆发,越来越多的定制产品层出不穷。由于存储器大多都要暴露在十分苛刻的环境中,市场对万能芯片FPGA的需求越来越大。Excepoint世健拥有专业的技术团队,其代理的Microchip 的FLASH型FPGA能有效抵抗辐射从而提高系统的可靠性,快速的SuperFlash和创新的EERAM技术的存储器等解决方案也都非常有特色,能帮助客户降低存储成本,为客户的系统设计需求提供更多选择。

最前沿的电子设计资讯

最前沿的电子设计资讯