世界正在经历一个前所未有的时代,数据呈爆发增长之势,随着新技术在更广泛的范围内实现,这一趋势预计将进一步加快。典型的实例包括:5G形式的下一代无线通信,领域不断扩展的人工智能和机器学习、物联网(IoT)、加密货币、虚拟现实,甚至汽车等诸多领域。在整个2021年,预计生成的数据达到了44万亿GB (440万亿亿字节),估计地球上每人每秒生成了1.7MB数据。这么庞大的数据量都需要比以往更快的速度进行存储、访问和分析,这就要求系统拥有更高的带宽,更高的存储密度,更高的整体性能。

为应对生成的数据量越来越高,必需提高内存性能,来存储、传送和处理所有这些信息。这个流程的主要瓶颈是内存能够访问和传送数据的速度。内存访问时间较慢,会导致整体系统性能拖后腿,而且数据吞吐量本身也受限于内存的传送速率。在历史上,高性能、快速访问内存的主导形式一直是双数据速率同步动态随机访问内存(DDR SDRAM)。DDR SDRAM是上个世纪90年代作为标准推出的,问世后得到极快速发展,2014年推出了第四代标准——DDR4。DDR4是一种内存接口,初期的数据传送速率为1600 MT/s,随着标准走向成熟,最后达到了3200 MT/s。这在电脑处理器只有8核时足够了,但当今28-64核多核处理器的问世(未来可望达到80 – 96核),则很明确,我们需要的内存性能已经超出了DDR4的能力范围。

为了帮助满足这一需求,业内正从DDR4迁移到下一代DDR内存标准——DDR5。DDR5将接替上一代标准,成为占主导地位的快速增长的标准。DDR5将在DDR4基础上,在初期提供3,200 MT/s的传送速率,最高可达6,400 MT/s,预计未来将扩展到高达8,400 MT/s。

DDR5带来了一系列全新的挑战,在实现和检验时必须克服这些挑战。更高的数据速率会扩大要求的测试设备带宽,要求新的流程来测量之前的方法测量不了的抖动,要求接收机均衡形式的全新DDR单元,甚至要引入新的采用夹具的标准化测试,这些都是DDR5验证面临的重大挑战。

DDR5改进了性能,意味着要求更高性能的设备,来分析和测试DDR5赋能的器件。为满足这一性能需求,泰克开发了一种深入的解决方案,利用高带宽示波器和探头硬件,如DPO71604SX和P7716,同时采用全新的软件自动化平台。

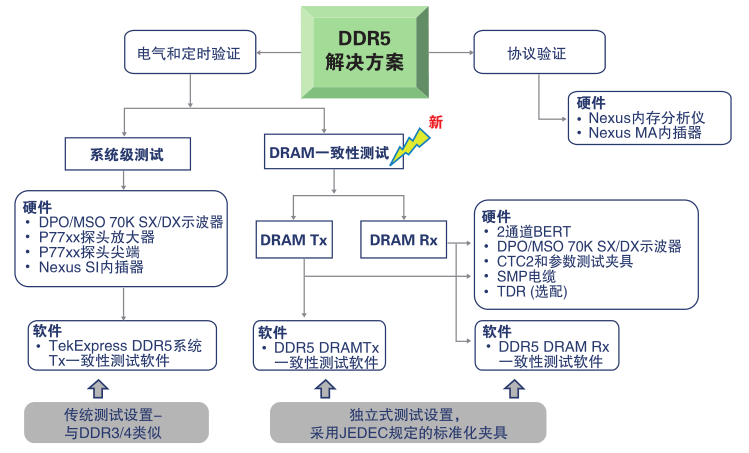

图1. DDR5测试解决方案中使用的泰克工具。

泰克TekExpress DDR发射机(Tx)软件是一种专门设计的自动测试应用,可以根据JEDEC (联合电子器件工程委员会)规范中规定的参数验证和调试DDR5器件。泰克选项DDR5SYS (TekExpress DDR Tx)包括以下全部测试覆盖范围和多种调试工具:

TekExpress DDR Tx支持根据DDR5 JEDEC规范测量50多种DDR5电气和定时参数。它内置多种强大的工具,协助进行表征和调试,如多选通功能、DDR5 DFE分析软件及用户可以全面控制测试条件的用户自定义采集模式。

泰克TekExpress DDR Tx解决方案拥有多种独特的创新功能,减少了测试中花费的工作量,加快了DDR系统和器件测试流程。TekExpress DDR Tx提供了一个简单的分步操作的简便易用的界面,加快了测试过程。

客户可以使用以下步骤,检验产品是否满足DDR5规范:

1. 把一只高阻抗泰克探头焊接到要测试的DDR子系统上,允许访问关心的电信号。

2. 泰克TekExpress DDR Tx软件分析探测到的信号,与DDR5规范进行对比。可以使用示波器上运行的其他软件,执行各种测试,如绘制眼图,测量相关电气参数。

图2是使用探头接入器件,执行系统级TX测试的一个实例。在这个实例中,片上系统(SOC)与被测器件(DRAM/RCD/ DB)通信,通过DDR总线传送双向业务。用户使用焊接在DRAM下面的内插器接入接口,使用高阻抗探头放大器探测接口。TekExpress DDR Tx软件为测量各种参数提供了必要的工具,如时钟抖动、读/写定时、甚至眼图。

图2. 系统级TX测试。

3. 测试结束时,会生成一份测试通过/未通过报告,提供与被测器件、物理设置、被测参数与JEDEC规范对比等详细信息。

4. 如果某项指标未通过测试,或发生非预期的结果,可以进一步使用TekExpress DDR软件解决方案调试结果。

信号传送速度不断提高和外形体积不断缩小,给下一代多千兆位设计和测试方法带来了多个挑战。外形越小,信号接入越难,得到的探测点会不理想,进而导致采集信号损耗和反射,因为理想的测量位置不存在阻抗断点。

DDR5的出现,使得DDR测试和调试以前采用的工具变得不够了。设计采用更高的数据速率,负载要求更加严格,顺利访问信号不能说不可能,但肯定会变得异常困难。解决这些问题的有效方法之一,是采用泰克串行数据链路分析(SDLA)软件包。通过SDLA功能,用户可以通过反嵌流程,消除测试设置(探头、内插器、电缆)的负载影响。不管是反射、插损、交叉耦合还是其他损伤,SDLA都提供了强大的功能,可以有效分析信号,就像这些效应不存在一样。这可以大大提高获得的测量的有效性和准确性,甚至会直接决定器件能否通过测试。

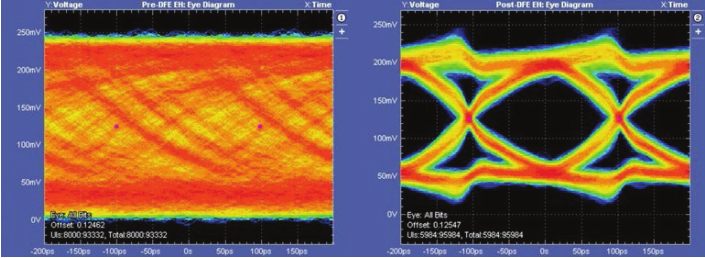

DDR中第一次以4阶DFE (判定反馈均衡)的形式引入接收机均衡。在访问和分析DDR5信号时,这带来了额外的挑战。例如,即使在反嵌后,生成的眼图可能仍会闭上(图3)。为了让眼图进一步张开,必需实现DFE均衡。

泰克开发了各种工具,帮助解决DFE在测试过程中引入的问题。可以使用SDLA,分析来自器件的连续数据流,从而训练DFE增益和阶值。然后可以使用DFE特点,输入TekExpress DDR Tx自动化软件,在突发信号上生成应用DFE之后的眼图。另外还可以使用独立式DFE应用(TekExpress DDR Tx标配),在自动化框架以外应用DFE均衡后,用户可以手动生成和查看DDR信号。

图3. 使眼图中的眼睛张开的实例。

DDR5对CLK、DQS和DQ提出了新的Rj/DJ抖动测量要求。此外,Rj指标大约在0.5ps (非常严格)。泰克开发了一种新的抖动噪底噪声校准技术,可以在泰克示波器上直接使用这种技术。该工具提供了一个选项,可以在噪声校准过程中包括探头、探头尖端和反嵌过滤器文件,考虑额外生成或放大的噪声。该工具全面集成示波器分析软件(DPOJET),从测量结果中消除示波器的噪声抖动。

随着业界转向DDR5开发、测试和生产,要求新的硬件和软件工具,来解决DDR5测试带来的最新挑战。泰克开发了一系列高带宽示波器和探头,从DDR5器件中采集信号,同时为验证开发了强大的软件工具。访问Tek.com进一步了解我们的解决方案,观看与DDR5和泰克解决方案有关的视频演示或网上研讨会。

最前沿的电子设计资讯

最前沿的电子设计资讯