所有现代数字逻辑都是由组合逻辑和时序逻辑组成的。组合逻辑由门电路(gate)组成,而时序逻辑则由触发器(flipflop)组成。不同的晶体管以特殊的方式连接在一起形成一个门电路,而连接不同门电路则形成一个触发器。无论是组合逻辑还是时序逻辑,任何芯片的基本单元都是晶体管。

现代芯片由数十亿个晶体管组成。例如,2021年10月发布的最新款 MacBook M1 max 处理器就是由约570亿个晶体管组成的。从晶体管的数量可以推断出,M1 max处理器所包含的门电路数就算没有数十亿至少也有数百万,这些门电路被仔细地建置于内存单元格中。以逻辑方式精心地将这些门电路互连在一起,就组成了功能强大的芯片。

整个芯片开发过程分为多个不同的阶段。首先是前端阶段,包括缓存器传输级(RTL)设计、设计验证和可测性设计(DFT)插入;然后是后端阶段,包括底层规划、频率树合成以及布局和布线。在RTL设计过程中,先编写芯片程序代码,然后进行仿真,接着合成设计,然后在RTL程序代码被固定的同时完成各种后端流程。

在芯片开发过程中很容易产生缺陷,因此为了确保芯片中的功能不受到影响,在投片之前修复这些缺陷十分重要。在像M1 max这样的芯片中,由于晶体管数量庞大,出现缺陷的机率就更大了。透过手动修改网表程序代码或使用Cadence Conformal或新思科技(Synopsys)的Formality等工具执行工程变更指令(ECO)可以在RTL固定后修复发现的缺陷。

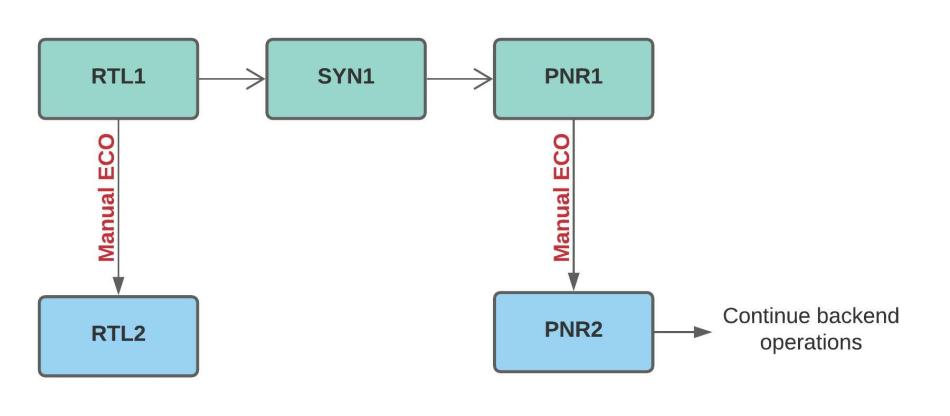

图1:手动执行ECO流程的实例。

对于小规模ECO来说,手动更改网表程序代码是有效的,但在较大规模ECO的情况下,使用EDA工具是更好的选择,因为它可以调整现有的逻辑等效检查(LEC)流程,以便自动执行整个ECO过程。本文将介绍半导体产业中广泛使用的光罩制作前(premask)平面型Conformal ECO流程。

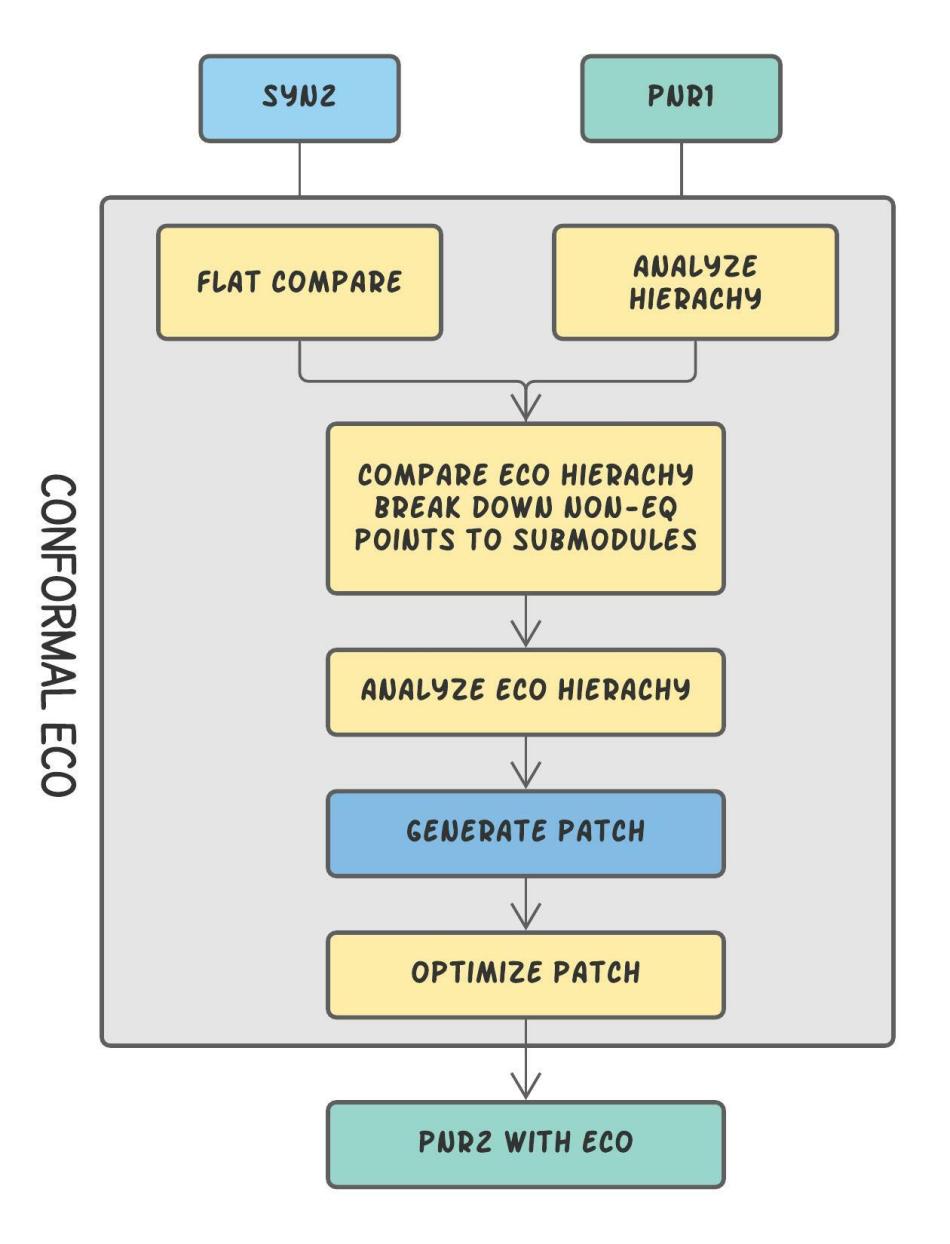

图2解释了使用Conformal执行的光罩制作前平面化ECO流程。在开始ECO流程之前,应该先执行特定的等效性检查。「逻辑等效检查」(LEC)可以直接检查修改后的设计,无需从测试台传递任何测试向量。这些检查比执行回归仿真更快,工程师经常在设计更改后使用这些方法来完成完整性检查。

图2:使用Conformal执行光罩制作前平面化ECO流程。

RTL1 – 未执行ECO的原始设计;

RTL2 – 执行ECO的修改后设计;

PNR1 – 未执行ECO且源自RTL1的布线后网表;

SYN2 – 执行ECO且源自RTL2的合成网表;

PNR2 – 执行ECO增补程序的布线后网表。

有关LEC及其流程的更多信息,请参见本系列文章的第一部份——「使用Conformal进行逻辑等效检查(LEC)入门电路」(A primer on logical equivalence checking (LEC) using Conformal)。

完成所有的初步检查后,将带有ECO的合成网表(SYN2)和原始的布线后网表(PNR1)一并提供给Conformal工具。这些网表分别称为改版设计和黄金设计。Conformal工具读取不同类型的优化,例如由合成工具执行的边界优化和分层频率门电路控,并在输入黄金网表和改版网表之间执行LEC。LEC会报告非等效点。这些非等效点都应该仔细审查,因为增补程序的产生取决于这些失败的关键点。

图3:使用Conformal执行光罩制作前平面化ECO过程的更多详细信息。

该工具会产生一个增补程序,我们可以将该增补程序应用到黄金设计——PNR1上,以获取新的带ECO的布线后网表(PNR2)。最后使用诸如Cadence Genus等合成工具及其提供的库信息完成增补程序优化。为了验证ECO增补程序并确保没有其他故障出现,需在SYN2和PNR2之间运行LEC,进而有望得到非等效关键点为零的成功结果。

如前所述,可以修改现有的LEC流程来适应ECO流程。在执行ECO的同时修改现有LEC流程的第一步是比较黄金设计和改版设计,计算它们之间的增量变化。这个增量又名增补程序,随后即被优化并应用于黄金网表。接着再次使用LEC比较带增补程序的黄金网表和带增补程序的合成网表以验证ECO。如果比较结果没有问题,那么ECO就算成功了。

简而言之,我们需要在ECO之前做三次等效检查,并在ECO期间进行两次等效检查。在ECO过程中的两次等效检查之间,可以透过以下指令产生、应用和优化增补程序:

产生指令:此指令产生分层增补程序。该工具还可以根据增补程序和接脚可用性添加/删除ECO接脚。

analyze_eco -hierarchical -ecopin_dofile ecopins.do patch.v -replace

set_system_mode setup

dofile ecopins.do

将增补程序应用于黄金设计:使用以下指令将产生的增补程序应用于黄金设计。

apply_patch -auto

优化指令:随后用提供的库信息和Genus合成工具优化增补程序。优化后增补程序中的实例、网络和缓存器的命名可以透过适当的参数进行控制。

optimize_patch -workdir <working_directory>

-library <lib_file_list>

-sdc <sdc_filename>

-instancenaming “ECOinst_%d”

-netnaming “ECOnet_%d”

-sequentialnaming “ECOreg_%s”

-synexec “genus”

-verbose

在RTL固定后,执行ECO可以发现设计中的缺陷并最终得到解决。手动修改网表程序代码可能是一个耗时且麻烦的过程。相较于手动执行ECO,使用Conformal或Formality等EDA工具可以实现整个ECO流程的自动化,并且速度更快,往往还能提供更好的结果。由于Conformal ECO流程利用了现有的LEC流程,因此在某些情况下可显着减少整个ECO的工作量。

(参考原文:A primer on engineering change order (ECO) using Conformal,by Deekshith Krishnegowda)

最前沿的电子设计资讯

最前沿的电子设计资讯