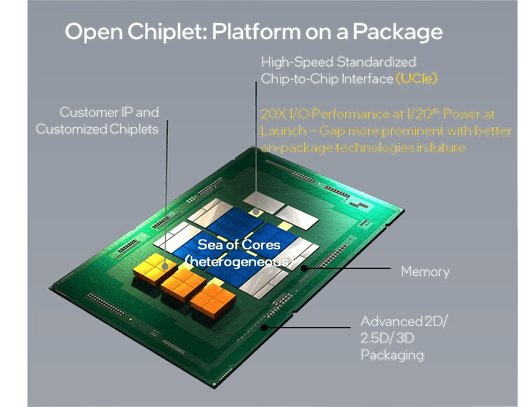

EDN小编第一次听说小芯片(Chiplet)是在2020年,当时是zGlue的开放芯片计划(Open Chiplet Initiative),该计划将不同供应商的IP或芯片集成到一个芯片上,无论是简单地将以前的单片 CPU 拆分成几块,还是将47 个小芯片放在一个封装上,小芯片当下的芯片设计中发挥着重要作用。上个月,随着英特尔对“开放芯片平台”的投资,Chiplet又回到了风口浪尖。

美国时间3月2日, 英特尔、AMD、Arm 和所有领先的代工厂商齐聚一堂,包括高通、三星、台积电、日月光,以及Google Cloud、Meta、微软,宣布他们正在为小芯片互连制定一个新的开放标准Universal Chiplet Interconnect Express (UCIe),希望以UCIe 1.0规范建立芯片互连、兼容运作,让更多业者能依照此标准打造新款处理器,并且能配合不同微芯片建构差异化设计。

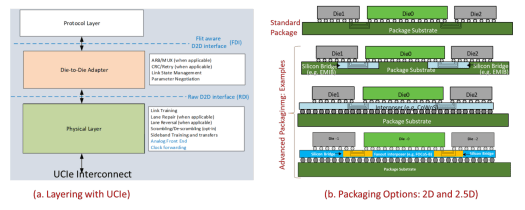

UCIe 1.0规范涵盖芯片到芯片的I/O端口实体层,以及芯片到芯片之间互连协议与软体堆叠设计,通过成熟发展的PCI Express (PCIe),以及CXL (Compute Express Link)连接协议对应更快数据传输效率,未来还将在规范中添加更多协议。

目标是提供混合和匹配来自不同晶圆厂、不同设计/架构和不同封装技术的封装芯片的能力。Universal Chiplet Interconnect Express表示,该计划旨在满足云、边缘、企业、5G、汽车、高性能计算和手持领域中计算、内存和存储的预计增长需求。

UCIe支持两种广泛的使用模式。第一种是封装级集成,以提供高功率和高性价比的性能,如图5a所示。连接在板级上的组件如内存、加速器、网络设备、调制解调器等,可以在封装层面上进行集成。适用于从手持设备到高端服务器,并通过不同的封装方案将来自多个来源的芯片连接起来甚至在同一个封装上通过不同的封装选项连接。第二种用途是利用UCIe提供非包装连接,使用不同类型的介质(如光缆、电线、毫米波)。

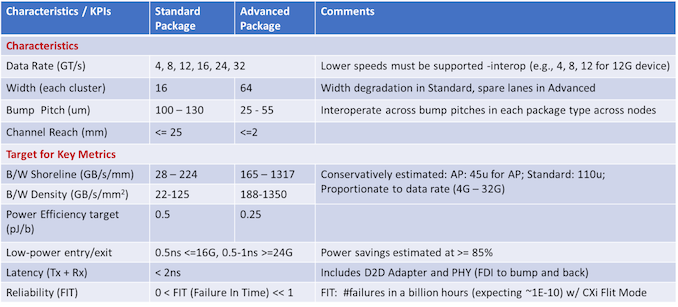

关于 UCIe 的白皮书还提到了高带宽、低延迟、节能和具有成本效益的封装连接。

UCIe支持不同的数据速率、位宽、凸点间距和信道范围,以确保最广泛的互操作性。上表1中详细列出了最广泛的互操作性。它定义了一个边带接口,便于设计和验证。互联的结构单元是一个集群,包括N个单端、单向、全双工的数据通道(标准封装的N=16,高级封装的N=64)。

多年来,已经有来自不同供应商的 IP 的 SoC,例如,Arm 内核通常与 Imagination 或 Vivante GPU 结合,但新标准应该会让它变得更容易,可以说,UCIe的发布打通了Chiplet未来发展障碍,对于推动Chiplet有历史性的意义,未来我们可能会看到越来越多的芯片混合 x86、RISC-V和/或 Arm 以及其他 IP。

最前沿的电子设计资讯

最前沿的电子设计资讯