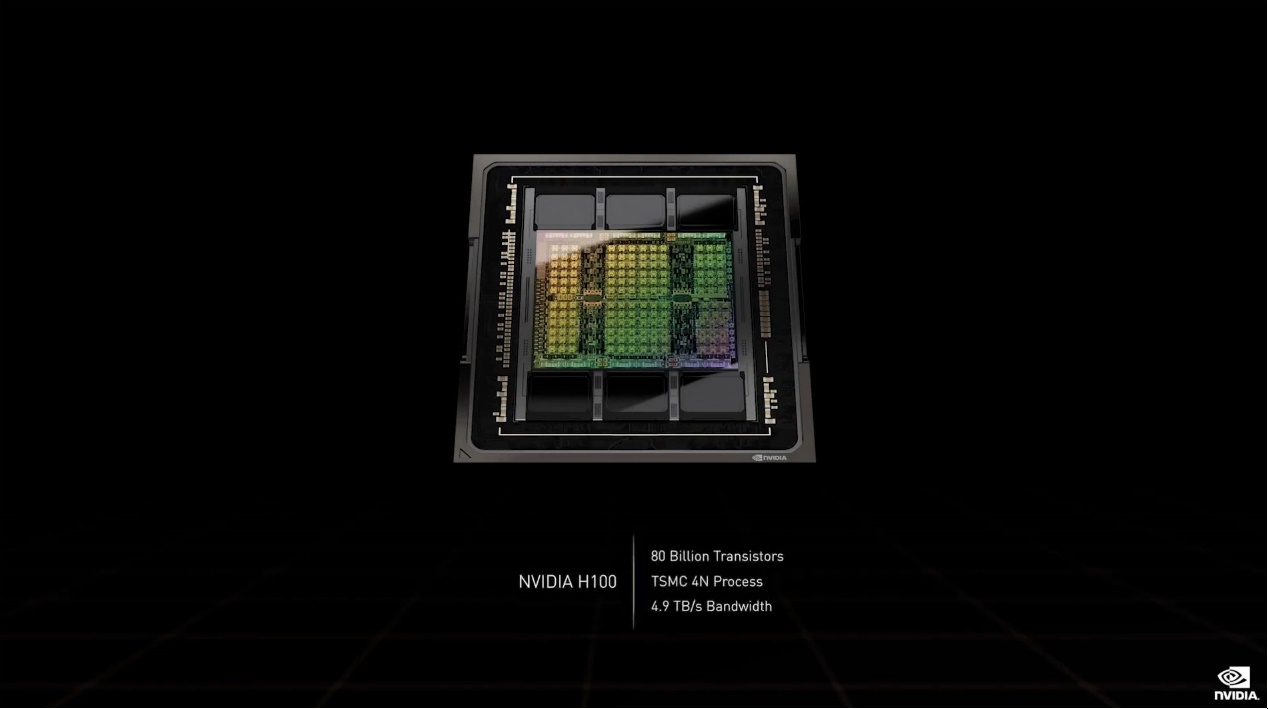

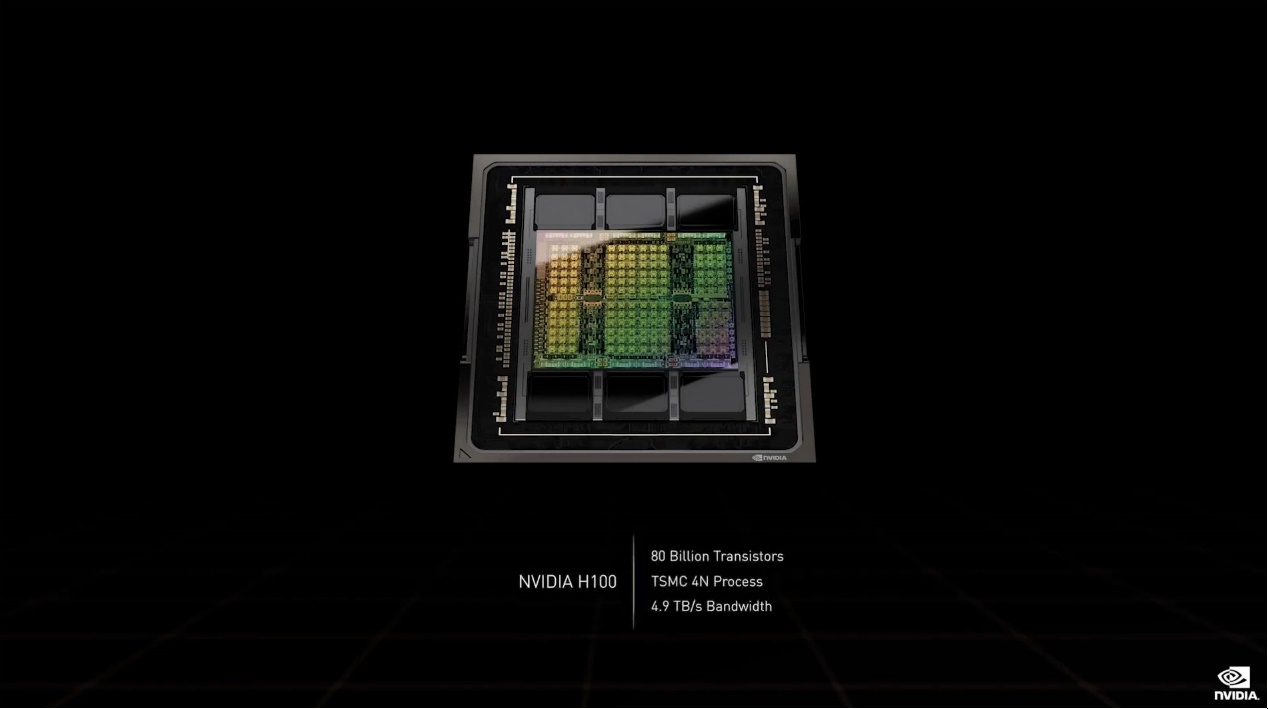

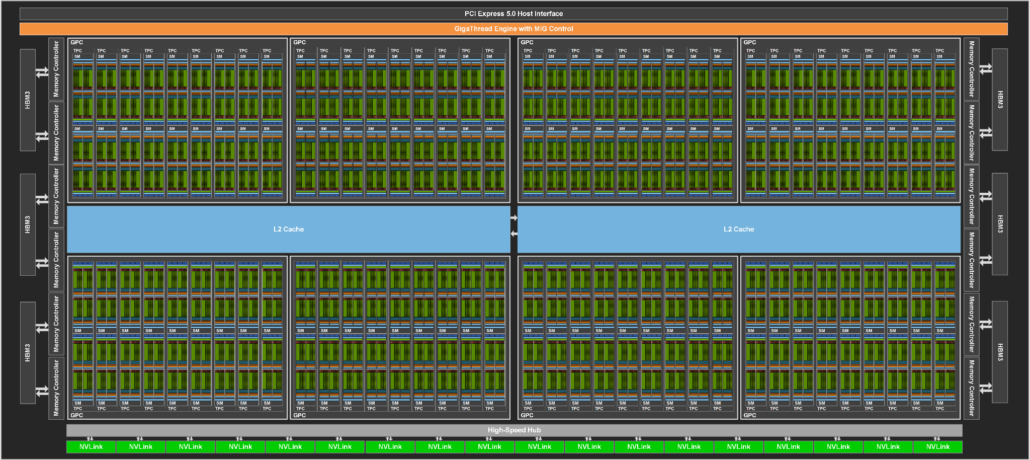

英伟达正式推出了其新一代架构与核心Hopper GH100 GPU,它采用全新的定制版台积电 4nm 工艺, CoWoS 2.5D晶圆级封装,单芯片设计,集成多达800亿个晶体管,号称世界上最先进的芯片。tdbednc

4nm工艺、800 亿个晶体管、地球上最快的 AI/计算产品

基于 Hopper 架构的 Hopper GPU 是在尖端台积电 4nm 工艺节点上生产的工程奇迹。就像之前的数据中心 GPU 一样,Hopper GH100 将针对各种工作负载,包括人工智能 (AI)、机器学习 (ML)、深度神经网络 (DNN) 和各种以 HPC 为重点的计算工作负载。tdbednc

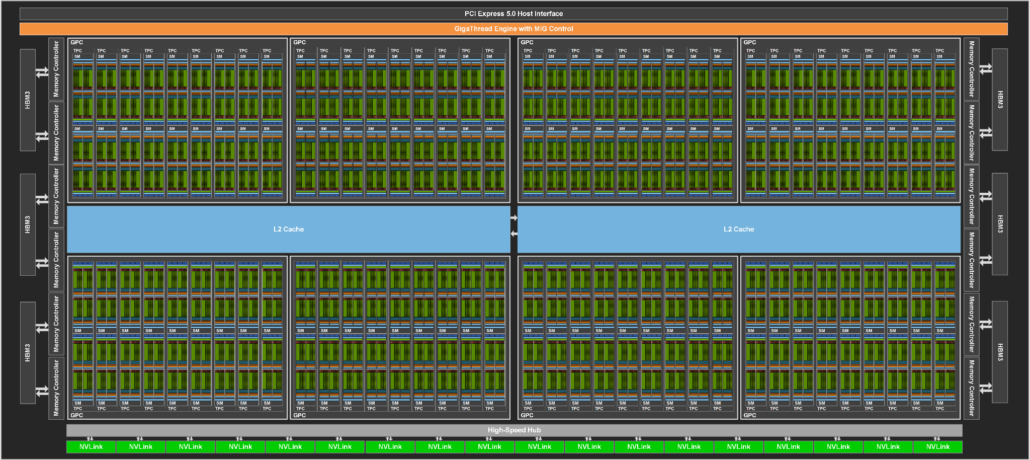

完整版有8组GPC(图形处理器集群)、72组TPC(纹理处理器集群)、144组SM(流式多处理器单元),而每组SM有128个FP32 CUDA核心,总计18432个。tdbednc

显存支持六颗HBM3或者HBM2e,控制器是12组512-bit,总计位宽6144-bit。tdbednc

Tensor张量核心来到第四代,共有576个,另有60MB二级缓存。tdbednc

扩展互连支持PCIe 5.0、NVLink第四代,后者带宽提升至900GB/s,七倍于PCIe 5.0。整卡对外总带宽4.9TB/s。tdbednc

tdbednc

tdbednc

tdbednc

tdbednc

tdbednc

tdbednc

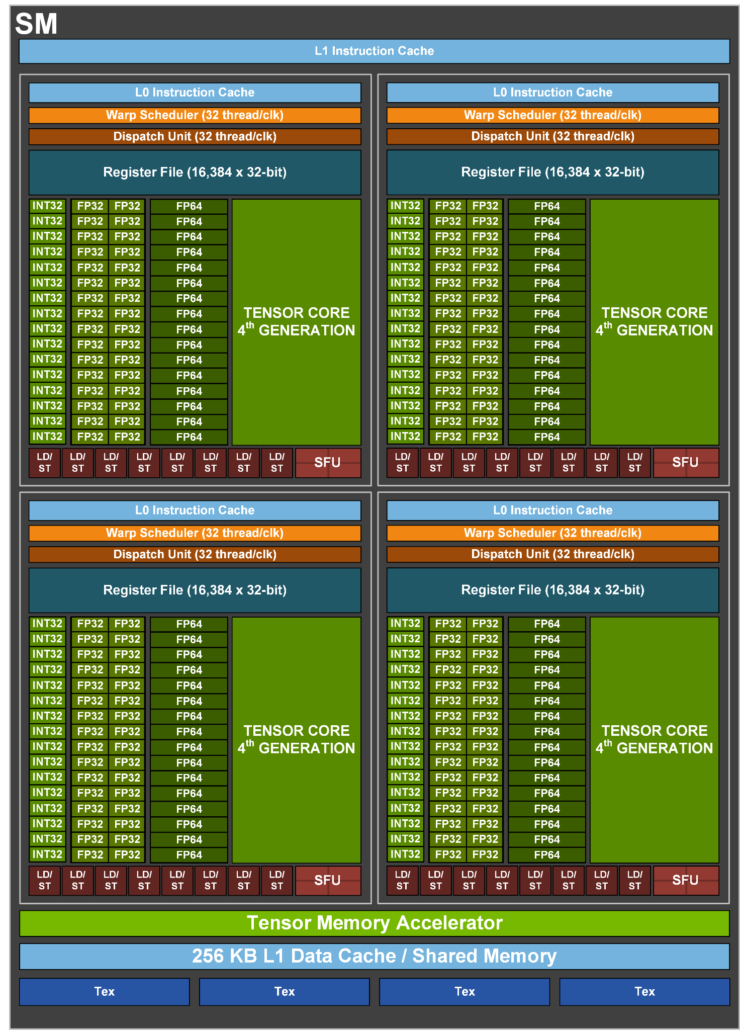

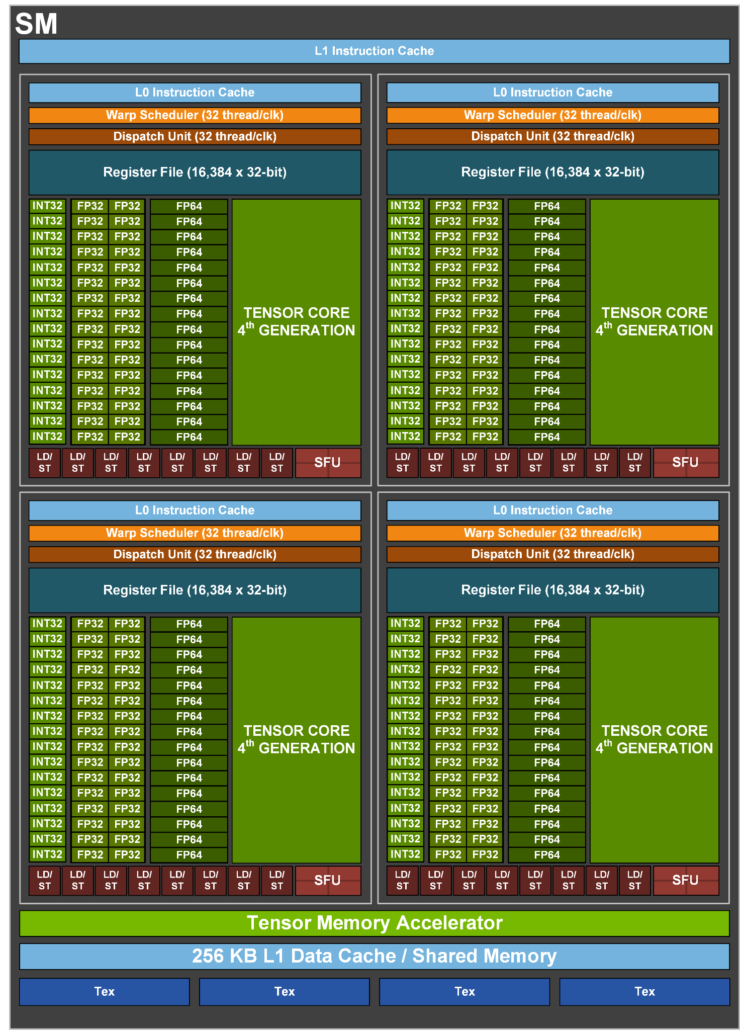

144组SM(流式多处理器单元)有哪些改进?

新的流式多处理器 (SM) 具有许多性能和效率改进。主要新功能包括:tdbednc

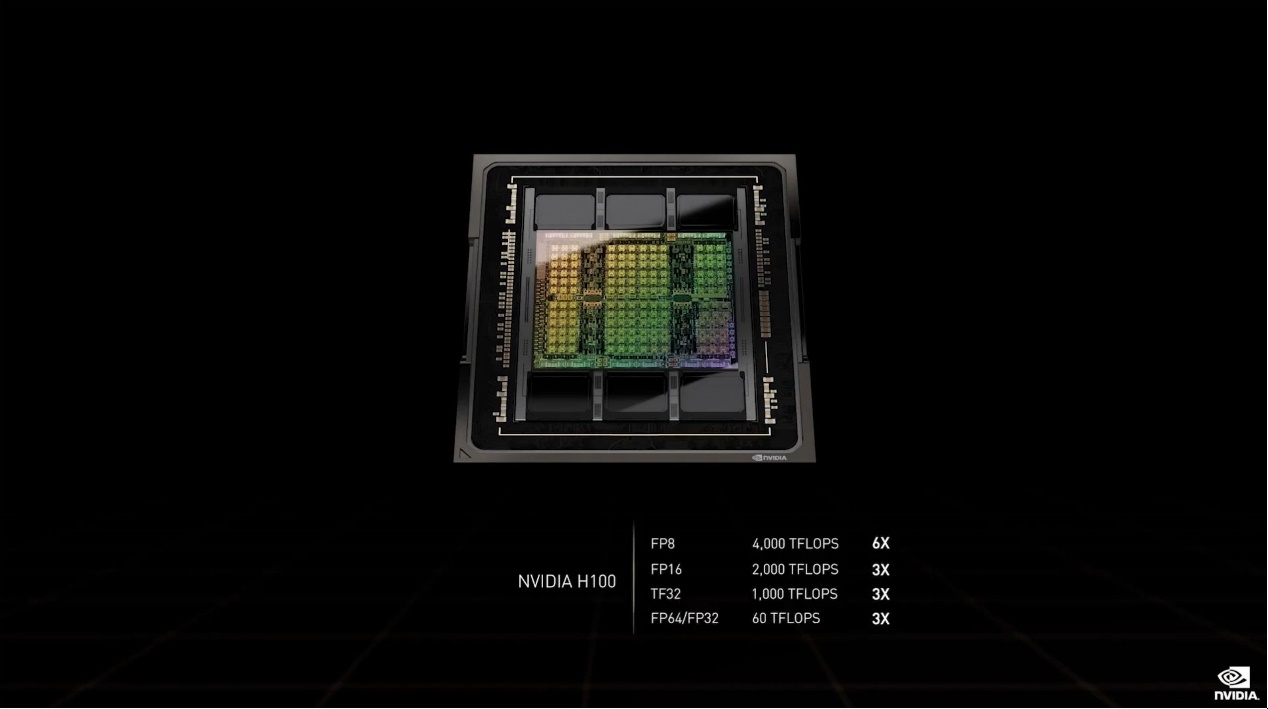

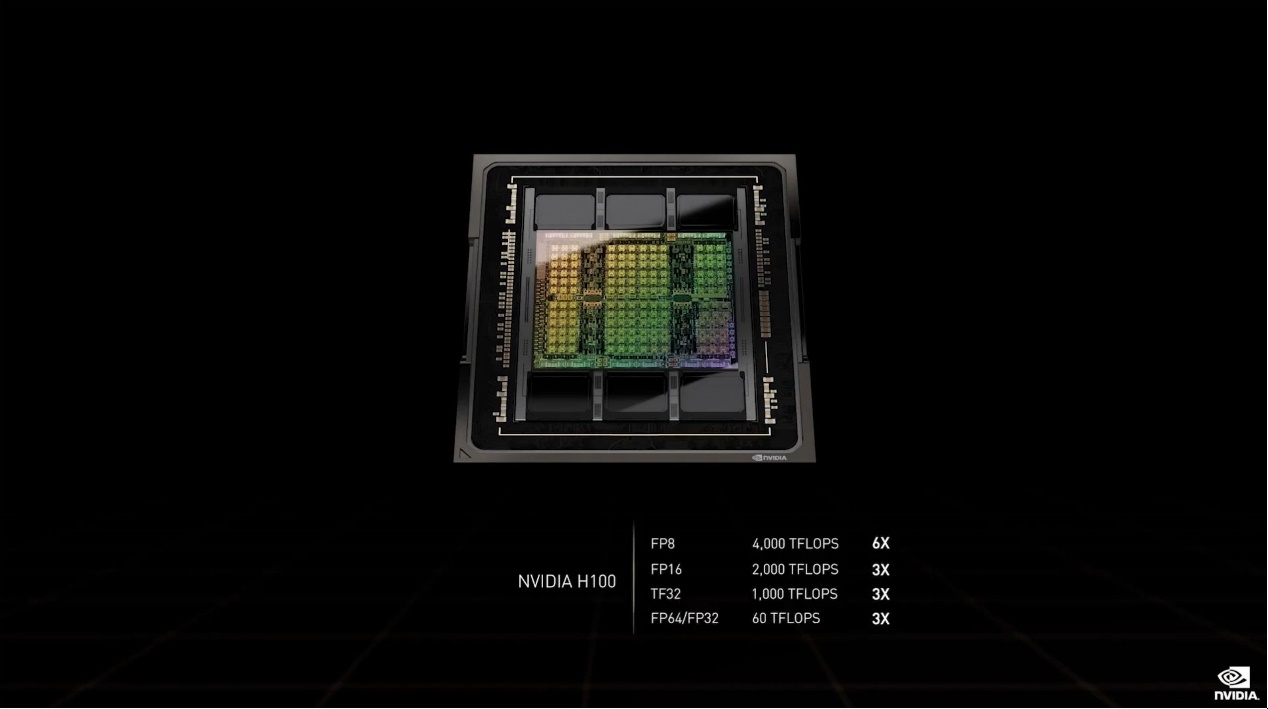

- 与 A100 相比,新的第四代 Tensor Core 的芯片到芯片速度提高了 6 倍,包括每个 SM 的加速、额外的 SM 数量和 H100 的更高时钟。在每个 SM 基础上,与上一代 16 位浮点数相比,Tensor Core 在等效数据类型上的 MMA(矩阵乘累加)计算速率是 A100 SM 的 2 倍,在使用新的 FP8 数据类型时是 A100 的 4 倍点选项。稀疏性功能利用深度学习网络中的细粒度结构化稀疏性,将标准张量核心操作的性能提高一倍。

- 新的 DPX 指令将动态编程算法的速度提高了 A100 GPU 的 7 倍。两个示例包括用于基因组学处理的 Smith-Waterman 算法,以及用于为机器人车队在动态仓库环境中寻找最佳路线的 Floyd-Warshall 算法。

- 与 A100 相比,芯片到芯片的 IEEE FP64 和 FP32 处理速率快 3 倍,因为每个 SM 的时钟对时钟性能提高了 2 倍,加上额外的 SM 计数和 H100 的更高时钟。

- 新的线程块集群功能允许以大于单个 SM 上的单个线程块的粒度对局部性进行编程控制。这通过向编程层次结构添加另一个级别来扩展 CUDA 编程模型,现在包括线程、线程块、线程块集群和网格。集群使多个线程块在多个 SM 上同时运行,以同步和协作获取和交换数据。

- 新的异步执行功能包括一个新的张量内存加速器 (TMA) 单元,它可以在全局内存和共享内存之间非常有效地传输大块数据。TMA 还支持集群中线程块之间的异步复制。还有一个新的异步事务屏障用于进行原子数据移动和同步。

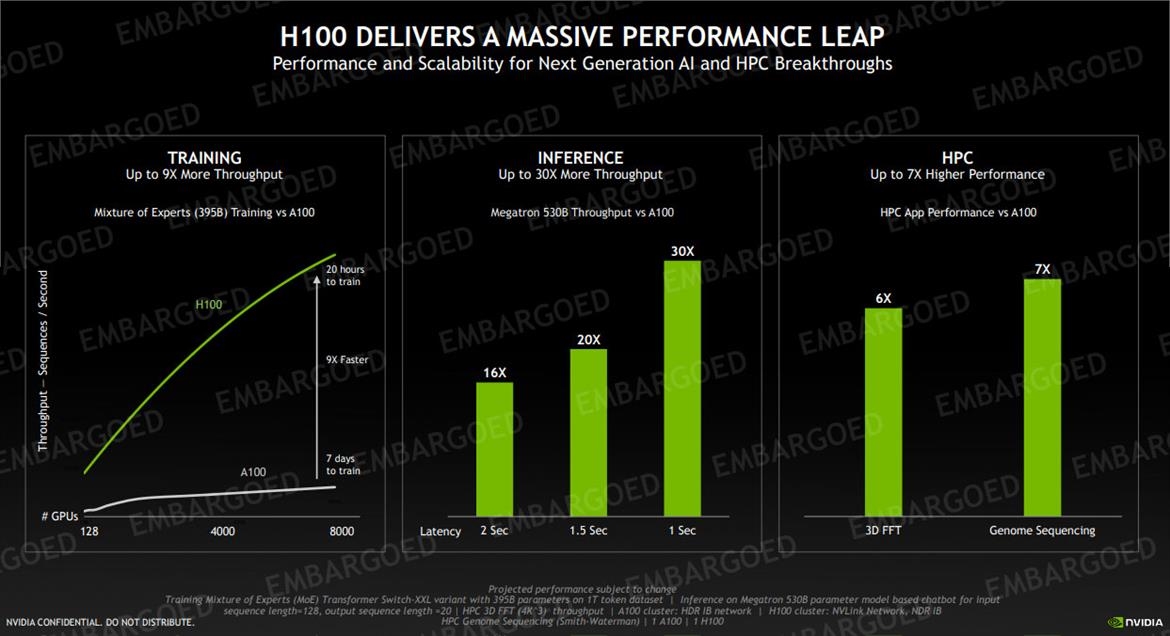

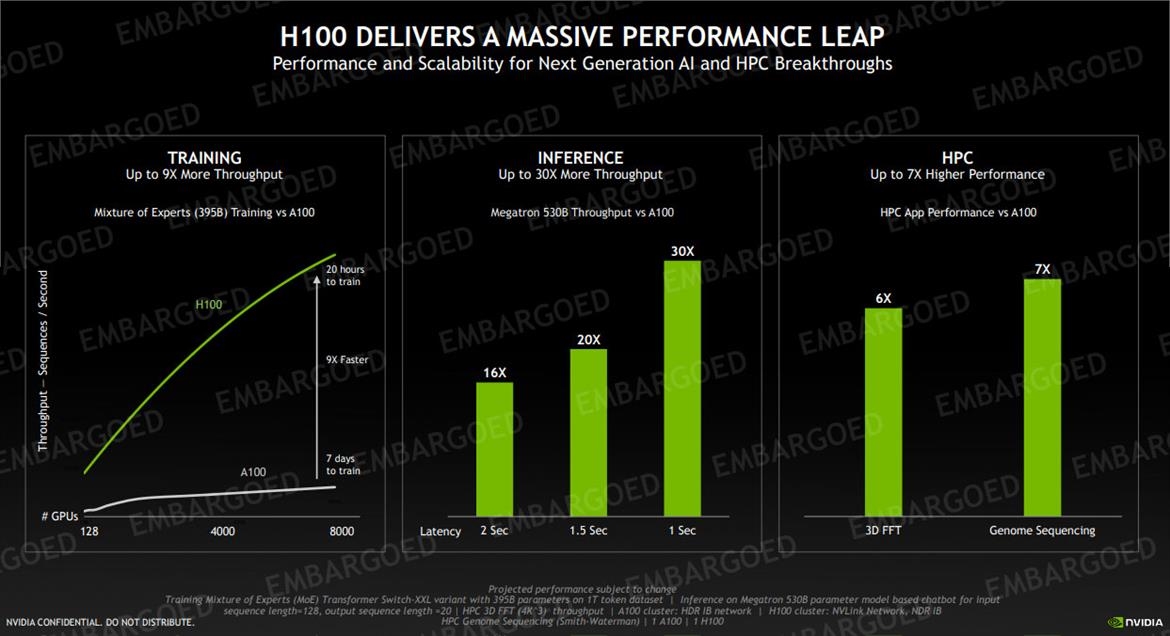

- 新的 Transformer Engine 结合了软件和定制的 Hopper Tensor Core 技术,专门用于加速 Transformer 模型的训练和推理。Transformer 引擎智能管理并在 FP8 和 16 位计算之间动态选择,自动处理每层 FP8 和 16 位之间的重铸和缩放,以提供高达 9 倍的 AI 训练速度和高达 30倍的人工智能推理加速与上一代 A100 相比的语言模型。

- HBM3 内存子系统提供的带宽比上一代增加了近 2 倍。H100 SXM5 GPU 是世界上第一款配备 HBM3 内存的 GPU,可提供一流的 3 TB/秒内存带宽。

- 50 MB L2 缓存架构可缓存大部分模型和数据集以供重复访问,从而减少对 HBM3 的访问。NVIDIA H100 Tensor Core GPU 架构与 A100 的比较。现在首次提供具有 MIG 级可信执行环境 (TEE) 的机密计算功能。最多支持七个单独的 GPU 实例,每个实例都有专用的 NVDEC 和 NVJPG 单元。现在,每个实例都包含自己的一组与 NVIDIA 开发人员工具配合使用的性能监视器。

- 新的机密计算支持可保护用户数据,防御硬件和软件攻击,并在虚拟化和 MIG 环境中更好地隔离和保护 VM。H100 实现了世界上第一个原生机密计算 GPU,并以全 PCIe 线速使用 CPU 扩展了可信执行环境。

- 与上一代 NVLink 相比,第四代 NVIDIA NVLink® 在 all-reduce 操作上的带宽增加了 3 倍,一般带宽增加了 50%,多 GPU IO 的总带宽为 900 GB/秒,其带宽是 PCIe Gen 5 的 7 倍。

- 第三代 NVSwitch 技术包括位于节点内部和外部的交换机,用于连接服务器、集群和数据中心环境中的多个 GPU。节点内的每个 NVSwitch 提供 64 个第四代 NVLink 链路端口,以加速多 GPU 连接。总交换机吞吐量从上一代的 7.2 Tbits/sec 增加到 13.6 Tbits/sec。新的第三代 NVSwitch 技术还通过多播和 NVIDIA SHARP 网络内减少为集体操作提供硬件加速。

- 新的 NVLink 交换机系统互连技术和基于第三代 NVSwitch 技术的新的二级 NVLink 交换机引入了地址空间隔离和保护,使多达 32 个节点或 256 个 GPU 能够通过 NVLink 以 2:1 锥形肥树拓扑连接. 这些连接的节点能够提供 57.6TB/秒的全对全带宽,并且可以提供令人难以置信的 FP8 稀疏 AI 计算的 exaFLOP。

- 第 5 代 PCIe 提供 128 GB/秒的总带宽(每个方向 64 GB/秒),而第 4 代 PCIe 中的总带宽为 64 GB/秒(每个方向 32 GB/秒)。PCIe Gen 5 使 H100 能够与性能最高的 x86 CPU 和 SmartNIC / DPU(数据处理单元)连接。

因此,按照规格,NVIDIA Hopper GH100 GPU 由一个巨大的 144 SM(流式多处理器)芯片布局组成,总共有 8 个 GPC。这些 GPC 共有 9 个 TPC,每个 TPC 进一步由 2 个 SM 单元组成。这使我们每个 GPC 有 18 个 SM,而在完整的 8 个 GPC 配置中,我们有 144 个。每个 SM 最多由 128 个 FP32 单元组成,这应该给我们总共 18,432 个 CUDA 内核。tdbednc

tdbednc

tdbednc

第 4 代 NVIDIA Hopper GH100 GPU SM(流式多处理器)的一些主要特性包括:tdbednc

- 与 A100 相比,芯片到芯片的速度提高了 6 倍,包括每个 SM 的加速、额外的 SM 数量和 H100 的更高时钟。

- 在每个 SM 的基础上,与上一代 16-位浮点选项。

- 稀疏性特征利用深度学习网络中的细粒度结构化稀疏性,将标准张量核心操作的性能提高一倍。

- 新的 DPX 指令将动态编程算法的速度提高了 A100 GPU 的 7 倍。两个示例包括用于基因组学处理的 Smith-Waterman 算法,以及用于为机器人车队在动态仓库环境中寻找最佳路线的 Floyd-Warshall 算法。

- 与 A100 相比,芯片对芯片的 IEEE FP64 和 FP32 处理速率快 3 倍,因为每个 SM 的时钟对时钟性能提高了 2 倍,加上额外的 SM 计数和 H100 的更高时钟。

- 256 KB 的组合共享内存和 L1 数据缓存,比 A100 大 1.33 倍。

- 新的异步执行功能包括一个新的张量内存加速器 (TMA) 单元,它可以在全局内存和共享内存之间高效地传输大块数据。TMA 还支持集群中线程块之间的异步复制。还有一个新的异步事务屏障用于进行原子数据移动和同步。

- 新的线程块集群功能公开了跨多个 SM 的局部性控制。

- 分布式共享内存允许跨多个 SM 共享内存块的负载、存储和原子直接 SM 到 SM 通信。

tdbednc

tdbednc

责编:Demi

最前沿的电子设计资讯

最前沿的电子设计资讯