对DAC可能最重要的动态指标是噪声、毛刺脉冲、失真和无杂波动态范围(SFDR)等等。本文将以数据转换器行业全球领导半导体厂商亚德诺半导体(ADI)的相关代表产品为基础,重点阐述如何提高精密DAC价值的主要动态性能规格,以及介绍精密DAC输出端噪声的性质和来源,同时说明一些动态性能规格,这些规格在某些应用中可能非常关键。

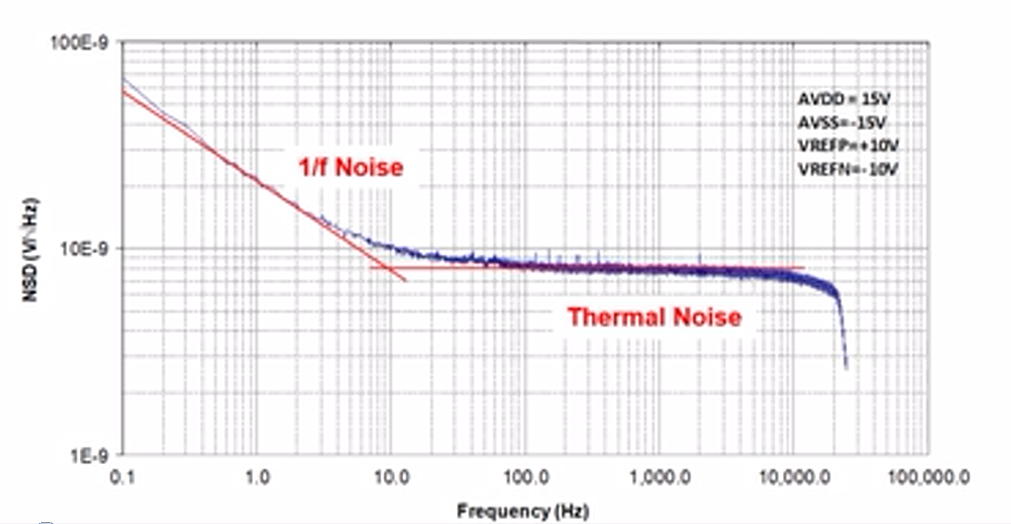

查看精密DAC数据手册时,噪声一般可以通过一种或两种方式加以规定。输出噪声和频谱密度通常是在1kHz和10kHz下进行测量,单位为nV/√Hz,输出电压噪声或1/f噪声是电压峰峰值噪声测量结果。在输出噪声频谱密度是指噪声能量相对于频率的关系,频谱密度的噪声由两个噪声源——1/f噪声和热噪声组成。1/f噪声也称为闪烁噪声或粉红噪声,它产生的原因有器件的性质和工艺杂质,没有一个通用公式来定义该噪声;热噪声也称为约翰逊噪声或电阻噪声,并该噪声由热电子扰动产生,该噪声与阻值成比例,如幻灯片中公式所示,在特定频率,所有其他项都是恒定的,因此噪声与阻值成比例。

该图代表亚德诺半导体公司(ADI)高精度数据转换器AD5780系列的噪声频谱密度,这些是16位、18位和20位分辨率精密器件,此低噪声性能对于实现精确的线性性能具有至关重要的原因,本质上,噪声必须低于最小电压阶跃或LSB。AD5780系列基于R-2R内核,R-2R梯形网络架构是降低热噪声的最佳DAC内核,因为它能最大程度地降低主要噪声源——输出阻抗。在本例中,噪声为8nV/√Hz,非常适合高精度超稳定应用,该图显示了最高10Hz的1/f噪声区域和更高频率下的热噪声。仅在01Hz至10Hz频率范围内测量,所示曲线为AD5780 18位DAC的峰峰值噪声,输出电压噪声峰峰值为11μV。

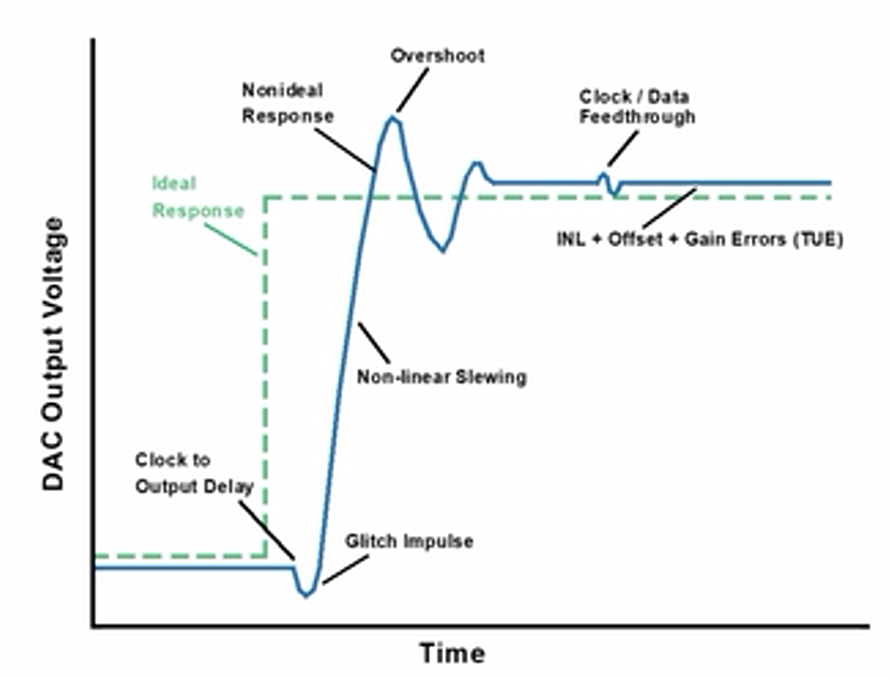

理想DAC会从一个电平立即精确地转换到另一个电平,然而,实际的DAC并不具有这种理想特性。在载入新代码后到输出开始变化有一个延迟,输出过渡到新的电平需要时间,这取决于压摆率。输出可能立即停止在最终值,在稳定之前,它可能会过冲和振荡,这同样取决于负载。

建立时间是指从编程要求输出更新到输出建立在最终值的+/-0.5LSB范围内所需的时间。例如,这可以从最后一个时钟沿或片选信号的上升沿开始计算,输出最终建立值是在器件的TUE范围内,该图中的绿色虚线显示了DAC输出的理想零阶全阶跃响应,以及一个更典型的输出,蓝线显示了可观测到的一些误差。

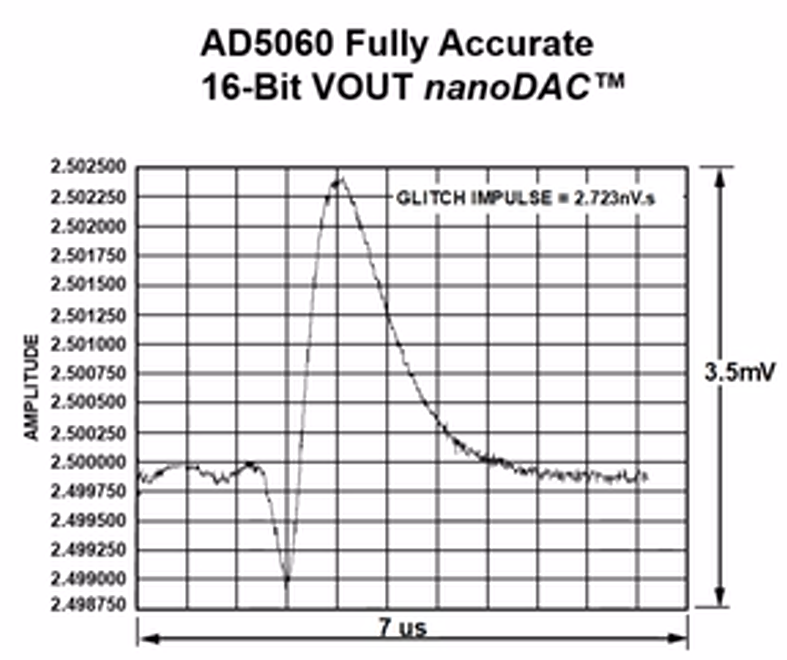

DAC误差可分为静态和动态两类。在输出建立到新值后可观测到静态误差,它通常是由元件不匹配引起的,导致线性特性不理想或增益误差。低频无杂散动态范围性能可能与DC线性度性能密切相关,还会影响较高频率下的小信号无杂散动态范围。动态误差发生在码跃迁期间,通常取决于步长,在较高输出频率下,这些误差通常占主导地位。压摆率衡量输出的变化速度,因为输出变化的初始阶段和最终阶段可能是非线性的,因此在输出转换的线性区域内测量压摆率。大多数压摆率测量是在¼和3/4量程之间的线性区域进行的,因为这样就消除了任何可能的上裕量和下裕量问题。压摆率的单位为V/μS时,该曲线显示了压摆率为2.5V/μs的AD5380 40通道电压输出DAC的输出响应的斜率。毛刺是指从一个代码转换到另一个代码时输出端观察到的瞬态响应。最大毛刺通常发生在主要代码转换时,从01111到10000或相反,这是因为该代码转换会使所有内部开关改变状态。

现在,DAC所有后续代码转换处的特性数据都会被收集,毛刺用nV-s表示,即瞬态响应的面积。AD5060 nanoDAC的额定毛刺小于3nV-s,另外,其额定峰峰值幅度小于3.5mV,需要强调的是,毛刺的持续时间非常短,虽然很容易在示波器上观察到,但最终应用的响应时间可能会导致慢得多,因此毛刺对于系统是不可见的。实际上,一些系统的延迟可能主要是由PID控制算法引起的,其持续时间可能达数百毫秒。

这就是数据手册中的技术规格表示例。在技术规格表上方,在我们给出了保证性能规格的条件,器件经过生产测试,满足给出的条件,这一部分条件通常会给出电源范围和负载条件。静态性能部分包含INL、DNL、主要直流线性度等信息,这里提供总非调整误差特性。在脚注部分很重要,通常指出了器件的温度范围,需要进行阅读。

现在大家知道了,详细了解了DAC技术规格有助于用户更好地选择DAC以实现最佳系统性能。在直流性能方面,分辨率或DNL对闭环系统更为重要。而精度或INL则对开环系统更为重要。总非调整误差更真实地反映了器件性能,比简单地将最差情况下的最大误差源相加更靠谱。1/f噪声,即闪烁噪声或粉红噪声,产生的原因有器件的性质和工艺杂质,没有通用公式来定义这种噪声,而热噪声,也称为约翰逊噪声或电阻噪声,是由热电子扰动产生的。此类噪声与DAC的电阻成比例。毛刺持续时间通常非常短,比系统响应的建立时间快,因此其影响极小。

最前沿的电子设计资讯

最前沿的电子设计资讯