除了讨论 PFC 级的开发之外,本系列文章的第三部分 [3]还提供了更广泛的概述,说明为什么仿真在电力电子设计中至关重要,以及在运行仿真之前要考虑的主要因素,例如目标、模型和输入参数。牢记这些因素将有助于成功的项目开发和执行。下面将介绍 DAB-PS 级电源仿真的关键信息。

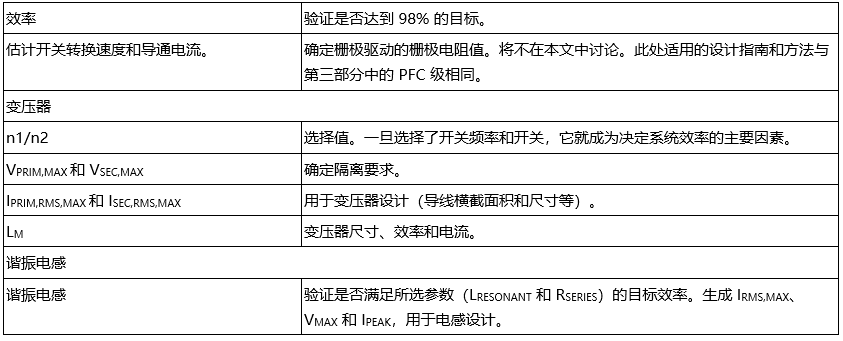

以验证系统的目标效率为主要目标,并由此帮助选择变压器和谐振电感的参数,在实现效率最大化的同时满足系统的其余要求。表 3 概述了主要目标。

表 3.仿真的主要目标摘要。

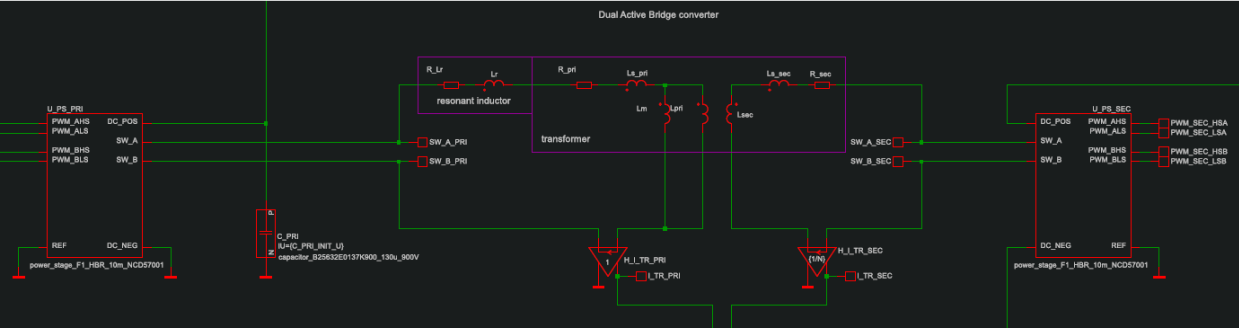

安森美半导体工程团队为 DC-DC 转换器开发的 SPICE 功率仿真模型如图 2 所示。与第三部分中介绍的三相 PFC 级的电源仿真模型相比,它更简单,前者对三个半桥进行开关,需要同步交流电网电流和电压。在 DAB-PS 转换器中,电源级使用四个半桥单元(与 PFC 模型中使用的模块相同)。至于变压器和谐振电感,该模型包含:Lpri 与 Lsec 的耦合比 (K = 1)、Lm(励磁电感)、Ls(次级电感)、Lr(谐振电感)和等效串联电阻(适用于变压器和电感绕组)。须强调的是,变压器和电感的磁芯损耗并未包含在内。在这一级中,考虑这些因素的可行起点是估计该损耗与传导损耗近似。

模型中的其他元件包括 C_Pri 和电压电流传感器(SPICE 格式),用于测量初级和次级电流以实现磁通平衡。C_Pri 代表在 DAB-PS 输入端使用的缓冲电容,并与直流链路并联。此类电容应靠近 MOSFET 放置,以抑制开关节点上出现的电压尖峰。

在最终产品实现中,可能不需要这些电容,或者其规格要小得多,因为 PFC 的直流链路部分已经提供了滤波功能。然而,就本项目的目的而言,DAB-PS 应作为一个独立系统正常工作,进行独立评估,因此该电容必不可少。如前所述,该控制模型采用了 50% 单相移工作的定制数字 PWM 模型。

图 2:DAB 转换器的仿真模型。

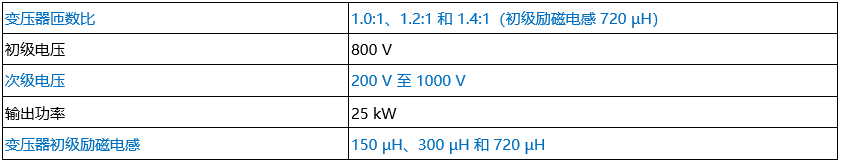

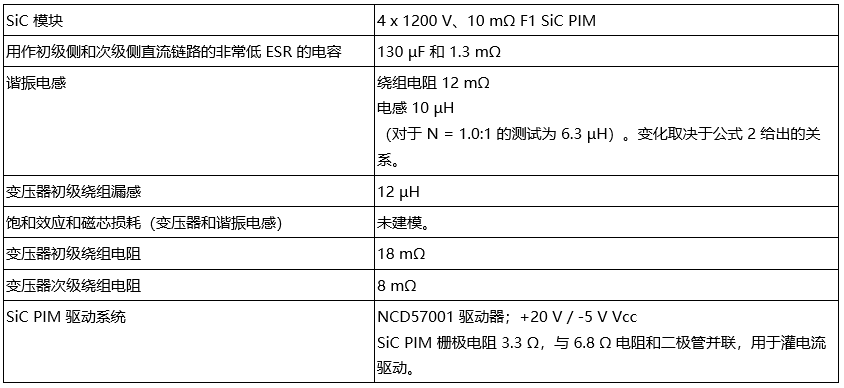

表 4 和表 5 概述了仿真输入参数。将使用 n1/n2、LM 和 VSEC 的替代值进行评估并最终确定最佳配置。其余参数在所有仿真中保持不变,根据我们工程团队在无源元件设计方面的专业知识、现有解决方案的基准和围绕该主题的文献,选择这些参数,以作为起点。

表 4.仿真输入参数。以蓝色突出显示的是在仿真中会发生变化的参数。

表 5.SPICE 仿真的配置。

本章节讨论仿真获得的结果。测试可分为两个主要评估,第一个评估围绕变压器匝数比 n1/n2 和效率,第二个评估围绕 LM。测试结果将有助于实现前面提出的目标并回答关键的设计问题。请注意,除非另有说明,否则所有仿真均在“输入参数”部分中提供的数值下执行。

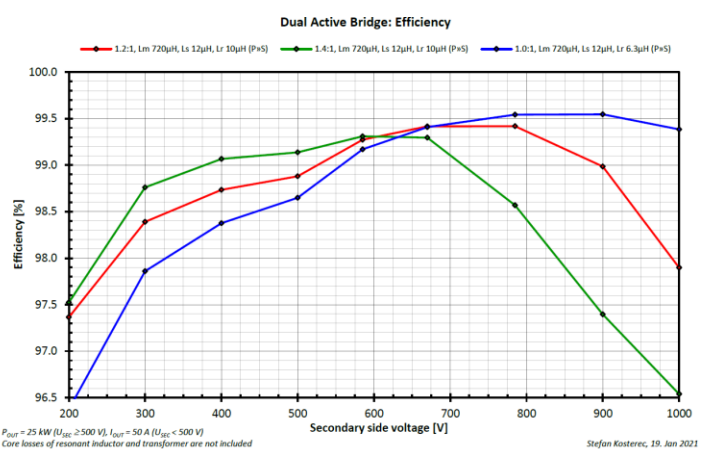

仿真的第一个结果和最具代表性的结果如图 3 和 4 所示。根据不同的 n1/n2 配置,分别在 800 V、666.7 V 和 571 V 次级工作电压下提供峰值效率。在此值得注意的是,在 340 V 至 830 V 的 VSEC 工作电压范围内,所有评估的匝数比都可实现 98% 的峰值效率(但不包括电感和变压器的磁芯损耗)。

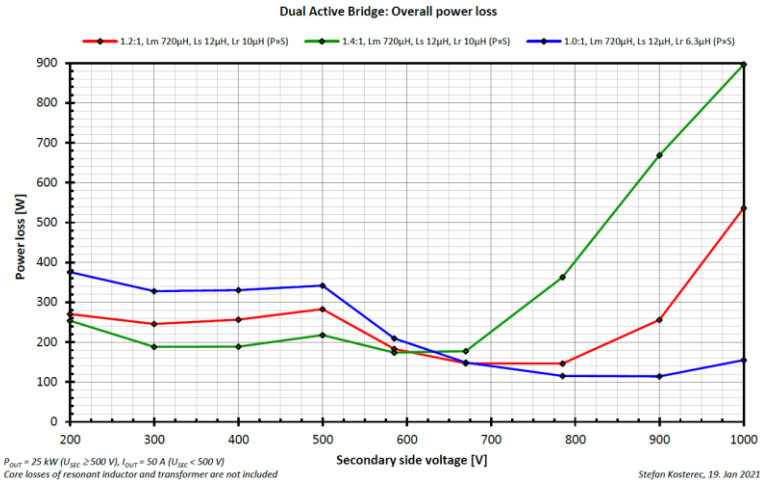

然而,随着 VSEC 向低端 (200 V) 和高端 (1000 V) 移动,不同 n1/n2 比值之间的差异会变得更明显。实际 VSEC 值偏离最佳点越远,效率就越差(图 3 中曲线图的左右两端)。有趣的是,虽然增加 n1/n2 会显著增加 VSEC > VSEC,OPTIM 时的总功率损耗(图 4 的右端),但减小 n1/n2 并不会对 VSEC < VSEC,OPTIM 时的功率损耗产生同等明显的影响(图 4 的左端)。

尽管增加 n1/n2 比值会使 VSEC < VSEC,OPTIM 时的效率提高(图 3 左端),但差异并不像 VSEC > VSEC,OPTIM时那样显著(图 3 右端)。因此,似乎减小 n1/n2 比值可能会导致整体性能的提高,不过情况并非总是如此,这取决于在整个 VSEC 工作范围内要确保的最低效率。

图 3:随 VSEC 电压和变压器不同的 n1/n2 比值,DAB 效率的变化。不包括谐振电感和变压器的磁芯损耗。VDC-LINK = 800 V,LM = 720 µH。

图 4:随 VSEC 电压和变压器不同的 n1/n2 比值,DAB 功率损耗的变化。不包括谐振电感和变压器的磁芯损耗。VDC-LINK = 800 V,LM = 720 µH。

最前沿的电子设计资讯

最前沿的电子设计资讯