随着多媒体视频/高速通信组件等科技产品朝向多功能化与IC体积微小化迈进,组件间的系统化整合也被视为未来的重点发展技术。目前业界的封装技术大多朝系统级封装(System in Package;SiP)、多芯片模块(Multi Chip Module;MCM)实现优化。

然而,当IC出现故障时,想分析其中一颗组件或裸片(Die)的异常状况,又碍于SiP、MCM内部打线或基板线路互相联结的复杂关系,将导致进行电性测试时,容易受到其他芯片或组件影响,造成判定困难,甚至无法判定。

该如何解决此状况呢?笔者任职于验证分析实验室——宜特科技(Integrated Service Technology;iST),累积多年厚实的半导体验证分析技术,研发出IC Repackage移植技术,可从SiP、MCM等多芯片或模块封装体中,将欲受测之裸片,无损伤的移植至独立的封装测试体,避开其他组件的干扰,进行后续各项电性测试,快速找到IC故障的元凶是谁。

芯片出厂的最后环节,即是进行裸片针测(Chip Probing,CP),在晶圆(Wafer)完成后、封装前利用点针手法,尽可能先将坏的芯片筛检出来,PASS的裸片经过封装后,再进行最终测试(Final Test,FT),即可完成制造并出货。

不过,通常属于新产品研发的芯片、或是经由客退的芯片,当须重新进行FT,数量皆不多,业界大型封装厂对于此类的少量芯片植入封装体需求,排程交期都较长,甚至不接受少量定制化的封装体芯片植入作业。

有些客户会直接使用陶瓷封装材料植入芯片,然而,陶瓷封装材料或许可以解决部份FT的问题,但市面上单一规格的陶瓷封装材料可能会遇到引脚长度及宽度与测试治具/载具无法匹配,或是陶瓷材料材质与塑料封装体材质不同,因而影响FT结果。

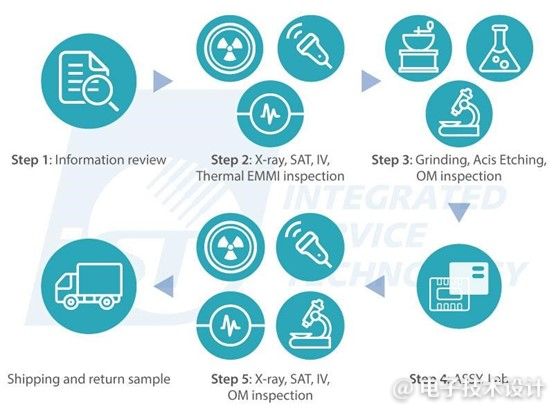

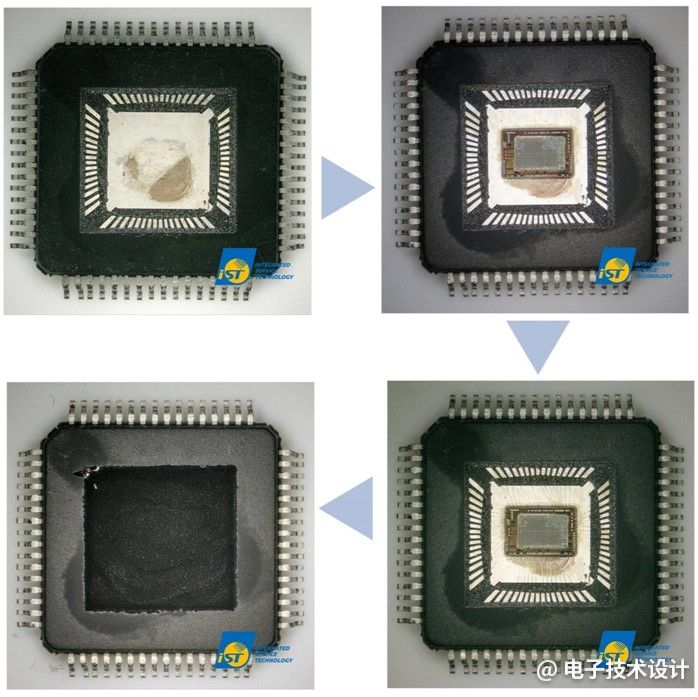

宜特科技使用客户手边现有的IC成品,进行开盖(Decap),做成符合需求的测试治具/载具,后续能便利且有效进行FT。进行IC Repackage移植,在宜特实验室中需要经过五道步骤(图1):

图1:宜特科技实验室的IC Repackage移植五步骤。

步骤一:收到待测样品后,先进行「样品进料质量控制」(Incoming Quality Control,IQC),并确认客户提供的相关信息,包括利用超高分辨率数字显微镜(3D OM)检查外观有无受损、确认封装体内Die的数量、目标异常芯片位置与厚度等,这个阶段主要目的是确认样品现况是否吻合客户反应情形。

步骤二:将利用X射线检测(X–ray)或超音波扫瞄(SAT),进一步确认目前样品有无封装异常,并定位确认需要取出的目标异常芯片位置。接着,藉由IV电特性量测,来确认封装体内客户指定pin的状况;同时,视情况利用Thermal EMMI (InSb)以确认亮点与目标异常芯片的关系。

步骤三:则是利用酸蚀及研磨方式,取出目标异常芯片,并藉由OM确认芯片有无裂痕(Crack)、烧毁(Burnout)、缺口(Chipping)等问题。

步骤四:将取出的裸片重新打线封装成客户要求的封装。这一步骤实际操作情形分成两部份:

1.透过现有IC成品做成测试治具/载具

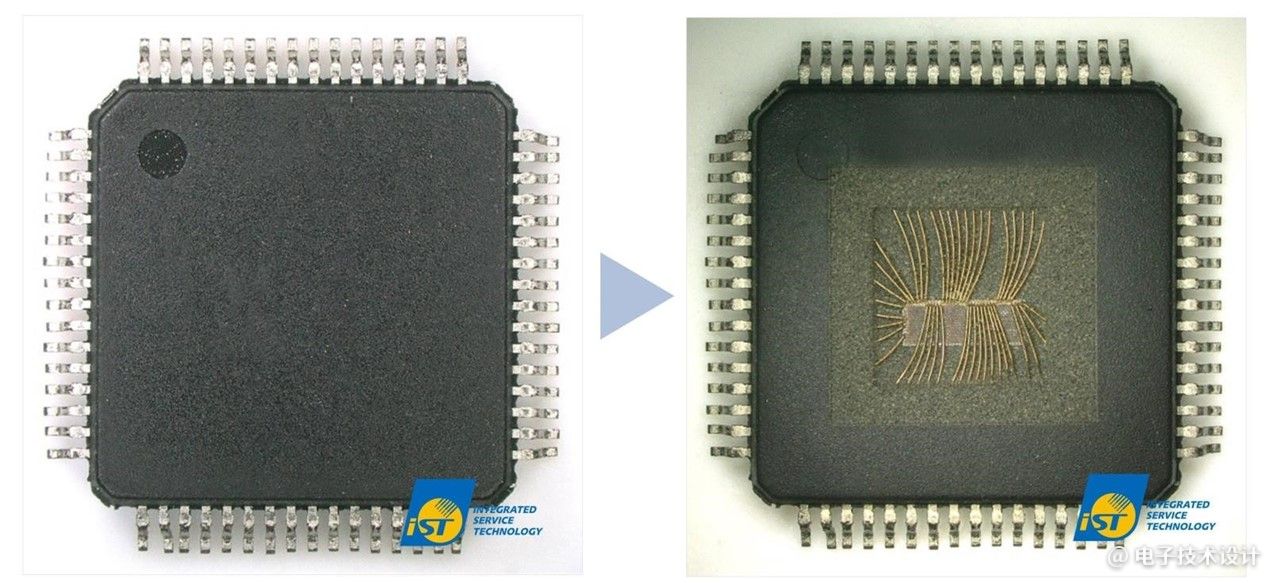

首先,选择符合客户测试治具/载具的IC成品,接着,利用特殊开盖方式,将部分打线及芯片露出(图2),以利后续移除芯片及打线。

图2:封装体经过特殊开盖方式露出芯片及部份打线。

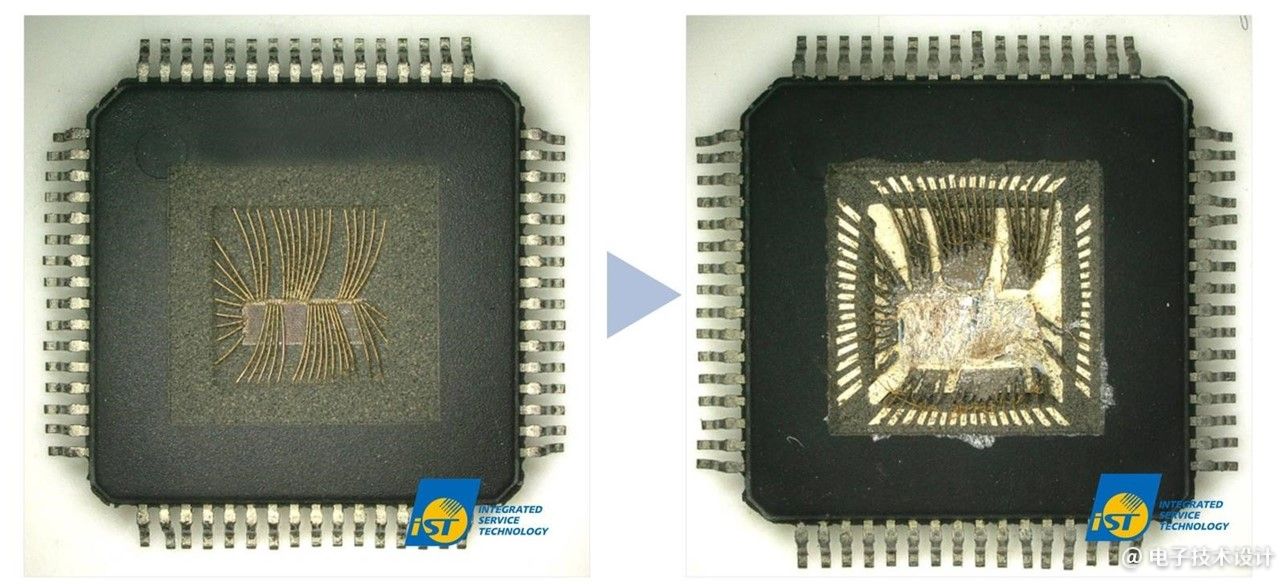

接着,以手动方式移除芯片及打线/引线(图3),露出底板及导线架(二焊点),并保留镀银层。

图3:使用人工物理手法,移除芯片及打线(引线)。

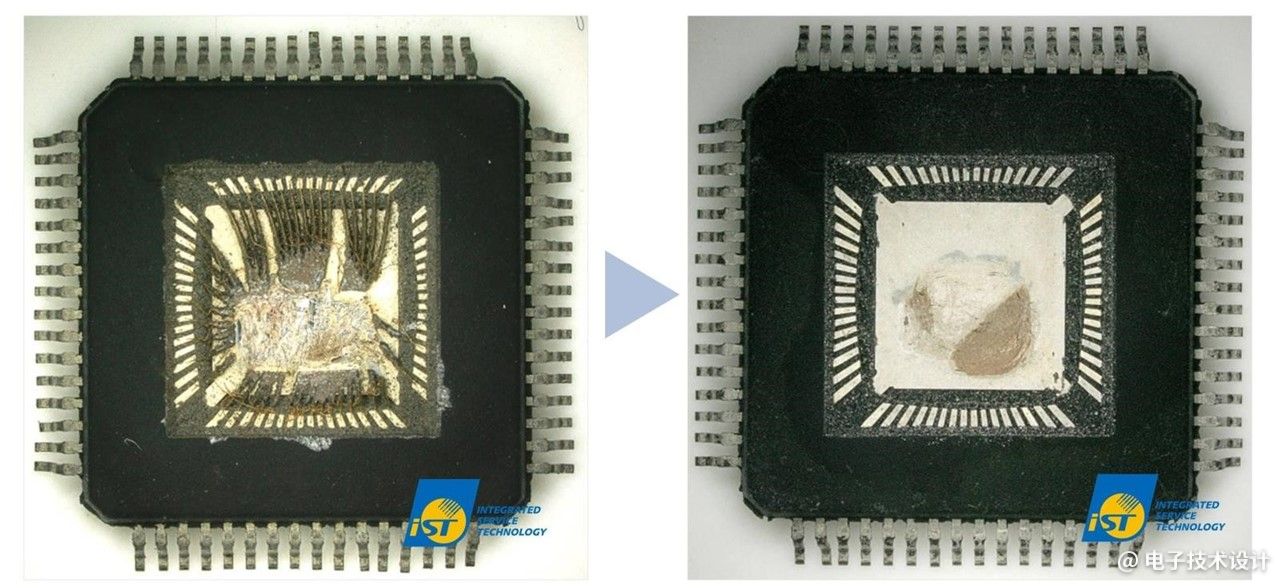

最后,清除封装体内残余的胶体及打线(引线),确认内部无残留物质,为后续成为测试治具/载具进行检查与确认(图4)。

图4:完成可以封装打线的封装体。

2. 结合待测芯片样品与测试治具成为新样品

利用封装黏晶,将待测芯片样品放置于测试治具;接着,施打对应的打线/引线;最后,使用封胶将打线/引线及芯片保护隔绝,完成成品(图5)。

图5:透过黏晶、引线、封胶,结合待测芯片样品与测试治具。

步骤五:先针对样品进行IV电特性量测,或是,客户也可以携回该颗重新封装过后的IC,至自家厂内进行功能性电特性量测。

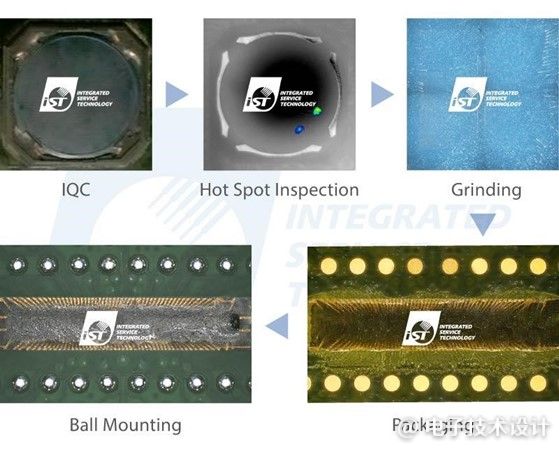

1. 取出SiP中的目标异常Die,制备成wBGA

图2为SiP样品,宜特科技透过Repackage移植技术,将其中的目标异常裸片取出,进行样品制备,移植成窗型BGA(window Ball Grid Array;wBGA)封装形式。藉此,客户即可避开其他组件的干扰,针对该颗wBGA进行后续自动测试设备(Automatic Test Equipment;ATE),确认异常位置。

图6:移植SIP内的目标裸片,样品制备为wBGA封装形式,顺利进行后续各项测试。

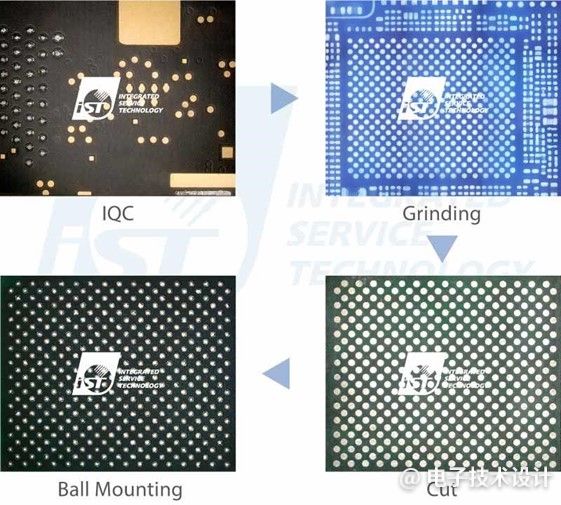

2. 从模块中取出组件,进行植球

当模块中有多颗IC或组件时,宜特科技透过研磨或切割,将目标组件从模抯中取出,接着进行植球服务,让客户可以取回至自家厂内进行各项测试,厘清相关故障原因。

图7为从Module中取出目标BGA IC,经过尺寸量测及植球后,便于客户后续测试。

图7:取出Module内的目标组件,经植球后,即可回到客户厂内测试。

最前沿的电子设计资讯

最前沿的电子设计资讯