华为此前4月5日公开“一种芯片堆叠封装及终端设备”专利引起了广泛关注,也透露了其从2019年就对芯片堆叠技术进行布局。

就在近日,华为又公开了2项芯片相关的发明专利。

EDN电子技术设计小编查询国家知识产权局官网发现,华为公开了申请的2项芯片相关专利——“一种多芯片堆叠封装及制作方法”和“芯片堆叠封装结构及其封装方法、电子设备”,申请公布号分别为CN114450785A和CN114450786A。

据公开的专利摘要显示,该专利涉及芯片技术领域,不仅能够解决多芯片的应力集中问题,还能够以进行更多层芯片的堆叠。

国家知识产权局网站截图

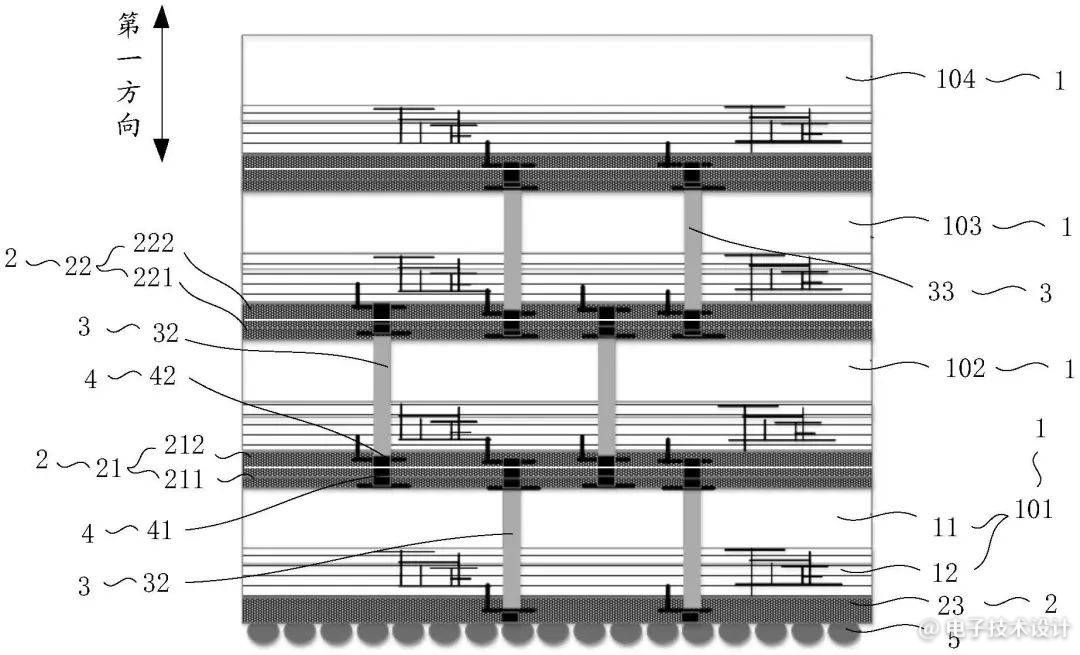

该多芯片堆叠封装包括:沿第一方向堆叠设置的第一芯片(101)和第二芯片(102),其中所述第一芯片(101)内沿所述第一方向开设有第一导电通孔(31),所述第二芯片(102)内沿所述第一方向开设有第二导电通孔(32);设置于所述第一芯片(101)和所述第二芯片(102)之间的第一再布线层(21),且所述第一再布线层(21)的两侧分别与所述第一芯片(101)的表面和所述第二芯片(102)的表面固定,其中所述第一导电通孔(31)和所述第二导电通孔(32)通过所述第一再布线层(21)导通,所述第一导电通孔(31)和所述第二导电通孔(32)错开设置。所述多芯片堆叠封装及制作方法用于芯片的制造。

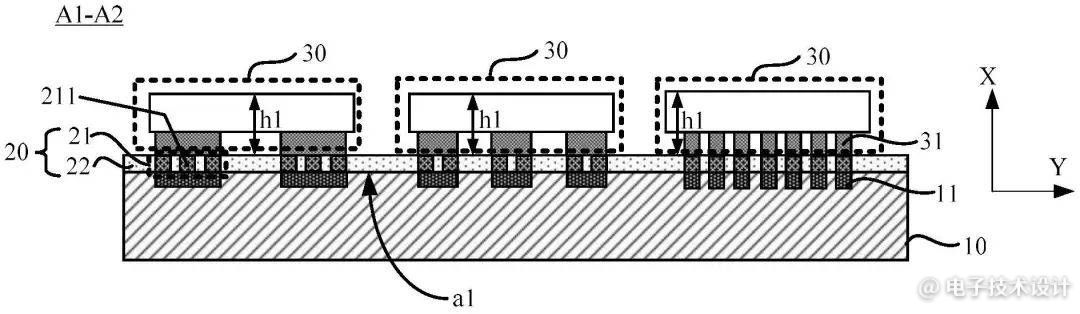

专利摘要显示,该专利为一种芯片堆叠封装结构(100)及其封装方法、电子设备(1),涉及电子技术领域,用于解决如何将多个副芯片堆叠单元(30)可靠的键合在同一主芯片堆叠单元(10)上的问题。

国家知识产权局网站截图

芯片堆叠封装结构(100),包括:主芯片堆叠单元(10),具有位于第一表面上的绝缘且间隔设置的多个主管脚(11);第一键合层(20),设置于第一表面上;第一键合层(20)包括绝缘且间隔设置的多个键合组件(21);多个键合组件(21)中的每个包括至少一个键合部(211),任意两个键合部(211)绝缘设置,且任意两个键合部(211)的横截面积相同;多个键合组件(21)分别与多个主管脚(11)键合;多个副芯片堆叠单元(30),设置于第一键合层(20)远离主芯片堆叠单元(10)一侧的表面;副芯片堆叠单元(30)具有绝缘且间隔设置的多个微凸点(31);多个微凸点(31)中的每个与多个键合组件(21)中的一个键合。

EDN电子技术设计小编注意到,本次公开的两项专利与4月5日公开专利申请时间均为2019年,但华为并非2019年才开始布局该技术。

据了解,早在2012年,华为便向国家知识产权局申请了一项名为“芯片堆叠封装结构”的发明专利。这意味着,华为对芯片堆叠封装的研究在2012年甚至更早的时间就已开始。

而华为官方首次公开确认芯片堆叠技术则是在今年3月28日举行的华为2021年年报发布会上。华为轮值董事长郭平当时表示,未来华为可能会采用多核结构的芯片设计方案,以提升芯片性能,同时采用面积换性能,用堆叠换性能,使得不那么先进的工艺也能持续让华为在未来的产品里面,能够具有竞争力。

随后,华为于4月5日正式公开了“一种芯片堆叠封装及终端设备”专利。

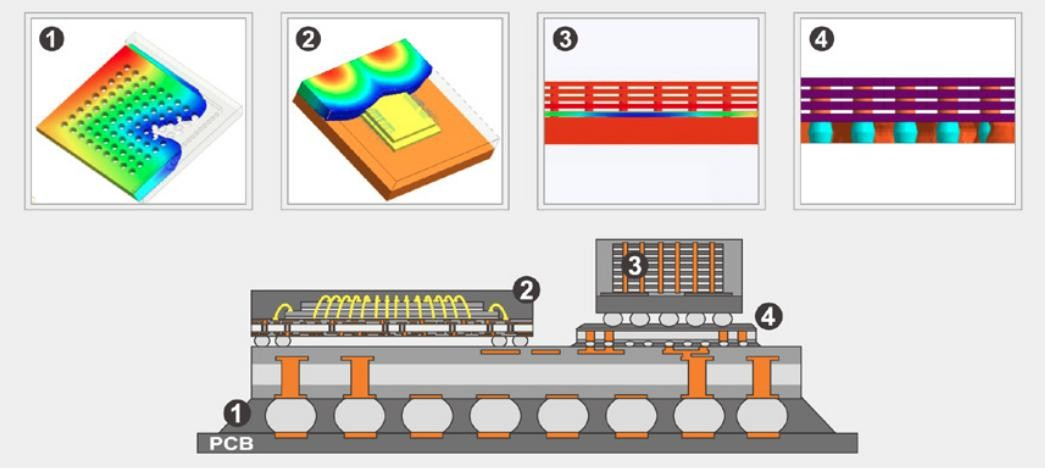

堆叠技术也可以叫做3D堆叠技术,是利用堆叠技术或通过互连和其他微加工技术在芯片或结构的Z轴方向上形成三维集成,信号连接以及晶圆级,芯片级和硅盖封装具有不同的功能,针对包装和可靠性技术的三维堆叠处理技术。

该技术用于微系统集成,是在片上系统(SOC)和多芯片模块(MCM)之后开发的先进的系统级封装制造技术。 在传统的SiP封装系统中,任何芯片堆栈都可以称为3D,因为在Z轴上功能和信号都有扩展,无论堆栈位于IC内部还是外部。

目前,3D芯片技术的类别包括:基于芯片堆叠的3D技术,基于有源TSV的3D技术,基于无源TSV的3D技术,以及基于芯片制造的3D技术。

当前,台积电、英特尔、三星等国际半导体厂商都开发了自己的3D芯片封装技术。

例如,在前段时间苹果举行线上发布会时推出了号称“史上最强”的Apple M1 ultra,就是一种采用堆叠思路设计的芯片。 M1 ultra将两枚M1 Max中隐藏的芯片间互连模块(die-to-die connector)通过技术手段整合在一起,苹果将其称之为“Ultra Fusion”架构,拥有1万多个信号点,互连带宽高达2.5TB/s,而且延迟、功耗都非常低。通过这种方式组合而成的M1 Ultra,规格基本上是M1 Max的翻倍。同样是采用了5nm制造工艺,但M1 Ultra的晶体管数量却高达1140亿个,统一内存最高达到128GB,总带宽800GB/s。

此外还有英特尔于2018年底推出了业界首创的3D逻辑芯片封装技术——Foveros;三星在2018年推出了名为“X-Cube”的3D IC封装技术;台积电则将旗下SoIC、InFO及CoWoS等3D IC技术平台进行整合,并命名为“3D Fabric”。

业内人士指出,苹果与华为是两种截然不同的方式。

双芯叠加层级运用于设计和生产初期,也就是说在设计过程中将原来的一颗芯片设计成双层芯片然后利用自己独特的技术,来将这两层芯片封装在一颗芯片中,通过同步信号方式与一些其他方法就可以激活双层芯片共同发力,从而实现芯片性能突破。所以说一个物理层堆叠,一个设计之初就开始改变设计思路,这是完全不同的两个方式。

华为的方法使用小芯片的重叠部分来建立逻辑互连。同时,两个或更多小芯片仍然有自己的电力传输引脚,使用各种方法连接到自己的再分配层 (RDL)。但是,华为的专利技术实施起来并不容易且便宜。

华为的流程涉及在连接到另一个(或其他)之前将其中一个小芯片倒置。它还需要构建至少两个重新分配层来提供电力,这并不是特别便宜,因为它增加了几个额外的工艺步骤。好消息是其中一个芯片的再分配层可以用来连接内存等东西,从而节省空间。

但业内人士认为,华为的方法增加了堆栈的表面尺寸,从而简化了冷却。同时,堆栈仍然小于2.5D封装,这对于智能手机、笔记本电脑或平板电脑等移动应用程序很重要。此外,华为的混合3D堆叠方式比其他公司传统的2.5D和3D封装技术更通用。

即使如此,业内人士仍认为双芯片组合带来的结果是1+1>1,但不一定等于2。

最前沿的电子设计资讯

最前沿的电子设计资讯