为了使大多数电子设备正常运行,提供准确的时序非常重要。许多应用需要在 PCB 上的特定位置呈现同步时钟信号,并在其他位置呈现异步时钟,这种布局通常称为多分支时钟树。随着时序复杂程度的增加,实现多分支时钟树的设计挑战也越来越大。抖动是最重要的时序规范之一,是衡量时钟信号周期变化的指标。随着时钟树解决方案变得越来越复杂和频率越来越高,抖动会变得更糟,这使得满足公差的任务非常具有挑战性,对于超高速应用,公差可能在飞秒(10-15 秒)数量级。在本文中,我们将讨论时钟树中的主要组件,分析不同类型的抖动和抖动来源,并讨论减少抖动对电子电路影响的方法。

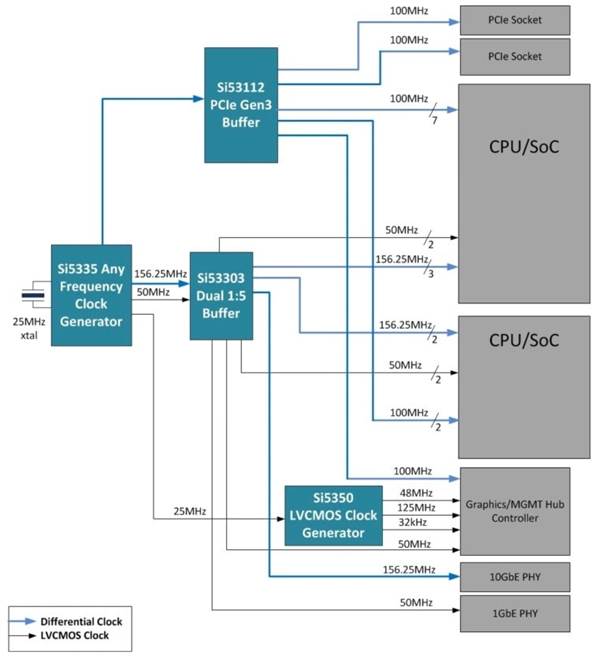

时钟树设计往往是依据具体应用而定,这意味着没有“典型”解决方案。图 1 显示了一个使用Silicon Labs组件的时钟树范例。

图 1:使用由单晶振和时钟发生器组合的多时钟时钟树。(来源:Silicon Labs)

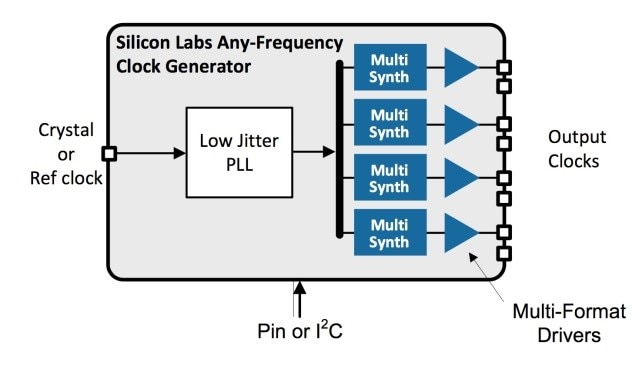

时序电路通常由下列组件中的一个或多个构成,包括石英晶体、晶体振荡器、缓冲器、时钟发生器和抖动衰减器。石英晶体是确定时序信号频率的压电谐振器,这些可以制造成产生精确的信号频率(32kHz ~50MHz),其随温度变化很小。晶体振荡器 (XO) 是一种电路,它使用石英晶体产生的信号以单端或差分格式产生其他所需的时钟频率。 XO 的一个例子是 Microchip 的 PL602-03,它可以使用 12 ~ 25MHz 的晶体工作,以产生 48 ~ 100MHz 的低抖动输出频率。压控晶体振荡器 (VCXO) 可生成时钟频率,并可以通过改变施加的输入电压来改变频率。 ON Semiconductor的 NB3N508S是一款 VCXO,它通过向器件的 VIN 引脚施加 0 ~3.3V的电压,利用27MHz 晶体信号产生 216MHz 输出。时钟发生器是一种 IC,它使用 XO 或 VCXO 产生的信号来产生多个不同频率的时钟信号。Silicon Labs的Si5338Q 是一款时钟发生器,可生成高达 350MHz 的四个独立用户可编程时钟频率和高达 710MHz 的其他选定频率。它可以产生四个差分时钟、八个单端时钟或它们的组合。

图 2:时钟发生器减少了电路板上的组件数量。(来源:Silicon Labs)

IDT的 9DBL0是一款时钟缓冲器,它能够从晶体振荡器中获取时钟信号,并将其分配到PCB板上的不同位置,而抖动衰减器是用于减少时钟信号中抖动量的专用组件,在高速应用中,抖动可能成为一个主要问题。

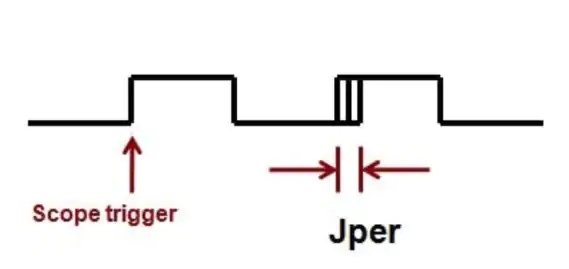

抖动是真实时钟信号相对于其理想值周期变化的量度,以秒为单位。抖动有两种形式:随机性抖动和确定性抖动。随机性抖动是由电子元件固有的电噪声引起,但它通常足够小,不会影响电路性能。确定性抖动则通常是重复的,可以分为周期性抖动或数据相关抖动。例如,由开关电源引起的抖动是周期性抖动,因为它与使用的开关频率相匹配。与数据相关的抖动可以是周期性的或非周期性的,它是由不断变化的占空比和以太网或 PCIe 等系统中编码串行数据流的不规则时钟边沿引起。与数据相关的抖动与系统相关,可能难以追踪。抖动通常归类为三种方式之一:绝对、周期和周期到周期。绝对抖动,有时也称为时间间隔误差 (JTIE) ,是实际时钟前沿出现与其理论计算值之间的时间差。周期抖动 (Jper) 是固定周期数内时钟周期最长和最短持续时间之间的差异(图 3),而周期到周期抖动 (Jcc) 是在固定数量周期内测量的连续时钟周期之间的最大差值。

图 3:周期抖动是观测持续时间内最长和最短时钟周期之间的差值。(来源:Silicon Labs)

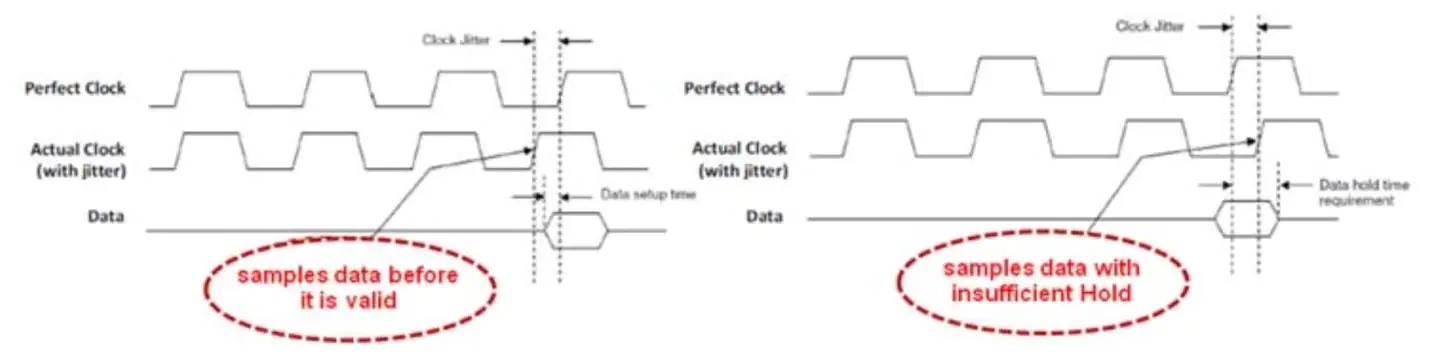

抖动过大可能会对电路性能产生有害影像。在同步以太网 (SyncE) 和光传输网络 (OTN) 应用中,JTIE 会导致同步缺失,这对其正常运行至关重要。 Jper 和 Jcc 在数字应用中很重要,因为它们会影响锁存器和触发器的建立和保持时间,这样会减少精密 ADC 的采样间隔,反过来又会限制数字处理器的运行速度。在不能容忍时钟频率变化的应用中,严格控制 Jcc 也很重要(参见图 4)。

图 4:抖动过大会导致出现采样和保持问题,从而造成数据丢失或损毁。(来源:IDT)

应用良好的设计实践可以最大限度地减少抖动。作为一个好的开始,重要的是要记住每个电子设备都会给电路引入固有抖动,因此如果可行,减少电子设备数量很有帮助。设计人员还应注意不要过度提高电路的抖动要求,因为即使存在一些抖动,大多数电路也可以正常工作。为了在设计时钟树时降低成本,很容易想到采用更少的晶体和时钟发生器,而不是使用更多的时钟缓冲器,这样会降低整个系统时序的精确度。通过使用 VCXO 和零延迟缓冲器可以进一步提高时序精度,但这会增加设计复杂性。其他有助于满足时序要求的常见设计技术包括尽量使信号线较短(以减少时钟树延迟)、采用精心匹配的组件、优化时钟线长度、保持一定间距和屏蔽,以便防止不需要的信号串扰。虽然这些都是很好的做法,但它们并不总能保证达到令人满意的时序性能。EMI、电压波动和机械应力(影响晶体的压电特性)都会导致抖动。如果抖动仍然存在问题,则可能需要使用仪器进行仔细分析以确定问题产生的根本原因。假设抖动具有高斯分布,因而通常以时序增量(皮秒或飞秒)的均方根 (RMS) 值来确定。计算结果是抖动测量的标准偏差,通常使用高速数字示波器来完成,这种仪器特别适合测量高频或低频时钟信号的数据相关抖动(JTIE、Jper 和 Jcc)。收集到原始抖动测量值后,即可对 RMS 抖动值进行后处理。进而通过执行“波峰因数(crest factor)”计算将该值转换为峰峰值,其中假定可接受的典型误码率 (BER) 为 10-12。对于这个 BER 值,波峰因数为 14.069,这意味着 1ps 的 RMS 抖动相当于 14.069ps 的峰峰值抖动。

一旦确定了时钟树中抖动问题的来源,就可以使用一些标准设计技术来解决,其中包括采用单个多输出缓冲器(而不是许多实例中的单个缓冲器)、选择更高性能的组件以及进行重新布线和更好地匹配金属迹线长度等。如果系统中随机抖动是时序问题的主要来源,最合乎逻辑的方法是将组件数量减少到最低限度,然后用更高规格的部件依次替换每个组件,直到满足时序要求为止。在特殊情况下,即使所有故障排除技术都尝试之后,也可能无法简单地满足抖动规范要求,在这种情况下,唯一可用的选择是在时钟树中使用抖动衰减器,例如 IDT 的 8V19N407 或 Silicon Lab 的 Si5317。这些器件能够从输入时钟信号中滤除噪声,以产生低抖动时钟输出。

时钟信号的抖动是电子电路中时序问题的主要原因,这其中有几个来源。在本文中,我们分析了时钟树中抖动的类型和来源,并讨论了良好的设计实践和认真的组件选择相结合如何有助于减少抖动的影响。

最前沿的电子设计资讯

最前沿的电子设计资讯