三星是世界上极少数掌握先进制造工艺的半导体厂商之一,晶圆代工规模仅次于台积电(TSMC),有报道称,在 3 nm制造工艺方面,韩国三星电子希望击败台积电 (TSMC)。

据韩国媒体的报道暗示,三星将在下周宣布 3nm 制造,并且该公司还计划在以后几年生产具有更先进工艺的半导体。

第一份报道来自韩联社援引消息人士的话,该消息人士认为三星将在下周宣布3nm半导体的量产。这些谣言是在拜登总统早些时候访问韩国之后出现的,在此期间,他参观了三星的芯片制造设施以及 3nm 芯片的演示。

如果传闻成真,那么三星将比台积电更早量产3nm。

台积电今年早些时候开始试产其被称为“N3”的 3nm 工艺,该公司首席执行官 CC Wei 博士发表的声明表明,该芯片制造商预计将在今年下半年开始生产。

因此,如果三星下周宣布 3nm 量产,那么这家韩国公司将稍微领先于其更大的竞争对手。

然而,韩国媒体的多个未经证实的传言也表明,三星的 3nm 工艺几乎没有客户排队,这给进入量产带来的好处蒙上了一层阴影。

关于三星 3nm 工艺客户很少的传言特别有趣,因为去年就有传言称,由于台积电缺乏可用性,AMD 正在考虑订购该公司的 3nm 产品。然而,在三星产量管理不善的报道之前,这些问题已经曝光,这可能会改变情况。

日前,在按计划推进3nm制程工艺下半年量产的台积电,也在研发更先进的2nm制程工艺,他们的这一制程工艺,是计划在2025年量产。

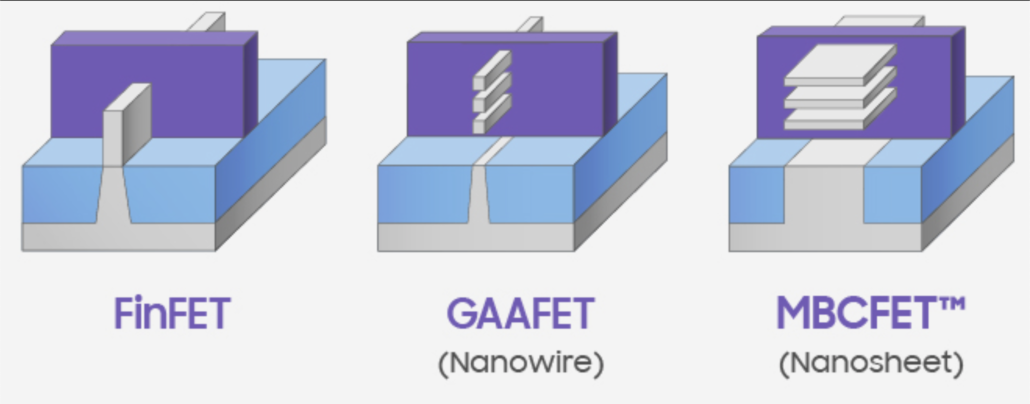

台积电透露,他们的2nm制程工艺将基于全新的纳米片电晶体架构,与5nm工艺所采用的鳍式场效应晶体管(FinFET)完全不同,会带来更强的性能和更优的能效,但所需要的投资也会更大。

在这方面,Business Korea的一份报告称,三星也将在 2025 年进入其 2nm 生产阶段,与台积电保持同步。

三星晶圆代工业务的负责人也曾表示,他们在按计划推进2nm制程工艺在2025年下半年量产。三星希望通过技术上的飞跃,快速缩小与台积电的差距。3 纳米工艺将半导体的性能和电池效率分别提高了 15% 和 30%,同时与 5 纳米工艺相比,芯片面积减少了 35%。

三星和台积电都将在其 2nm 产品中使用称为 GAAFET 的新型晶体管,但三星也计划在 3nm 产品中使用 GAAFET。

因此,它的 3nm 技术自然会引起芯片设计人员的兴趣,即使存在良率问题。在芯片行业,良率是指硅晶圆中通过质量控制标准的芯片数量,较低的良率导致公司每片晶圆的可用芯片数量减少。

最前沿的电子设计资讯

最前沿的电子设计资讯