台积电最近在加利福尼亚州圣克拉拉举行了年度技术研讨会,演讲全面概述了它们的状态和即将到来的路线图,涵盖了工艺技术和先进封装开发的各个方面。EDN电子技术设计小编为大家总结一下这场研讨会有哪些亮点。

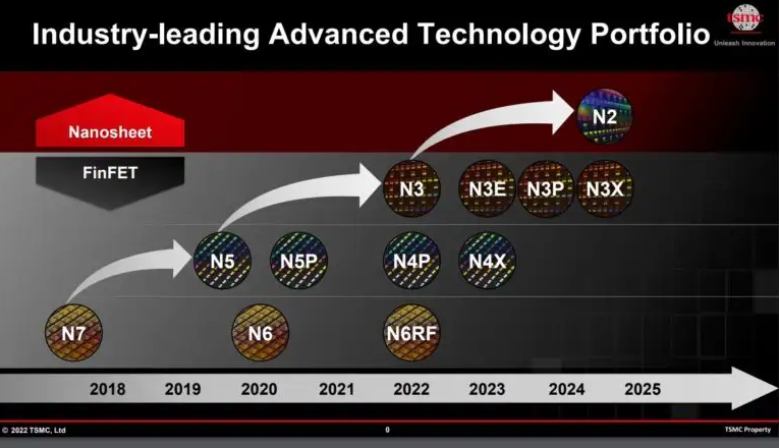

在技术研讨会上,台积电宣布的关键事项之一是其属于其 N3(3 纳米级)和 N2(2 纳米级)系列的领先节点,这些节点将在未来几年用于制造先进的 CPU、GPU 和 SoC .

技术研讨会上,台积电谈到了将在未来几年推出的四种 N3 衍生制造工艺(总共五个 3 纳米级节点)——N3E、N3P、N3S 和 N3X。这些 N3 变体旨在为超高性能应用提供改进的工艺窗口、更高的性能、增加的晶体管密度和增强的电压。所有这些技术都将支持 FinFlex,这是 TSMC 的“秘密武器”功能,极大地增强了他们的设计灵活性,并允许芯片设计人员精确优化性能、功耗和成本。

台积电的第一个 3 纳米级节点称为 N3,该节点有望在今年下半年开始大批量制造 (HVM)。实际芯片将于 2023 年初交付给客户。该技术主要针对早期采用者(如Apple 等),他们可以投资于领先的设计,并从前沿节点提供的性能、功率和面积 (PPA) 中受益。因此 N3 的工艺窗口相对较窄(产生确定结果的一系列参数),就良率而言,它可能并不适合所有应用。

一年后大规模量产 N3E 工艺变体,N3E 看起来是比 N3 更通用的节点,台积电期望该工艺在移动和 HPC 平台上得到广泛采用。

将在 2024 年左右的某个时间推出 N3P,这是其制造工艺的性能增强版本,以及N3节点的密度增强版本N3S。

对于那些无论功耗和成本都需要超高性能的客户,台积电将提供N3X,它本质上是N4X的意识形态接班人。同样,台积电没有透露有关该节点的详细信息,只是表示它将支持高驱动电流和电压。

公布其 N2(2 纳米级)制造技术计划于 2025 年某个时间投入生产,并将成为台积电第一个使用其基于纳米片的栅极全方位场效应的节点晶体管(GAAFET)。新节点将使芯片设计人员能够显著降低其产品的功耗,但速度和晶体管密度的改进似乎不太明显。

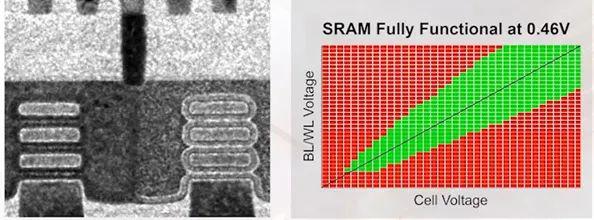

台积电的 N2 是一个全新的平台,广泛使用 EUV 光刻技术,并引入了 GAAFET(台积电称之为纳米片晶体管)以及背面供电。新的环栅晶体管结构具有广为人知的优势,例如大大降低了漏电流(现在栅极围绕沟道的所有四个边)以及调节沟道宽度以提高性能或降低功耗的能力。

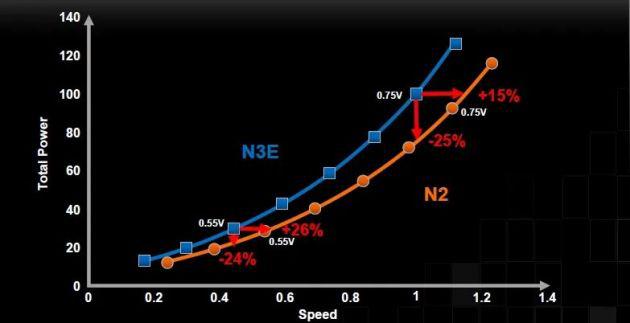

与 N3E 相比,N2 将提供约 10-15% 的性能提升(@iso-power,0.75V)或约 25-30% 的工号降低(@iso-perf,0.75V);另请注意上图中指定的工作范围低至 0.55V。

将为其 N2 节点提供各种功能和选择,以允许芯片设计人员针对移动和高性能计算设计等进行优化(请注意,台积电将 HPC 称为非移动、汽车或专业的一切。包括从低功耗笔记本电脑 CPU 到针对超级计算机的高端计算 GPU)。

此外,平台产品包括称之为“chiplet integration”的东西,这可能意味着台积电使其客户能够轻松地将 N2 芯片集成到使用各种节点制造的multi-chiplet封装中。由于晶体管密度扩展正在放缓并且新工艺技术的使用成本越来越高,因此multi-chiplet封装将在未来几年变得更加普遍,因为开发人员将使用它们来优化他们的设计和成本。

顺便说一句,台积电面临两难境地,即不同平台的要求具有如此广泛的功耗、性能和面积 / 成本目标。如上所述,N3E 正在使用不同的库解决这些问题,并结合了定义单元高度的,不同数量的鳍。对于 N2 库设计,该设计决策被关于整个垂直堆叠纳米片数量的工艺技术决策所取代(器件纳米片宽度有一些允许的变化)。就纳米片拓扑而言,看看台积电选择为 N2 提供什么来覆盖移动和 HPC 市场将会很有趣。(下图来自台积电在 VLSI 2022 大会上的早期技术演示,描绘了 3 个纳米片。)

注意:有两种新兴的工艺技术正在被采用来降低功率传输阻抗和改善局部可布线性——即 " 埋地 " 电源轨 ( BPR:buried power rail ) 和 " 背面 " 配电 ( BSPDN:backside power distribution ) 。对提供 BPR 的初步调查已迅速扩展到处理集成完整 BSPDN(如 N2)的路线图。然而,很容易混淆这两个首字母缩写词。

考虑到现代半导体生产周期的长度,如果一切按计划进行,预计第一批 N2 芯片将在 2025 年末或 2026 年上市。

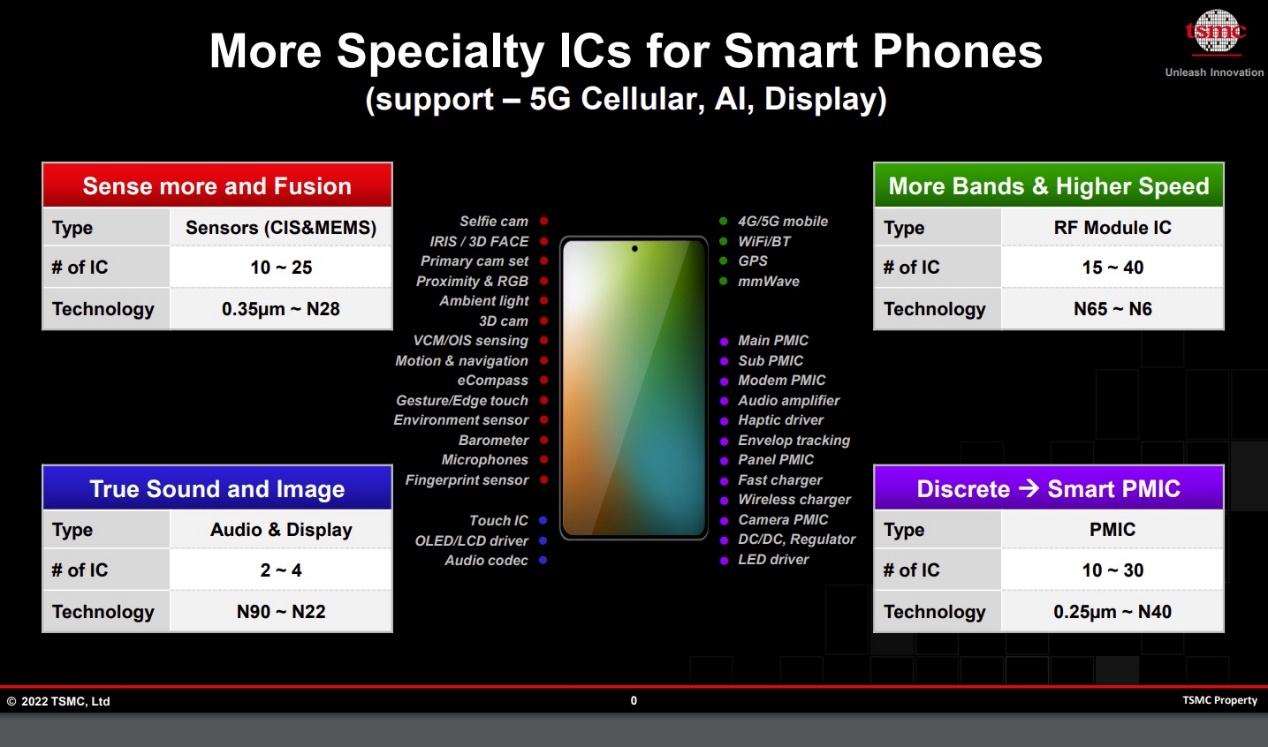

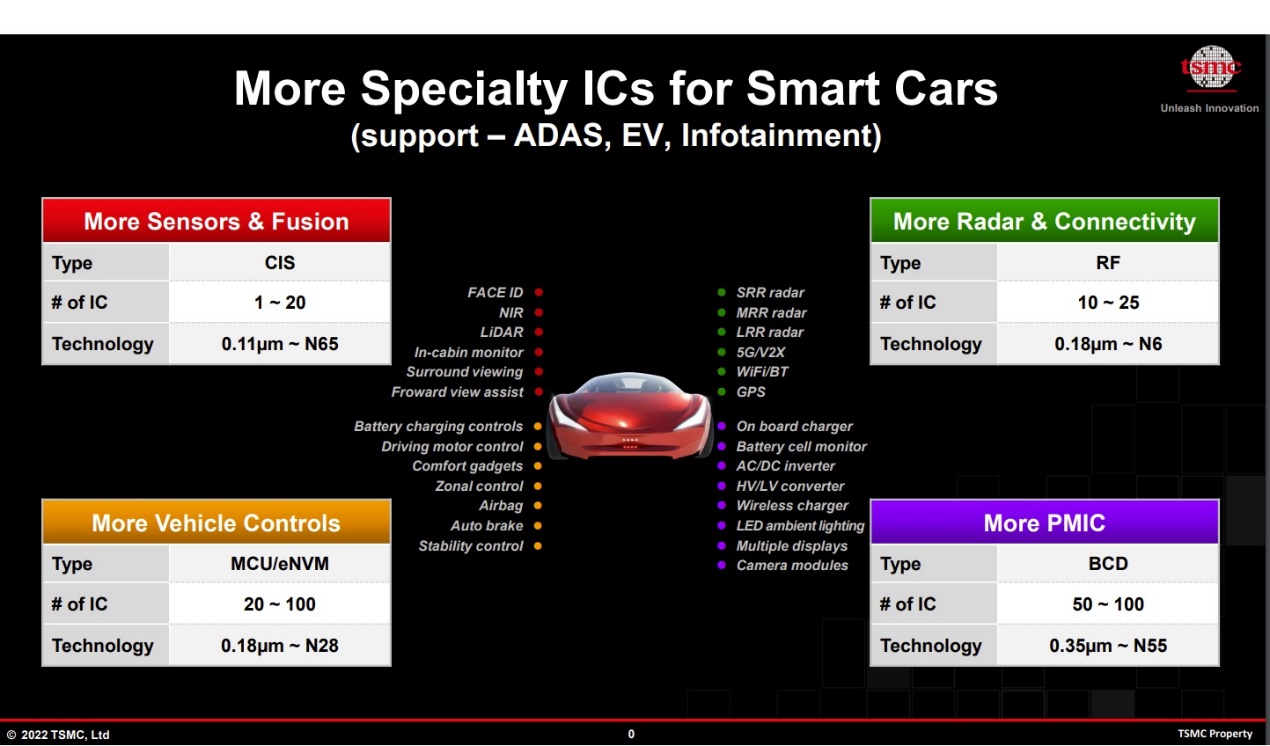

台积电将继续投资成熟的节点和专业技术,从 2021 年到 2025 年,产能将扩大 1.5 倍,包括 Fabs F14P8(天安)、F16 P1B(南京)、F22 P2(高雄)和 fab F23 P1(日本熊本)。

台积电高管周四表示,这家全球最大的芯片制造商将在 2024 年拥有下一个版本的 ASML Holding NV 最先进的芯片制造工具。 这种名为“high-NA EUV”的工具产生聚焦光束,在用于手机、笔记本电脑、汽车和人工智能设备(如智能扬声器)的计算机芯片上创建微观电路。EUV 代表极紫外,即 ASML 最先进机器使用的光波长。

到 2025 年,其成熟和专业节点的产能将扩大约 50%。该计划包括在中国台湾、日本和中国大陆建设大量新晶圆厂。此举将进一步加剧台积电与格芯、联电、中芯国际等芯片代工厂商之间的竞争。

台积电还宣布推出适用于 NVM、HV、传感器、PMIC、ULP/ULL、模拟和射频技术的集成专业技术平台。

最前沿的电子设计资讯

最前沿的电子设计资讯