增强型GaN基高电子迁移率晶体管(HEMT)已经采用两种不同的结构开发出来。这两种增强型结构是金属-绝缘层-半导体(MIS)结构2和栅极注入晶体管(GIT)结构3。MIS结构具有受电压驱动的小栅极漏电流,而GIT则具有脊形结构和高阈值电压。两者也都有一些缺点。MIS对栅极干扰的可靠性较低,阈值电压较低,而GIT的栅极开关速度较慢,栅极漏电流较大。原文可点此获得。

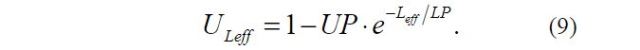

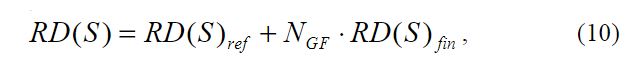

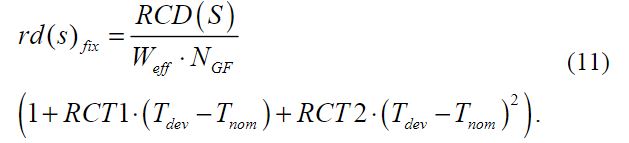

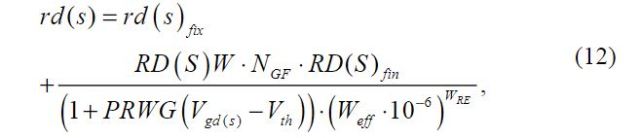

图1给出了用于测试这两种结构的设置。可以对MIS和GIT两种结构使用单一模型。GIT用于开发使用电流模型的等效电路,而MIS则用于内核漏极电流建模4。随后就可使用S参数测量值评估两种器件中的每一个的电路。

图1a显示了MIS晶体管的基本结构以及嵌入式源极场板(ESFP)。此处使用了金属有机化学气相沉积技术在其上形成氮化硅(SiN)钝化层。并使用了载流子密度为1.4×1,013cm2、迁移率为1,203cm2V/s、薄层电阻为382Ω/sq的二维电子气(2DEG)薄片。然后将由位于金属间电介质MO膜顶部的500nm厚的二氧化硅(SiO2)膜所制成的栅极在钝化膜上延伸,从而使Cgs降低。ESFP将栅漏电场分成两个峰值。这会由于负偏压而降低电子密度,并在有源偏压下增加栅极绝缘膜下的密度。

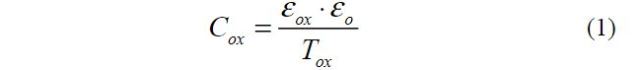

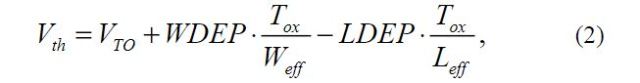

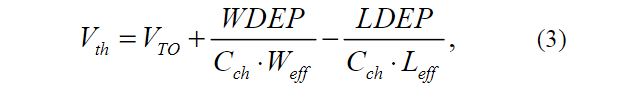

图1b显示了脊型GIT晶体管和源极场板(SFP)的基本结构。其结构有一个10nm的作为阻挡层的氮化铝镓(AlGaN)层和一个60nm的P-GaN层。在使用ICP蚀刻机蚀刻表面后,栅极表面采用100nm厚的SiN膜进行保护。漏极和源极也由蚀刻的SiN膜形成,从而产生欧姆电极。源极在栅极上方延伸到漏极侧以形成SFP。SFP将栅极到漏极的电场分成两个峰值,从而降低了栅极边缘下方的电场强度。这些实验中所使用的测量值包括:Lmask=0.8mm,Wmask=100mm,源极到栅极距离=0.9mm,栅极到漏极距离=3.5mm,以及栅极电容(Cox)——这个值可以使用栅极氧化膜厚度(Tox)和SiO2的介电常数(εox)计算得到。如图2b所示,要想使用PN二极管空穴注入中所累积的电子密度准确计算栅极沟道电容(Cch)非常困难。因此要在任何参数提取过程开始之前测量Cch。

图1:简化的测试结构。

图2:栅极的放大图。

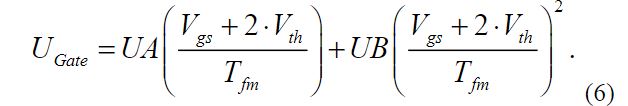

MIS-HEMT的栅氧化层电容

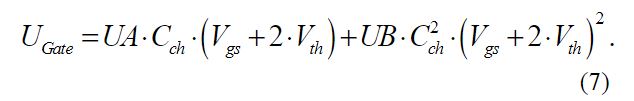

脊形HEMT的栅极至沟道电容

脊形GIT HEMT的肖特基接触结和PN结如图2b所示。沟道区由P型栅极至2DEG区以及来自沟道的空穴注入所组成。漏极电流的导数具有合并的单位面积栅极沟道电容(Cch)。

阈值电压

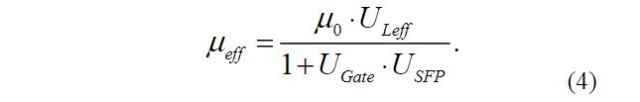

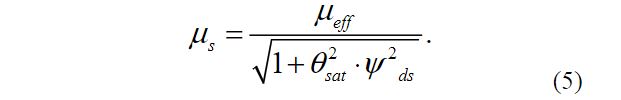

电子迁移率

漏源电阻

图3显示我们的MIS和脊形HEMT两种模型具有相同的宏电路。主HEMT晶体管用作FET以减少漏极电场;次晶体管用作SFP。图4给出了MIS和脊形HEMT两种类型具有固有小信号的交流等效电路。

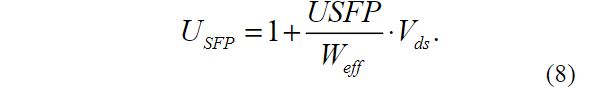

金属互连电感标记为Lg、Ld和Ls,而栅极电容标记为Cgs和Cgd——它们使用经验函数分为常数电容(Cgs0和Cgd0)和偏置相关电容10。漏源电容标记为Cds。扩散电阻为Rdis_T,而扩散电容标记为Cdis_T和Cgdis。栅源内阻为ri。栅极、漏极和源极电阻分别由Rg、Rd_T和Rs_T表示。栅漏电阻由Rgd表示。可扩展栅极电容Cgs_sfp和Cgd_sfp与Cds并联,因为ESFP必须连接在漏极和地之间。

栅极注入PN二极管中脊形HEMT的扩散电容(C_diffusion)和结电容(C_junction)如图4b所示11。此处使用的端子位于源极和栅极之间。C_diffusion甚至可以作为Cdis_T工作。

图3:MIS和脊形HEMT模型的电路。

图4:等效电路。

此处使用了具有脉冲测量模式的曲线跟踪器测量所采用的两种晶体管结构的直流特性。为此提供的偏置具有100ms的脉冲宽度和50%的占空比。

在实验之前使用多栅极长度和宽度的器件进行测量,以便获得线性和饱和漏极电流、阈值电压的模型参数,以及栅极沟道中的长度和宽度依赖性。

该模型具有高精度,可用于MIS和脊形HEMT两种器件而在线性区和饱和区激发静态漏极电流。这在图5和图6中得到了清晰的体现。S参数测量以及小信号交流表征可以有效地用于等效电路的评估1。

图5:测量和仿真得到的Ids-Vgs。

图6:测量和仿真得到的Ids-Vds。

本文总结了HEMT的两种模型:漏极电流模型MIS和脊型GIT。用于交流和瞬态仿真的小信号等效电路模型也使用测量值和S参数制作。对于脊形HEMT,本文详细讨论了栅极漏电流模型以及过量漏极电流。漏极电流模型的其他修改方程可以使用MIS-HEMT模型创建。我们结合使用了HSPICE与Verilog-A语言来创建此模型。我们的测试设置与该模型及其参数配合良好,可应用于电源设计。此外,可以设计瞬态和噪声等效电路以及模型方程来更快速地开关电源。

1H. Aoki, H. Sakairi, N. Kuroda, A. Yamaguchi, and K. Nakahara. “Drain Current Characteristics of Enhancement Mode GaN HEMTs,” Graduate School of Environmental Information, Teikyo Heisei University, Nakano-Ku, Tokyo.

2K. Chikamatsu, M. Akutsu, T. Tanaka, S. Takado, K. Sakamoto, N. Ito, and K. Nakahara. “Embedded Source Field-Plate for Reduced Parasitic Capacitance of AlN/GaN MIS-HEMTs on Si Substrate,” SSDM2015 Conf. Dig., pp. 122–123, Sept. 2015.

3Y. Uemoto, M. Hikita, H. Ueno, H. Matsuo, H. Ishida, M. Yanagihara, T. Ueda, T. Tanaka, and D. Ueda. “GIT-A Normally Off AlGaN/GaN Power Transistor Using Conductivity Modulation,” IEEE Trans. Electron Devices, Vol. 54, pp. 3,393–3,399, Dec. 2007.

4H. Aoki, H. Sakairi, N. Kuroda, Y. Nakamura, K. Chikamatsu, and K. Nakahara. “A Scalable Drain Current Model of AlN/GaN MIS-HEMTs with Embedded Source Field-Plate Structures,” IEEE APEC 2018, Dig. pp. 2,842–2,847, March 2018.

5D. Schroeder. “Modelling of Interface Carrier Transport for Device Simulation,” 1st ed., Springer, 1994.

6BSIM: www-device.eecs.berkeley.edu/bsim.

7U. Radhakrishna, L. Wei, D. S. Lee, T. Palacios, and D. Antoniadis. “Physics-based GaN HEMT Transport and Charge Model: Experimental Verification and Performance Projection,” IEEE IEDM, Dig., pp. 13.6.1–4, Dec. 2012.

8R. Rodriguez, B. Gonzalez, J. García, and G. Toulon, F. Morancho, and A. Nunez. “DC Gate Leakage Current Model Accounting for Trapping Effects in AlGaN/GaN HEMTs,” Electronics, 7, 210, 2018.

9A. M. Cowley and S. M. Sze. “Surface States and Barrier Height of Metal-Semiconductor Systems,” Journal of Applied Physics, Vol. 36, Issue 10, pp. 3,212–3,220, 1965.

10H. Aoki, H. Sakairi, N. Kuroda, Y. Nakamura, K. Chikamatsu, and K. Nakahara. “A Small Signal AC Model Using Scalable Drain Current Equations of AlGaN/GaN MIS Enhancement HEMT,” IEEE RFIC2018, pp. 80–83, June 10–12, 2018.

11Y. C. Fong and K. W. E. Cheng. “Experimental study on the electrical characteristic of a GaN hybrid drain-embedded gate injection transistor (HD-GIT),” 2017 IEEE PESA, 2017.

(原文刊登于EDN姊妹网站Power Electronics News,参考链接:Drain-Current Characteristics of Enhancement-Mode GaN HEMTs,由Franklin Zhao编译。)

本文为《电子技术设计》2022年7月刊杂志文章,版权所有,禁止转载。免费杂志订阅申请点击这里。

最前沿的电子设计资讯

最前沿的电子设计资讯