晶圆代工龙头台积电(TSMC)据报导有望在9月推出备受期待的3奈米(nm)制程节点,而苹果(Apple)将会是其首家3nm客户——Apple将在其今年稍晚发表的Mac计算机中采用台积电为其制造的M2 Pro处理器。根据报导,其他预计采用台积电3nm节点制造芯片的半导体供货商还包括AMD、博通(Broadcom)、英特尔(Intel)、联发科(MediaTek)、辉达(Nvidia)和高通(Qualcomm)。

这显示了台积电较三星(Samsung Foundry)的更强劲优势,Samsung Foundry在今年初声称即将大规模量产3nm处理器,而成为业界人瞩目的焦点。然而,众所周知,Samsung Foundry除了自家的Exynos处理器外,唯一值得关注的重要客户是高通的Snapdragon智能型手机处理器,而今也正与三星的Exynos智慧手机处理器直接竞争。

此外,相较于三星在其3nm节点转向新的环绕式闸极(gate-all-around;GAA)制程技术,台积电决定在3nm制程技术继续沿用FinFET技术,针对即将到来的2nm制程节点才转向GAA制程。GAA制造技术由于具备高导电性而增强其芯片性能。

由于坊间媒体猜测其3nm制造制程即将延迟,台积电重申该制程将在2022年9月前准备就绪。还有媒体传言,由于英特尔更改其即将推出的处理器设计,导致台积电可能因而推迟其3nm计划。最终,这家全球领先的台湾半导体代工厂商得以坚持原定计划,实现其于2022年下半年开始生产3nm的目标。

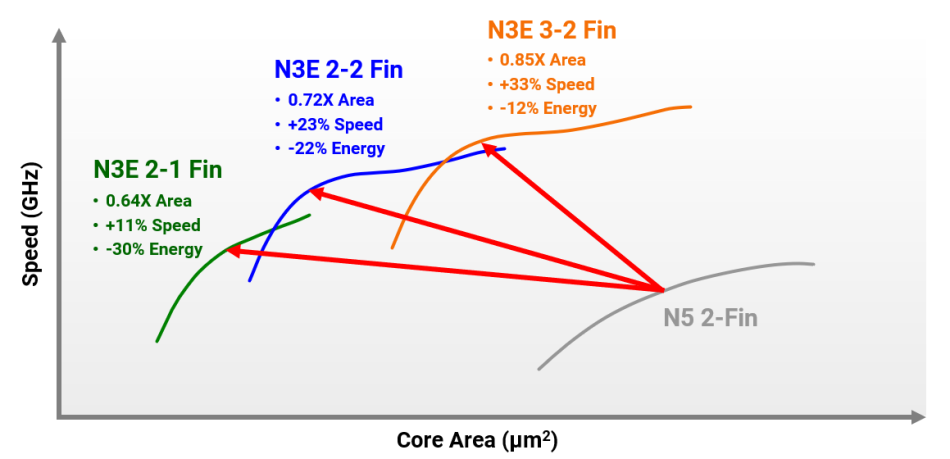

图1:台积电的3NM制程节点基于FINFLEX技术,可望从性能、电源或芯片面积方面为芯片设计人员提高灵活性,以及对其芯片设计的控制。(数据源:TSMC)

台积电的3nm制程节点(称为N3)采用FinFlex技术,让芯片设计人员可在一个模块内混搭不同类型的标准单元,以准确地优化效能、功耗和面积(PPA)。这一新功能特别有利于制造复杂的芯片设计,例如具有大量核心的CPU和GPU。

相较于台积电的5奈米节点(通常称为N5),N3节点的初始版本预计将提升10%至15%的性能,并将功耗降低25%至30%,逻辑密度提高约1.6倍。但是,它对于某些芯片设计来说,所能担儛的良率可能低于预期。台积电计划发布具有改进制程的N3E节点,其晶体管密度略低,但将能够支持大量制造(HVM)。

图2:在N3E制程中,2-1 FIN可降低功耗和泄漏,而2-2 FIN则可提高性能。2-3 FIN提高频率频率以满足更大的运算需求。(数据源:TSMC)

最终,台积电将为其3nm节点系列添加N3P、N3S和N3X等制程版本。因此,值得注意的是,台积电之前还提供了同一节点的不同版本。然而,这一次,它采用新的FinFlex技术,让芯片供货商以客制化其设计,从而提高3奈米芯片在不同领域的性能。换句话说,3nm制造制程将为每颗晶体管的鳍片数量提供不同的变化版本。

虽然3nm制程技术和最的制程节点将于下个月启动,但这些变化版本预计要到2023年和2024年上线。

(参考原文:A closer look at TSMC’s 3-nm node and FinFlex technology,编译:Susan Hong)

最前沿的电子设计资讯

最前沿的电子设计资讯