运算放大器(简称运放)是许多模拟系统和混合信号系统中的一个完整部分。各种不同复杂程度的运放被用来实现各种功能:从直流偏置的产生到高速放大或滤波。伴随者每一代 CMOS 工艺,由于电源电压和晶体管沟道长度的减小,为运放的设计不断提出复杂的课题。

运算放大器的设计可以分为两个较为独立的步骤,第一步是选择或搭建运放的基本结构,绘出电路结构草图,第二步就要选择直流电流,手工设计管子尺寸,以及设计补偿电路等等,然后在手工计算的基础上,运用模拟电路仿真软件对设计的两级运放进行仿真,并对电路进行后续的调试和修改。

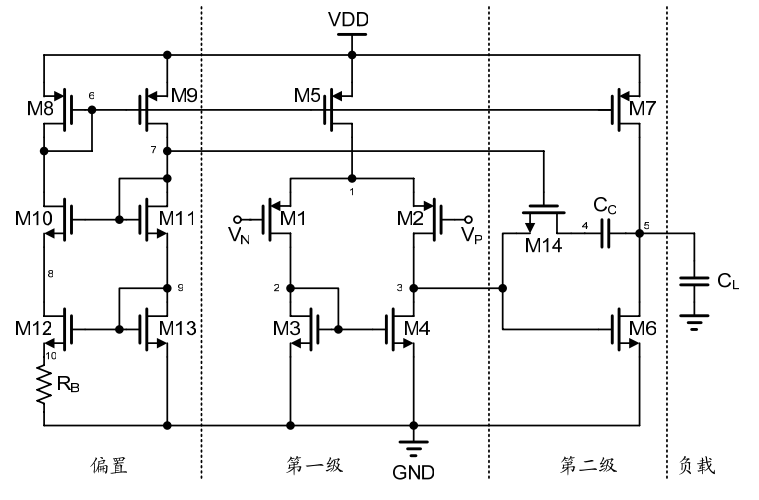

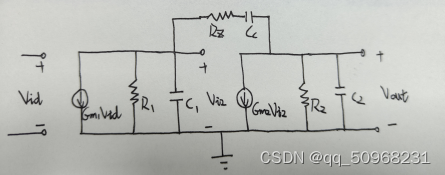

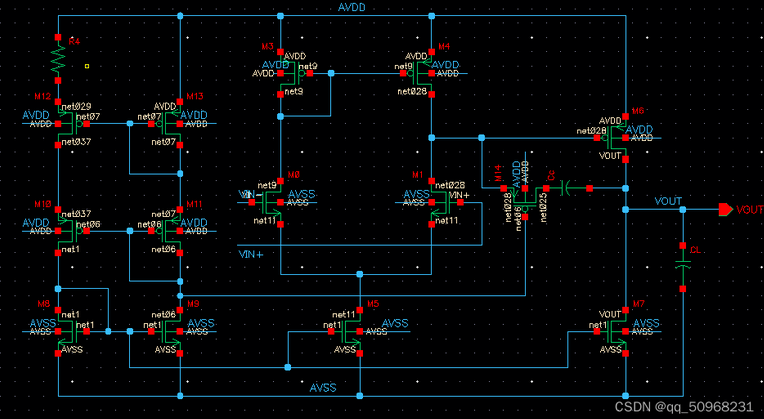

常见的 COMS 二级密勒补偿运算跨导放大器的结构如图 2.1 所示。主要包括四部分:第一级输入级放大电路、第二级放大电路、偏置电路和相位补偿电路。

1.2 电路描述

第一级为PMOS作为输入管的五管差分对,提供高增益并且可以有效抑制共模信号干扰。第二级为共源级放大电路,由M6、M7构成,为电路提供大的输出摆幅,并进一步提高增益。M14和Cc跨接在第一级输出级和第二级输出级之间,起相位补偿作用,M14工作与线性区,通过偏置电路控制其导通电阻。偏置电路由 M8~M13 和 RB 组成,这是一个共源共栅 Widlar 电流源。M8 和 M9宽长比相同。M12 通常是 M13 的几倍,源极加入了电阻 RB,组成微电流源,产生电流 IB。对称的 M11 和 M12 构成共源共栅结构,减小沟道长度调制效应造成的电流误差,同时还为 M14 栅极提供偏置电压。

1.3 静态特性分析

第一级的电压增益为:Gm1R1,Gm1为M1,2跨导,R1为M2、M4输出阻抗并联。第二级的电压增益为:Gm2R2,Gm2为M6跨导,R2为M6、M7输出阻抗并联。

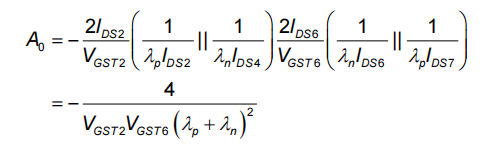

总的直流电压增益为:Gm1Gm2R1R2=gm1gm6(ro2//ro4)(ro6//ro7)

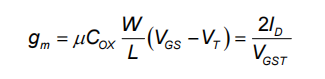

将 VGS-VT简写作 VGST,有:

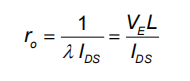

电阻 ro由下式决定:

其中 λ 是沟道长度调制系数,VE 为厄利电压,L 为管子的有效沟道长度。

将gm和ro分别替换得到:

可见,两级运放的直流增益与过驱动电压 VGST和λ成反比,而 L 增大λ将减小,因此,为了得到较高的增益,应当选取较小的过驱动电压和较大的沟道长度。

1.3.1 偏置电路分析

偏置电路由 M8~M13 构成,其中包括两个故意失配的晶体管 M12 和 M13,电阻RB串联在 M12 的源极,它决定着偏置电流和 gm12,所以一般为片外电阻以保证其精确稳定。为了最大程度的降低 M12 的沟道长度调制效应,采用了 Cascode 连接的 M10以及用与其匹配的二极管连接的 M11 来提供 M10 及M14的偏置电压。最后,由匹配的 PMOS器件 M8 和 M9 构成的镜像电流源将电流 IB复制到 M11 和 M13,同时也为 M5 和 M7提供偏置。

下面进行具体计算:

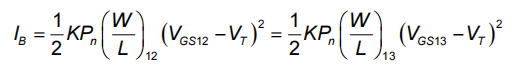

镜像电流源 M8 和 M9 使得 M13 的电流与 M12 的电流相等,从而有

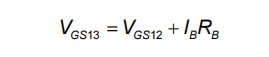

且,

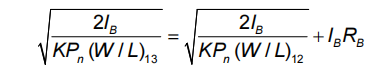

联立上面两式得:

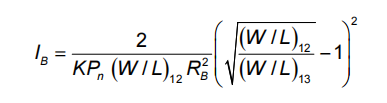

整理得:

一般的,我们取W/L12=4*W/L13

1.3.2 调零电阻分析

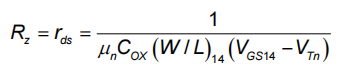

位于线性区的M14充当该两级运放的调零电阻,其中 M14 管的电阻为:

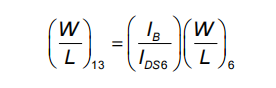

我们设置偏置电流使得 M11 与 M14 的源极电压相同,从而使得VGS11=VGS14,需满足:VGS13=VGS6,从而:

并且

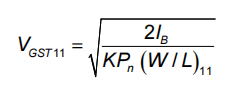

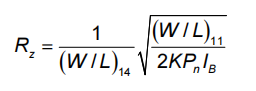

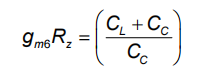

将上式带入Rz,我们得到:

1.4 小信号分析

1.4 小信号分析

1.4.1 零极点分析

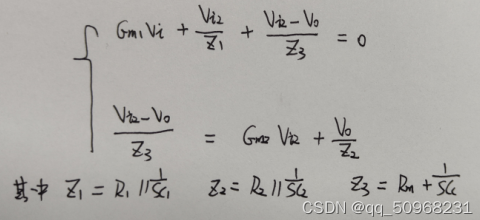

两级运算放大电路小信号等效模型入下图所示:

其中,R1、R2分别为第一级、第二级输出阻抗,C1=Cdb2+Cdb4+Cgs6(Cgs6为C1的主要成分),C2=Cdb6+Cdb7+CL(CL为C2的主要成分)

列KCL节点电流方程:

解KCL方程并化简零极点得到:

P1=1/(Gm2R1R2Cc)

P2=Gm2/C2

P3=1/RzC1

Z=1/Cc(Rz-1/Gm2)

Av=Gm1Gm2R1R2

GBW=Gm1/Cc

1.4.2 相位补偿分析

通过调节M14和M11的长宽比可以起到调节Rz阻值大小,实现移动右半平面零点的作用。如果将零点移到左半平面并与第二极点重合,这样一来可以起到消去第二极点的作用,这要求:

但在实际的电路实现中,在负载电容未知或者运放工作过程中负载电容发生变化的情况下,很难使得零点和第二极点精确抵消。另外,即使在设计时使得零点的位置等于第二极点,由于工艺波动和寄生电容的影响,会使得 Rz 和电路中其它相关的参数偏离原先的设计值,这样一来两者不能够完全抵消,反而会形成相邻的零、极点对,会对电路的瞬态性能产生不利的影响。

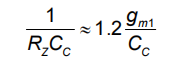

如果将零点移到左半平面略大于 GBW 的位置(一般为 1.2 倍 GBW 处),从而使得相位超前,可以提高电路的稳定性。这就需要:

同时使非主极点 p2在 1.5GBW 处,本次二级运算放大器设计采用这种方法来补偿相位。

设计指标如下表:

2.2 设计步骤

2.2 设计步骤

1.选择Cc的大小。

Cc取值通常为CL的三分之一左右,暂取1.5pf。考虑压摆率指标(IDS5/Cc≥30V/us),得IDS5≥45uA。

2.分配各支路电流。

IDS5=50uA IDS7=200uA ID8=ID9=10uA,270uA×1.8V=0.486mW(<0.5mW),满足静态功耗指标。

3.相位补偿。

由1/Cc(Rz-1/Gm2)=1.2×Gm1/Cc,Gm2=1.5×Gm1/Cc,得Rz=(1/1.2+gm1/gm6)×1/gm1; gm6/gm1≈5。

4.选择过驱动电压。

VDSAT1降低有助于提高电压增益、共模抑制比以及电源抑制比,并且在同等电流前提下,过驱动越小,跨导越大。因此VDSAT1尽量取小,这里取VDSAT1=100mV。

5.计算M1,2宽长比。

已知 ID1=25μA,VDSAT1=0.1V,计算得:(W/L)1,2≈37。

6.计算 M3,4、M6、M5和 M7的宽长比。

为使M5不进入线性区,VDSAT5不能过大,取VDSAT5=300m,得(W/L)5=8.29,为方便其他MOS管设计,取(W/L)5=10;ID7=4ID5,故(W/L)7/(W/L)5=4/1,得(W/L)7=40;由gm6/gm1=5,ID6=8ID1=8ID4,计算得:VDSAT6≈160mV,(W/L)6≈180;且VGS4近似等于VGS6,有(W/L)3,4/(W/L)6=1/8,得(W/L)3,4=21.875,取(W/L)3,4=22。

7.计算 M8,9、M10,11、M12、M13的宽长比和 RB 的阻值。

取(W/L)12=4*W/L)13;由VGS13=VGS6可得,(W/L)13=(IRB/ID6)×(W/L)6,(W/L)13=9,因此W/L)12=36;带入式IB表达式中可解得:RB≈8061Ω;ID9/ID7=10uA/200uA=(W/L)9/(W/L)7,得(W/L)9=(W/L)8=2;将Rz=(1/1.2+gm1/gm6)×(1/gm1)带入Rz表达式求解,取(W/L)14=16,计算得(W/L)10,11=2。

至此器件参数设计完成,由于沟道调制效应以及体效应的影响,各支路电流、MOS管跨导及过驱动电压较设计值会存在一定误差,并且由与M6管宽长比很大,将引入很大的寄生电容,使得C1变大,P3极点变小,使相位裕度减小,将在后面的电路仿真讨论。

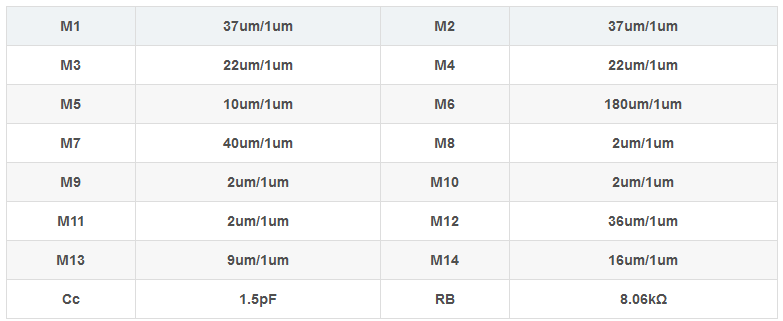

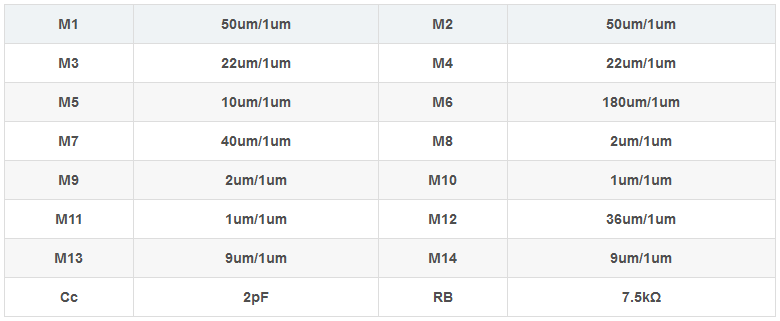

最终得到的器件参数如下:

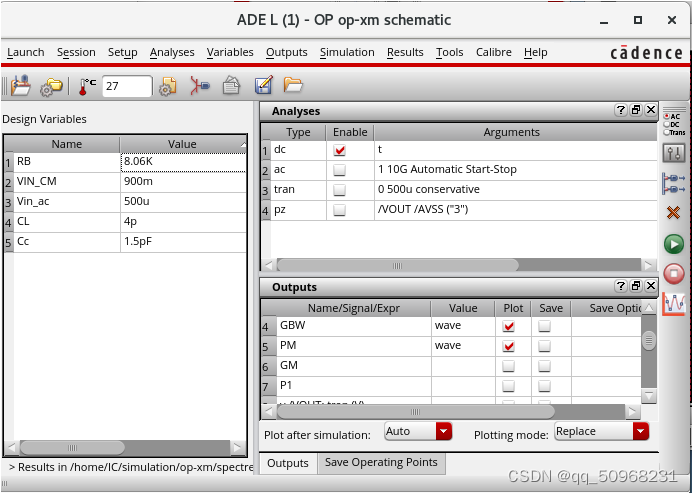

使用Cadence virtuoso IC618对该两级运放进行电路仿真,采用tsmc65nm工艺库完成电路搭建,如下图所示:

3.1 DC直流仿真

3.1 DC直流仿真

完成电路原理图搭建后,在ADE L 仿真器中输入预设参数,选择DC分析,输入共模电平为0.9V。

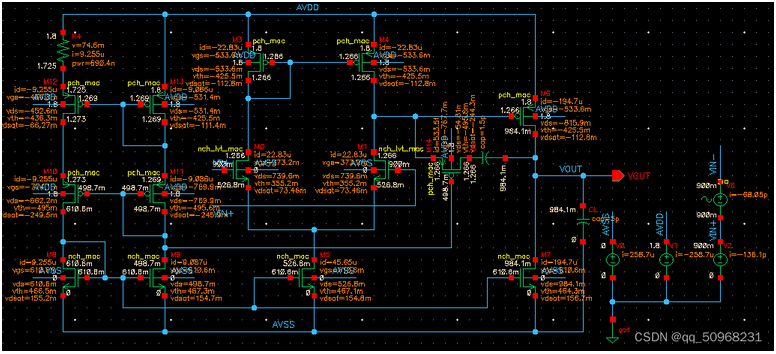

DC仿真结果如下:

DC仿真结果如下:

由于沟道调制效应以及体效应的影响,IRB实际值小于10uA,减小RB值使IRB接近10uA,并且由于W/L1较W/L5大很多,M1,2过驱动电压将远小于M5,这就容易使M1、M2进入亚阈值区,这里M1、M2选择低阈值NMOS管。输出共模电平为980mV。

输入共模范围

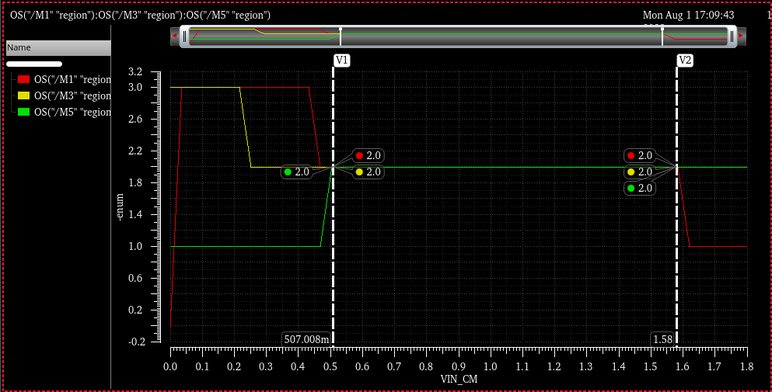

输入共模范围即放大器第一级所有 MOS 管工作在饱和区的共模输入电压范围。共模输入范围仿真方法如下:

calculator-OS可查看器件DC参数,选中M0、M3以及M5的region参数,查看器件的工作区域,其中region=0为关断区,region=1线性区,region=2饱和区,region=3亚阈值区,region=4击穿区。

DC参数扫描,设置变量为VIN_CM,扫描范围为(0,1.8V),扫描结果如下:

共模输入范围为(0.5V,1.58V)

输出电压摆幅

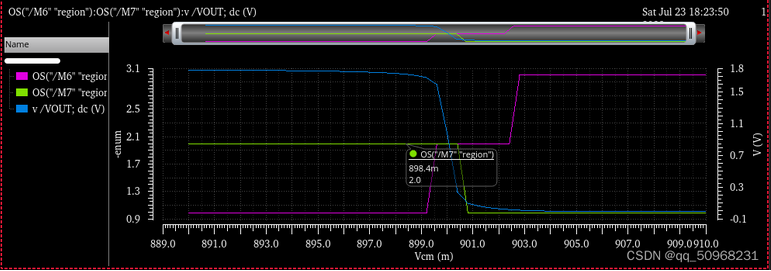

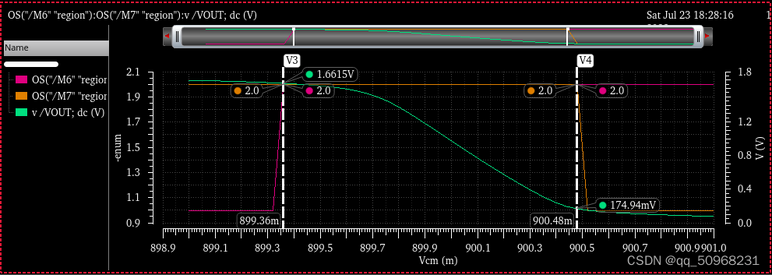

该两级运算放大器的最大输出电压摆幅为VDD-2*VDSAT,输出电压摆幅仿真方法如下:

在运放一端施加0.9V电压,另一端在0.9V±10mV范围内扫描DC电压,同时画出VOUT:

在0.9V±1mV范围内继续扫描DC电压:

输出电压范围为:(175mV,1.66V),输出电压摆幅为(1.66-0.98)×2=1.36V

3.2 ac仿真

幅频响应

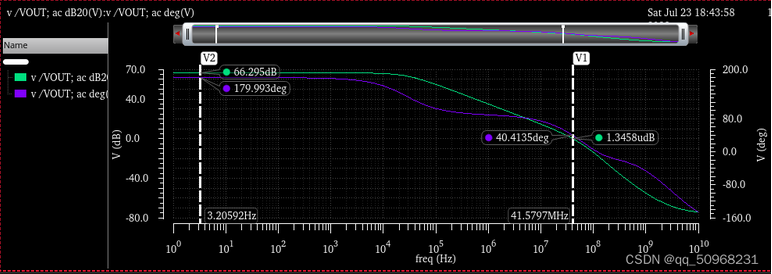

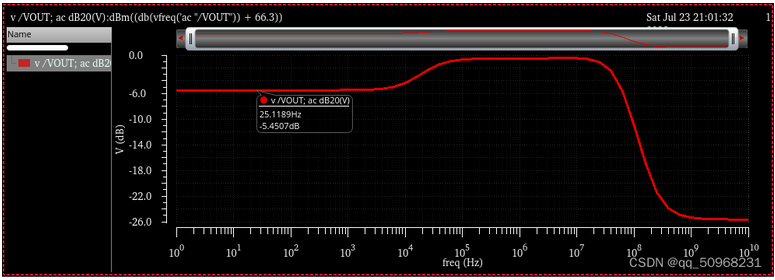

ac小信号仿真结果如下:

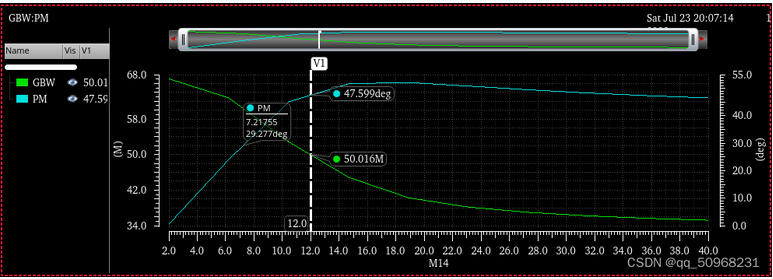

仿真结果显示GBW和PM均小于设计指标。PM小于45°,因此P2位于GBW内,且P2=gm6/2πCL≈100MHz>GBW。

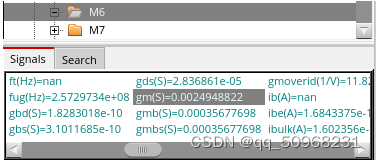

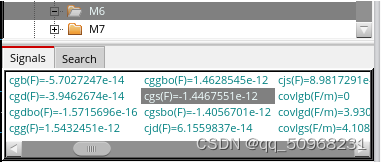

分析发现W/L6很大,导致其寄生电容很大(约为1.45pF),1/(RzC1)≈48MHz

将M6的W、L同时减半以减小该寄生电容,仿真发现:

Cgs减小为0.36pF,PM约为60.7°,GBW约为54.55MHz满足指标要求,但由于M6沟道长度减半,沟道调制效应变得更加显著,为了平衡M6、M7电流,输出共模电平升高,将极大减小输出电压摆幅。

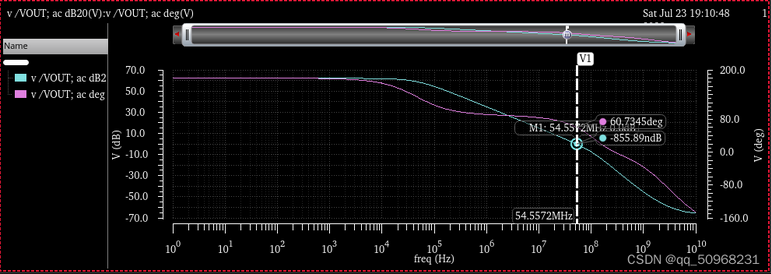

因此,仍保持M6宽长不变,尝试移动左零点补偿该寄生电容引起的极点。

M14的宽长比控制着Rz的大小,通过扫描M14的宽长比发现,当W/L14=12时,满足GBW指标要求,但仍不满足PM指标。

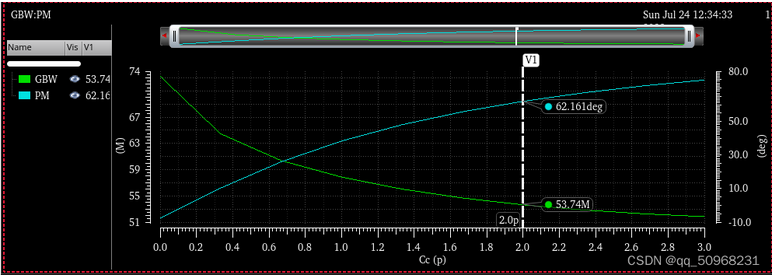

为了获得更好的PM和GBW指标,将W/L1修改为50,W/L10和W/L11修改为1,W/L14修改为9,对Cc值进行参数扫描:

Cc修改为2pF,PM和GBW均达到指标要求,适当的增大Cc可以获得更好的相位裕度,但Cc增大同时会减小GBW和压摆率。

PSRR

PSRR+:

正电源抑制比(66.3+5.45)≈72dB

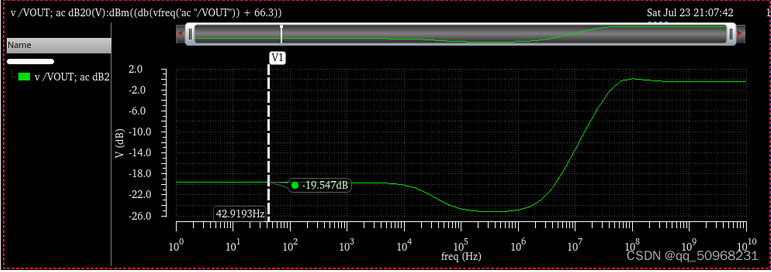

PSRR-:

负电源抑制比(66.3+19.54)≈86dB

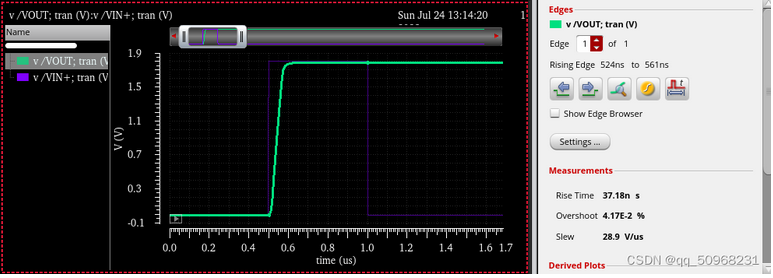

3.3 tran仿真

压摆率

给差分输入管一端施加脉冲阶跃信号,选择tran分析,画出VOUT输出曲线,点击measurement-transient measurement,仿真得压摆率为28.9V/us>20V/us

3.4 noise仿真

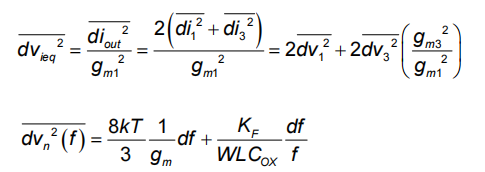

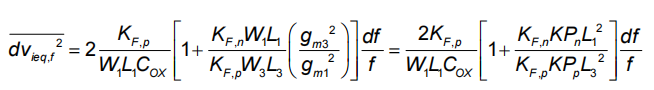

由于第二级噪声等效到输入端需要除以第一级增益,因此两级运放的噪声集中在第一级。输入噪声电压由热噪声和闪烁噪声两部分组成:

在中低频段,闪烁噪声为主要部分,其等效输入参考噪声电压为:

所以,一般采用增大输入管面积的方法来优化电路的噪声性能。

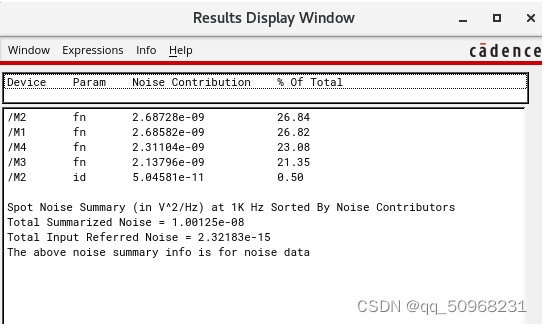

noise仿真结果如下:

输入参考噪声电压为48.17nV/ √Hz@1KHz。

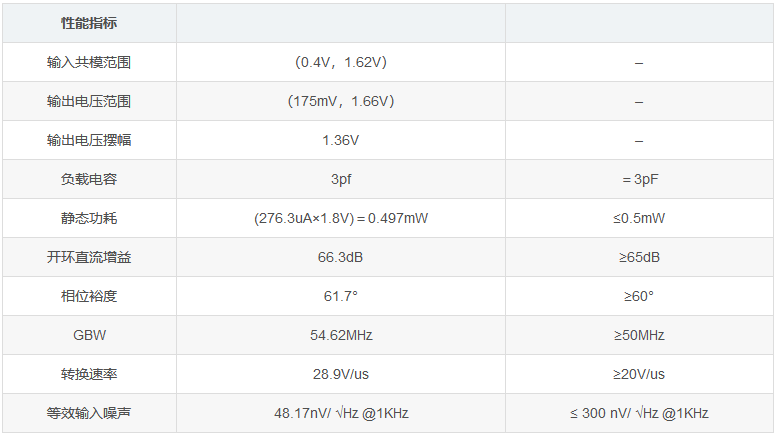

Cadence仿真结果见下表:

器件最终参数

性能指标

————————————————

版权声明:本文为CSDN博主「Metaa2227」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/qq_50968231/article/details/125905662

最前沿的电子设计资讯

最前沿的电子设计资讯