随着量子计算的出现,对外围容错逻辑控制电路的需求达到了新的高度。在传统计算中,信息的单位是“1”或“0”。在量子计算机中,信息单位是一个量子比特,可以描绘为“0”、“1”或两个值的叠加(称为“叠加态”)。

由于其高性能和低功耗,传统计算机中的控制电路都基于 CMOS(半导体)。传统计算机的“1”和“0”可以使用在室温下运行的 CMOS 芯片进行操控、存储和轻松读取。如今,大多数量子计算机都在低温下运行,以确保量子比特尽可能长时间地保持一致(处于叠加态)。在量子计算机中,一致的时间通常非常短(纳秒到毫秒),因此需要更多能够执行高速、容错操控的控制电路。如果传统的 CMOS 控制电路可以在低温下运行,则可以满足这一要求。

A.K. Jonscher 曾在《Proceedings of the IEEE》期刊上发表过题为“低温下的半导体”的文章,其中首次尝试描述低温下的半导体材料[1]。他的两个基本结论是:1) 由于“在这样的极端温度下进行大规模实验没有切实的技术理由”,半导体器件在当时没有重要的低温应用;2) “半导体材料在低温下的特性与我们熟悉的较高温度下特性有显著不同,因此可以合理地预期,通过在这个方向上持续进行研究和开发,将会出现更多的器件应用”。几年后,IBM 开始对低温下的半导体器件操控产生兴趣[2-3]并得出结论:MOSFET 半导体器件在低温下表现出更高的性能。低温操控虽有优势,但按比例缩小冷却装置仍然是使用基于半导体的控制电路的障碍。

进入量子力学。1959 年,Richard Feynman 向科学界提出挑战,要求在信息处理系统的设计中使用量子力学。他设想了涉及量子化能级和/或量子化“自旋”(量子粒子的角动量)相互作用的新信息系统和功能。这在1980 年代得到实现,当时证明了基于能量的量子力学方程可以代表通用的图灵(计算)机[4]。1994 年的研究表明,(“在多项式时间内”)量子计算机可以比传统计算机更快地分解整数[5]。这一发现激发了人们对构建量子计算系统的持续兴趣,直到今天在众多商业、研究和学术组织中还持续存在。

即使人们对构建量子计算机有浓厚的兴趣,但事实是,这种计算机的成功运行目前仍然需要低温环境,量子逻辑控制电路也需要在低温下工作才能高效运转。因此,我们看到人们对基于 CMOS 的电路的低温性能重新产生了兴趣。

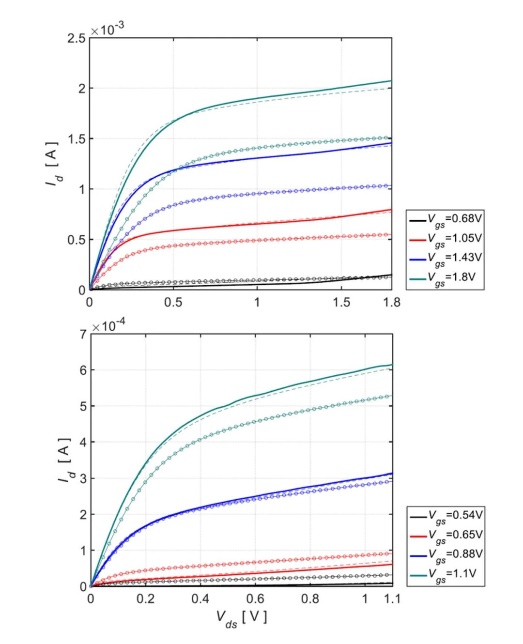

量子计算机不需要最先进的 CMOS 电路,但 CMOS 器件在低温和室温下的运行方式不同。最近研究人员分别在室温和 4.2 开尔文温度下,在 40nm 和 160nm 为主体的 CMOS 器件上测量了 CMOS 晶体管性能(以及相关的电流-电压特性)(如图1所示)。由于在这些温度下硅中的迁移率提升,低温下的驱动电流也将增加。不幸的是,基底冻结等其他因素会限制在这些低温下驱动电流的增加。

图1: 在 160nm(上)和 40nm(下)CMOS 中制造的 nMOS 晶体管测量电流-电压特性。点状曲线显示室温操控,实线显示液氦操控,短划虚线显示拟合实验数据的 Spice 兼容模型[6]

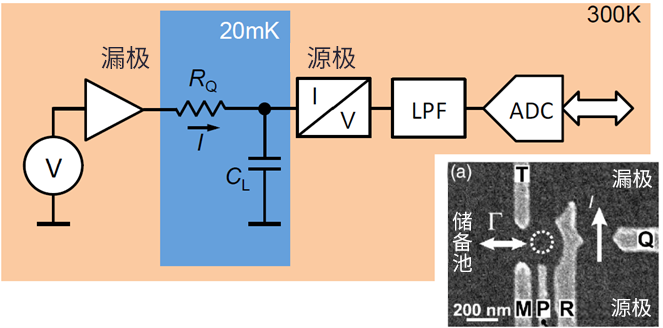

量子计算机的控制电路目前在室温下运行。如前所述,由于在较高温度下读取量子比特的“状态”很敏感,这可能成为一个问题。在与量子计算机一样的低温冷冻柜中,在低温或接近低温的情况下运行 CMOS 电路,可以部分缓解这一挑战。这种集成可以减少延迟并提高整体系统的可扩展性。尽管存在一些二阶问题,但低温下的 CMOS 晶体管可以执行与量子计算机一起工作所需的各种功能。这些功能包括以 I/V 转换器、低通滤波器以及模拟信号/数字信号间的相互转换等的执的能力(如图2所示)。

图2: 以虚线圆圈为中心的硅自旋量子比特、控制和读出信号(M、P、R、T 和 Q),以及量子点接触和配套电路的简化示意图。电压源极在室温下作为数模转换器[6]

为了实现容错量子计算机系统的预期性能,需要可以在极低温下运行的新一代深亚微米 CMOS 电路[6]。通过将这一想法推演为其合乎逻辑的结果,最终得到一个量子集成电路 (QIC),其中量子比特阵列与读取量子比特状态所需的 CMOS 电子器件集成在同一芯片上。这种集成显然是实现可扩展、可靠性和高性能兼备的量子计算的最终目标。

在未来的应用中,与量子比特之间的光通信可能也是必要的。在这种情况下,集成 CMOS电路还需要包括微米和纳米光学结构,例如光导和干涉仪。这些类型的光学功能已在室温 CMOS 器件上成功实现,在未来的量子计算应用中可能也需要在低温下实现同等级别的光通信功能。

原文链接:https://www.coventor.com/blog/quantum-computers-cmos-semiconductors-review-future-predictions/

最前沿的电子设计资讯

最前沿的电子设计资讯