在传统的登纳德缩放比例定律(Dennard scaling)大放异彩的日子里,我们经常会想起平面晶体管。其材料结构上的特性也被简化为片状电阻(只包含电阻电容等参数信息)。这样就会导致其器件是平面二维的抽象概念,而为了理解MOS管的底层电路设计,我们大部分的假设和建模也都设计为2轴。

慢慢的思路开始发生转变,二维设计开始被材料物理学特性所打破,越来越复杂的特性开始展示在科学家和工程师面前,最终MOS和三极管等器件诞生出了FinFET技术,一举将二维平面带入到“3D”时代。

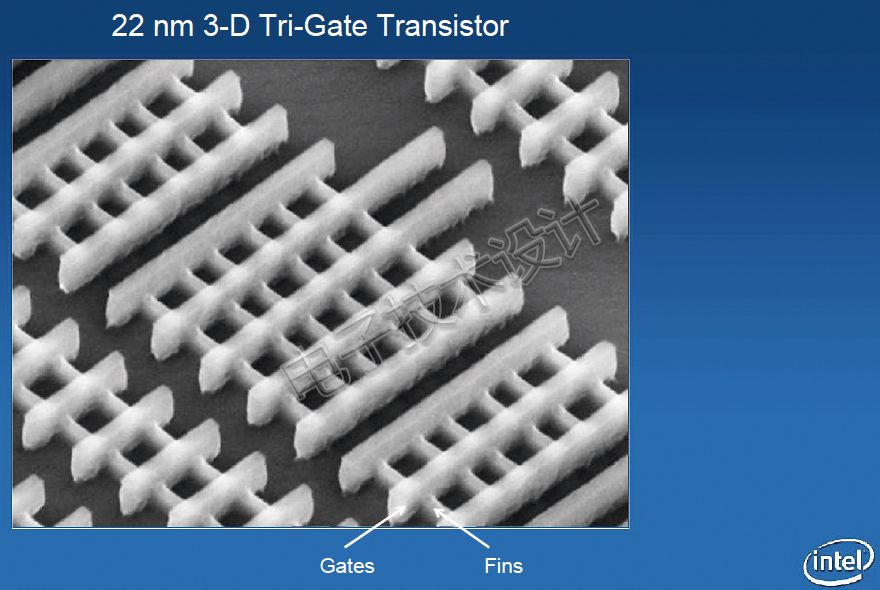

图1:来自Intel的原始三维FinFET。(图片来源:Intel)

当然技术路线的更新换代往往还伴随着名词和术语的重新调整、修改和复用等。而现代的技术人员继续使用“MOSFET”未免有失偏颇,毕竟其工艺和设计包括使用材料都截然不同(氧化物和高-K介质)。MISFET一词会更准确,读起来也比较容易,而且还有点像用来形容技术领域工程师的某个词(译者注:即MISFIT一词,这是作者的自嘲,形容不太合群、格格不入的人)。

最近Nature期刊的一篇在线文章“Promises and prospects of two-dimensional transistors”提供了对半导体技术未来发展的见解,探讨了硅基材料晶圆生产的终点。当然不仅是因为传统FinFET逐渐失去动力(图1),同时也因为未来的器件将足够薄(单层或两层),可以看成是二维的,不用说都知道,像硅这样的传统3D半导体在2D领域里效果不佳。

从材料学角度来看,还有一类被称为过渡金属二卤化物(TMD或TMCD)的材料,从材料学角度来看,还有一类被称为过渡金属二卤化物(TMD或TMCD)的材料,例如二硫化钼(MoS2)、二硒化钼(MoSe2)、二碲化钼(MoTe2)、二硒化钨(WSe2)和二硫化钨(WS2)。

前面提到的Nature期刊文章的主要作者是UCLA加利福尼亚纳米系统研究所的Xiangfeng Duan,以及中国湖南大学和韩国三星电子技术学院(SAIT)的研究人员,他们都指出TMD(过渡金属硫化物)材料在未来二维半导体材料生产中具备广泛的应用前景。

Nature期刊的这篇文章是最前沿的研究,当然我们可以从其他的资料中看看现今的技术发展路线。

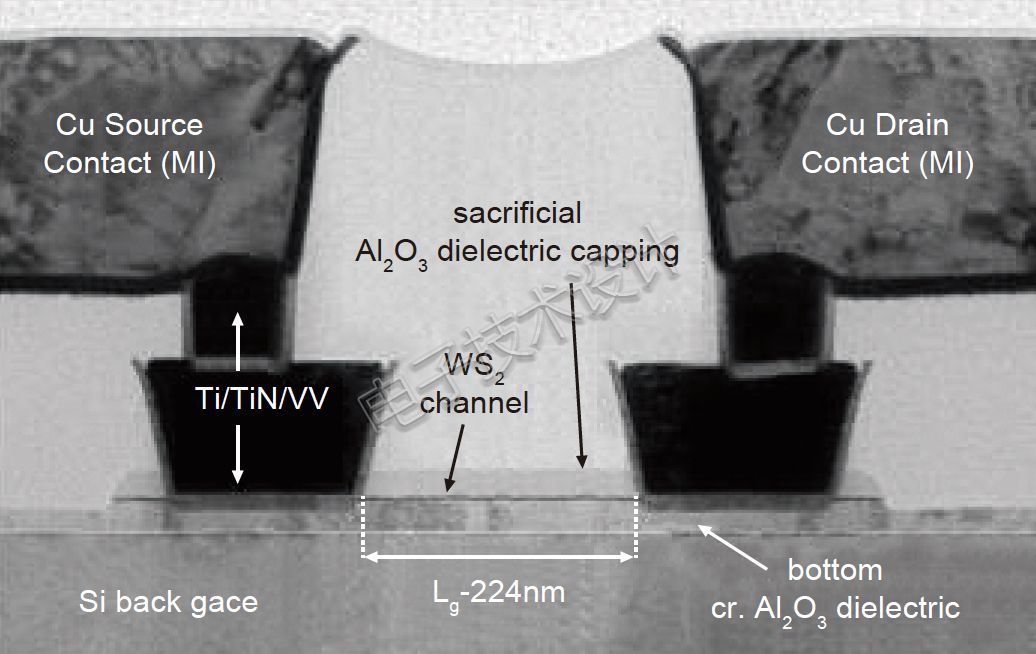

图2:IMEC 通道晶体管。(图片来源:IEEE)

在对未来的发展技术进行预测方面,微电子研究中心(IMEC)是最权威的机构之一。2020年12月举行的国际电子设备会议(IEDM)从多个角度讨论了从材料到“芯片结构”(可能特意避免使用“芯粒(chiplet)”一词)缩放的前景和未来。

为了使标准单元逻辑将来缩小到4轨道单元以下,IMEC寄希望于采用二维材料的晶体管。IMEC在路线图中定义未来的2D晶体管技术可以达到或超越“1nm”工艺节点,其展示了极性互补的堆叠“纳米片”结构制成的CFET晶体管,拥有四个轨道单元,每个大约在1.5nm左右。IMEC还指出,在近十年间,大量的技术革新和信息流动带动了整个产业发展。

IMEC正在寻找用于MOS管通道的新型材料WSi2(图2),IEEE报道称IMEC在300mm晶圆产线成功制造出了这种MISFET管芯片。

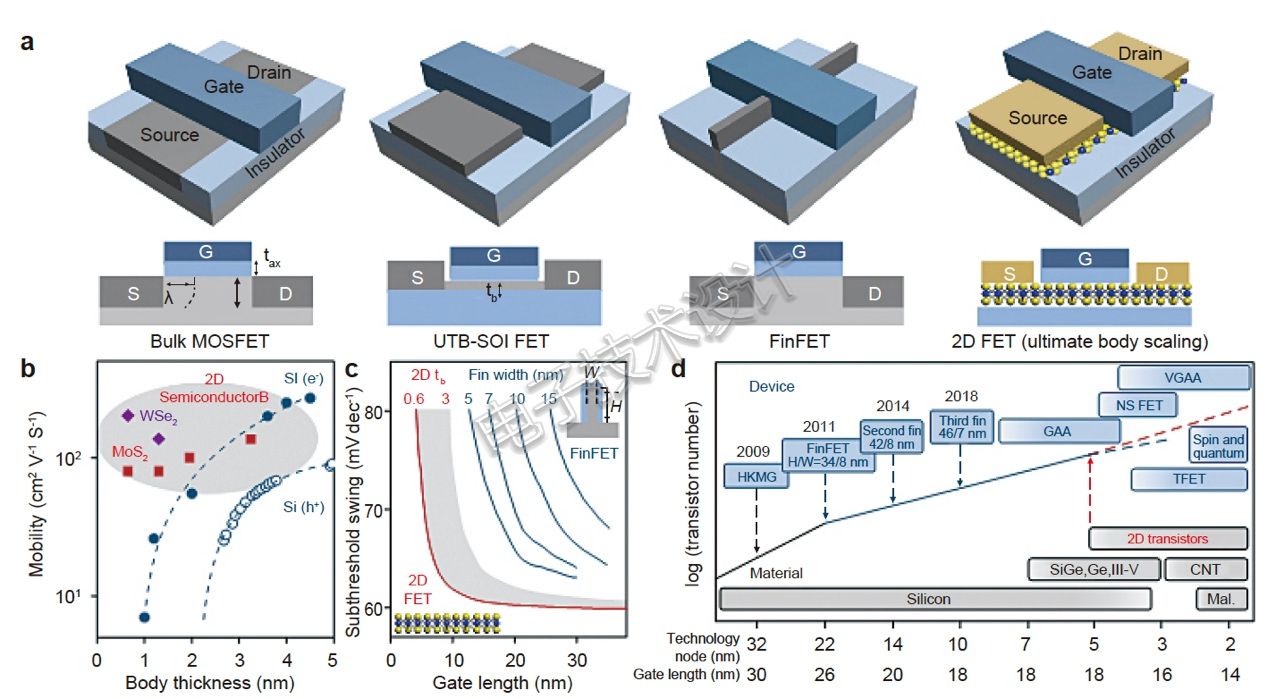

2015年发布的旧版International Technology Roadmap for Semiconductors(ITRS)最后预测,到2021年,硅CMOS晶体管的电流最大只有约1500µA/mm。Nature期刊引用了这篇文章,并重新预测了2021年的目标。图3比较了旧版与最新的官方路线图。

图3:从体硅MOSFET到二维MISFET。(图片来源:Nature)

ITRS已被能够更全面描绘微电子技术发展的International Roadmap for Devices and Systems(IRDS)所取代。旧的ITRS团队长期以来一直使行业保持在继有轨道上发展,但这并不是说不能对它进行调整以迎接新的挑战。

最新版IRDS在2020年发布可谓相当及时。许多老朋友因为IRDS又重新聚在了一起,还是熟悉的模式,但是对旧工作组进行了一些调整。我们最感兴趣的是深度摩尔(More Moore)和超越CMOS(Beyond CMOS)的路线图。

我们可以从最新的深度摩尔来看一看预测结果是否正确,传统CMOS的最大导通电流应略高于1700µA/µm。如果使用之前的ITRS路线图,新材料驱动电流数字更让人满意,所以之前是低估了硅材料的实力。这里只是将新型二维材料与常规技术进行比较,因此数据非常接近。

到目前为止,一切都还说得通,但我们还是要了解IRDS BC(超越CMOS)技术人员是怎么想的。毕竟我们不想像从前的人一样,想当然地就认为地球是平的。

一些人预测目前的技术会被淘汰,他们认为2028年将使用二维材料,这也是“1.5nm”节点的时间轴。

2D transistor review的作者提出,许多用于确定新材料适用性或衡量新材料发展进度的指标可能阻碍了半导体材料的发展。究其根本,还是性能决定一切,而不是看这些材料制造的器件的某些物理属性是否能打破实验室的世界纪录。

许多用于确定新材料适用性的指标可能阻碍了半导体材料的发展,因为器件性能至关重要——很多材料制造出的器件的某些物理性质不可能打破实验室的世界纪录。

对于实际应用中的缩放技术,功耗、性能、面积和成本(P-P-A-C)缺一不可。只有在各种因素达到工程平衡的前提下,新的晶体管设计和材料才能投入批量生产。

电流驱动能力是衡量晶体管的重要性能指标之一,就是我们所说的饱和驱动电流,其基准测量值为,在半导体行业以μA/μm为单位来测量。Duan和合作者提到,其他常见指标,如迁移率(µ)和接触电阻(Rc),可能无法说清问题。具体地说,这两个数据点有可能导致“模棱两可甚至相互矛盾的结论”。研究人员列举了一些报道,称高迁移率或低接触电阻并不能表明是高的驱动电流。

这篇Nature文章认为耗费精力改善迁移率或接触电阻没什么意义,研究人员往往为了解释晶体管获得的电流密度而绞尽脑汁进行器件建模。Duan及其同事希望使用同一个指标来比较二维晶体管与传统技术,以衡量下一代的高性能产品。不过,二维晶体管目前得到的最好数据是传统硅晶体管的一半左右(或更少,具体取决于使用什么TMD材料)。

缩小硅通道的问题在于,随着厚度的减小(目前采用5nm技术,未来基体厚度将小于3nm),迁移率会迅速下降。因此,TMD二维材料将比硅更具竞争优势,在1nm厚度以下可以轻松维持迁移率。

我们又在考虑迁移率了。奇怪吧?

我们来看一下硅。平心而论,这种半导体材料具有良好的特性,它的机制众所周知,硅薄层中迁移率下降及其背后的原因大家都能接受。

人们对二维材料的认识还不全面。不过,材料层的厚度已渐渐接近单原子厚度,迁移率的值却保持不变,这证明了人们对二维材料的理解大体正确。根据二维材料在未来技术节点中所具备的物理优势来看,这样的材料可以用于生产。

但是,IRDS路线图中提出的2028年将开始采用二维材料,在这之前肯定仍然存在很多问题。

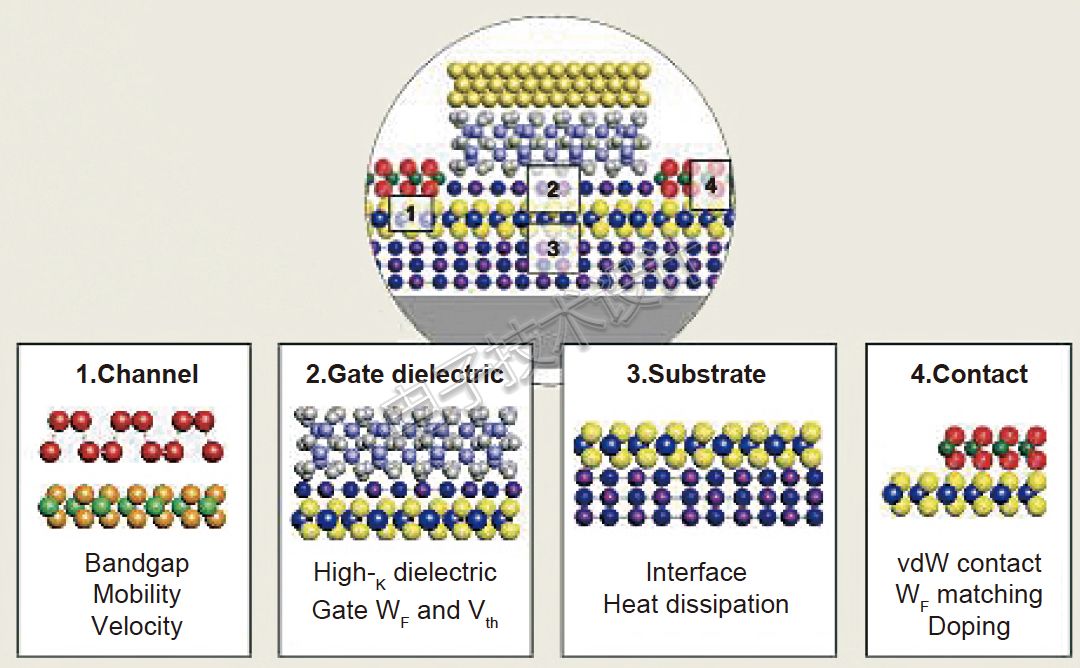

二维晶体管的最佳饱和驱动电流取决于四个主要因素:本征材料特性、接触电阻、半导体-介质界面和散热。图4显示了理想二维MISFET的四个关键要素。

在当前技术中,晶体管是利用重掺杂的源极和漏极区域来将接触电阻降至最低的。但二维晶格不能用这种方法,因为它只有一个原子那么厚。新器件需要一种新方法。现在已经提出了几种新的触点技术,并对边缘触点法进行了演示,还涉及既有潜力又有趣但还未经验证的横向金属-半导体异质结构。

Duan及同事则认为另一种有趣的新技术最有希望——直接的范德华(VDW)触点,这种技术可提供干净的界面和可调节的金属半导体势垒。Nature杂志的另一篇在线文章“2D Materials and Applications”更详细地介绍了VDW触点。

当所设计的器件厚度大约为一层一个至几个原子时,设计的成功明显依赖于是否选择了合适的衬底材料。需要考虑的一个主要因素是热性能,氮化硼(BN)具有较好的热性能,还能提供较高的界面质量,这反过来有助于二维晶体高-K栅极电介质的集成。

图4:理想二维MISFET的四个关键要素。(图片来源:Nature)

尽管在关键领域已取得了很大的进步,但通道材料、触点、电介质、热界面和器件几何结构未能同步得到优化。

要做的事还有很多,时间却很紧。只有等到三星或台积电宣布的那一天,才能真正知道谁是“1.5nm”工艺的最终赢家。值得一提的是,SAIT为此做出了重大贡献。

接下来,Duan及其合著者研究了新材料“从实验室进入代工厂”的情况。

尽管氮化硼所显示的特性极其适用于生产300mm衬底,但在这种尺寸上沉积TMD多数时候都会产生多晶而不是所需的单晶材料。

许多二维材料与堆栈中相邻层的粘合性较差,在加工过程中容易发生化学腐蚀,从而导致制造过程之中或之后发生层的剥落和器件故障。

我们暂且把这个主要的绊脚石放在一边。问题已经够严重了,就没必要再散布悲观情绪了。

台积电或三星将是未来新材料或新器件先进技术的践行者,我们目前还不知道他们的计划是什么,但是他们在工艺集成方面的卓越表现可能会推动二维晶体管的使用。

Nature文章的作者们意识到,二维晶体管需要“杀手级应用”才能投入生产——这是硅晶圆生产中资深玩家和巨额投资的老套了。作者认为,在可预见的未来,二维半导体不太可能完全取代硅。我不确定这里“可预见”指的是何时,因为2028年转眼就会到来。

答案可能在于3D集成。与通常出现在“超越摩尔(More than Moore)”解决方案中的3D系统集成不同,这里指的是真正的单片式3D集成电路。“由于二维晶体本身具有自立性和无悬空键特性,因此非常适合多层集成。”采用二维器件的一个主要问题是衬底,将它们堆叠在传统的硅前端可能可以克服这一挑战。

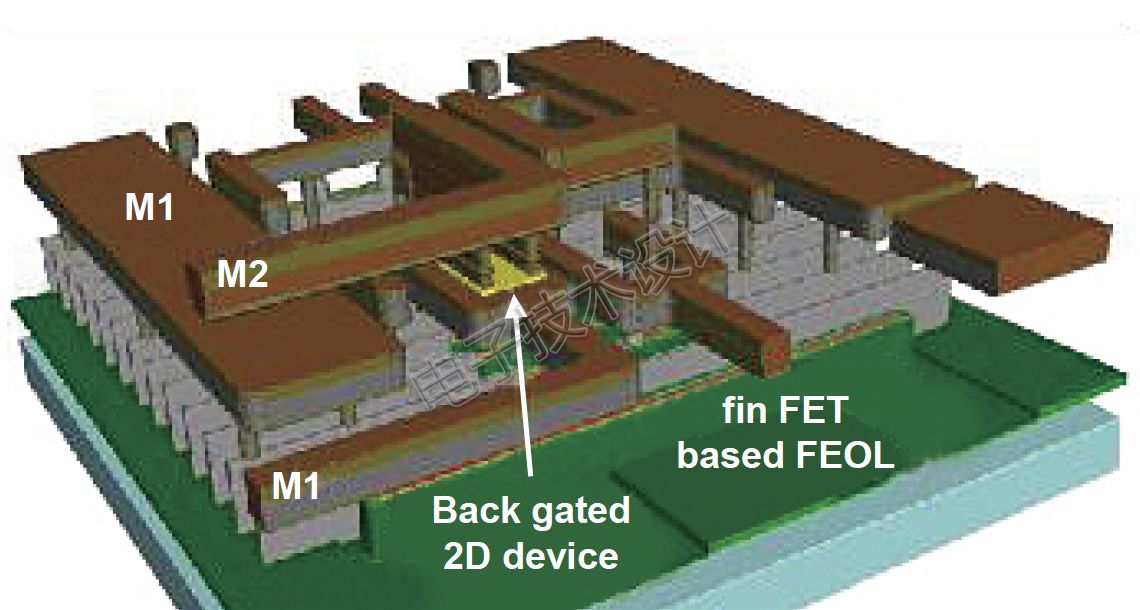

二维材料能够在比硅前端更低的温度下生产,而且二维材料可以采用目前的生产线后端(BEOL)金属化工艺。除了能够在同一晶圆衬底上提供有源电路层堆叠,集成到BEOL中还有另一个好处——就像IMEC所展示的晶体管那样,二维通道的背栅功能可以直接集成进这个流程(图5)。

图5:集成到标准金属化工艺中的IMEC背栅二维晶体管。(图片来源:IEEE)

二维技术另一种可能的应用是柔性电子器件。柔性器件通常采用有机半导体,其性能比采用二维材料要低好几个数量级。二维材料具有高性能和灵活性,“柔性、可折叠或适应不规则表面”的高速电路适合多种新的应用。

尽管面临挑战,Duan和他的合著者相信,从理论上讲,没有任何障碍可以阻止集成电路晶体管在工业领域使用二维材料。

未来使用二维晶体管看来是大势所趋。如果在几年前,这样彻底的改变是不可想象的。快速看一下技术路线图和所做的预测可以发现,在未来几年中,集成电路技术将发生巨大的变化,因此,二碲化钼这样的材料不断被提及就并不奇怪了。

当然,总有很多大事情会超出人们的预期。接下来是什么?如果我们一直降低维度,那么二维将降到一维。其中一项技术预言就是一维的碳纳米管晶体管。

必须承认,变化将是半导体技术领域永恒的主题。

(原文刊登于Aspencore旗下EETimes网站,参考链接:Chip Makers Must Learn New Ways to Play ‘D’,由Jenny Liao编译。)

本文为《电子技术设计》2021年5月刊杂志文章,版权所有,禁止转载。免费杂志订阅申请点击这里。

责编:Jenny Liao

最前沿的电子设计资讯

最前沿的电子设计资讯