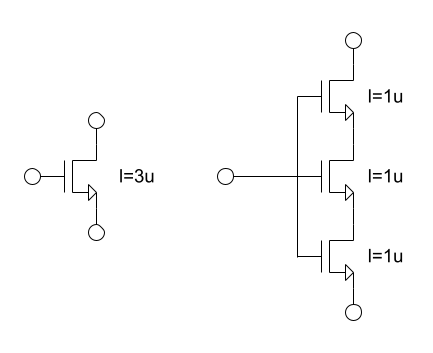

在28nm以下,由于最大器件长度限制,模拟设计人员经常要对多个短长度的MOSFET串联来创建长沟道的器件。这些串联连接的器件通常被称为堆叠MOSFET或堆叠器件。例如,将三个1μm的MOSFET串联堆叠,可创建一个沟道长度为3μm的有效器件(图1)。

图1:将三个MOSFET串联堆叠,可提供3μm的沟道长度。

堆叠MOSFET在现代模拟设计中非常常见,但并不是没有问题。其主要问题是电容增加以及面积更大。电容增加很大程度上是由于器件周围的互连增加。总栅极面积和总栅极电容与非堆叠等效电路相似,但在互连线上有额外的寄生电容。与单个长沟道器件相比,堆叠器件的物理分离增加了总设计面积。

当在电路中使用堆叠MOSFET时,版图质量变得比平常更重要。不良的版图设计会显著增加寄生电容和设计面积,并可能使电路无法满足期望的性能特性。版图设计工程师必须非常小心地设计这些器件的版图。大多数从事于这些较小工艺节点的设计人员都经历过版图前仿真和版图后仿真非常不同的情况。通常,这归因于堆叠器件上所存在的互连寄生效应。

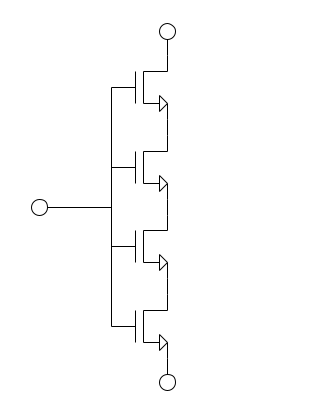

下面来看看几种实现堆叠MOSFET高质量版图的方法。图2中的子电路显示了将四个NMOS MOSFET堆叠在一起而创建一个长沟道器件。

图2:将四个MOSFET堆叠,可创建一个长沟道电路。

在这个电路中可以看到,所有的栅极引脚都是相互连接的(所有四个整体连接也是如此),也可以看到,所有的MOSFET都是通过将一个器件的漏极与下一个器件的源极串联起来而连接在一起。在这种情况下,由于每个器件都是简单的单指MOSFET,因此可以使用简单的扩散分配版图模式来设计这种结构的版图。

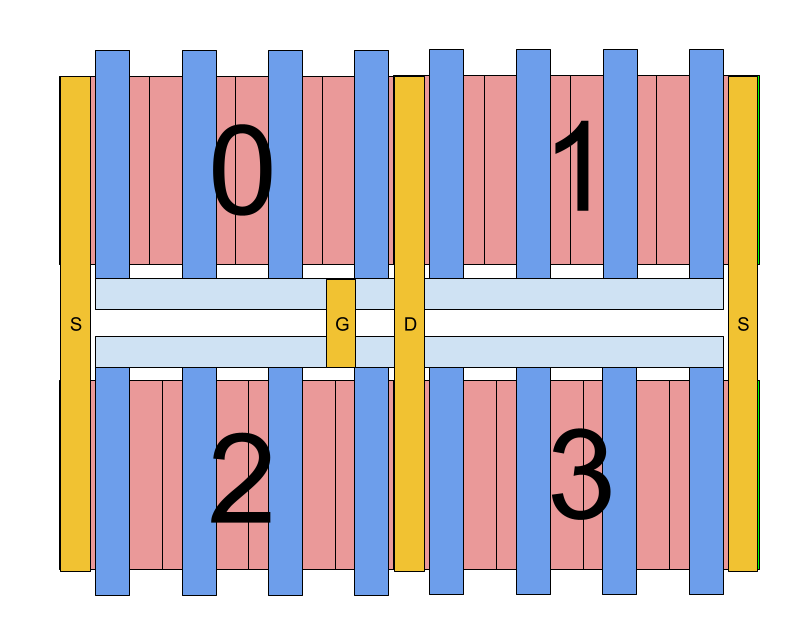

图3:将左边的简单堆叠情况与右边的等效长沟道器件进行比较。

简单堆叠情况的版图如图3左边所示,可以看到它几乎没有额外的互连,因为等效的长沟道器件(右边)也需要一个多晶硅触点。在这种情况下,面积不利显著,但这是不可避免的,并且由多晶硅最小间距规则所决定。

这种方法的另一个问题是,非常长的有效器件可能导致非常长的扩散分配链路。然而,可以将长链折叠成多行,如图4所示。但是,其代价是这增加了额外的互连,并进一步增加了堆叠器件的电容。

图4:可以将长链折叠成多行。

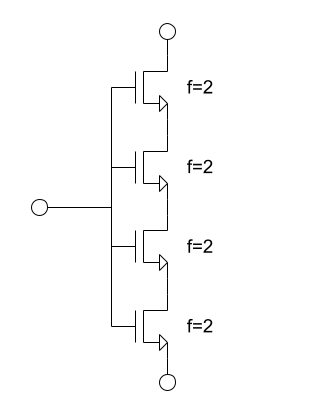

图5中的电路显示了电路设计人员想要在电路中使用两指MOSFET来实现更好匹配的情况。

图5:可以在电路中使用两指MOSFET实现更好的匹配。

两指器件不能通过扩散分配连接,因此必须使用不同的布局和布线方法。为了实现紧凑的版图,器件是按列来连接的,而不是前面示例中所示的按行模式。

图6:按列进行连接(左侧);这种按列模式的布局机制如右侧所示。

在图6中,左图显示了连接模式,也即将一个器件的漏极与下一个器件的源极垂直相连。如图所示,连接是按列的方式进行的,交替器件的不同参数在MOSFET的漏极中心变体和源极中心变体之间进行交换。交换的触点使列中的器件之间可以进行直线布线,从而就可避免弯曲以及额外的过孔。

在右侧可以看到这个按列模式的布线模式。有额外的互连,但与通常的接触增强所需的互连相比并不会明显增多。

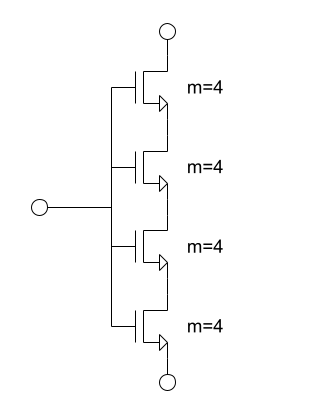

电路设计人员也可以为堆叠的器件指定m因子。堆叠m因子拓扑使电路设计人员可使用多个小型MOSFET构建具有长、宽沟道的器件。图7显示了m因子为4的单指堆叠器件。

图7:具有m因子拓扑的单指堆叠器件。

在图7的版图中可以看到,这种模式中包含了前面按行模式的四个副本,这样一来就可确保器件之间额外布线的数量最少。

本文中展示了一些可用于堆叠MOSFET的基本模式。在上述所有例子中,器件的布局和布线是实现高质量版图设计的关键。

Pulsic的Animate Preview工具中的技术将布局和布线结合在一次操作中。这使Animate Preview可以为堆叠器件实现上述最佳版图设计模式。每个器件的准确位置、方向和参数化都必须经过优化才能获得期望的结果。同时,该工具还必须考虑流经每个器件的电流,从而最大限度地降低互连的复杂性和长度。模拟版图设计总是需要仔细平衡多个竞争优先事项,没有一种行事方式能在所有情况下都有效。

(本文授权编译自EDN电子技术设计姐妹网站Planet Analog,原文参考链接:All about stacked MOSFETs in analog layout。由赵明灿编译。)

本文为《电子技术设计》2021年9月刊杂志文章,版权所有,禁止转载。免费杂志订阅申请点击这里。

最前沿的电子设计资讯

最前沿的电子设计资讯