首款专为低带宽单通道传感器设计的商用现货(COTS)模拟前端(AFE),展示了模拟至数字集成的功能。然后,面向超声成像等应用的COTS AFE,证明了匹配多个输入通道如何能够提高性能。现在,雷达、5G和其他应用需要更高的采样率以及优化的匹配通道,这正在改变AFE的格局。

ADC和DAC更高的采样率,只是改变之一。零中频或直接采样架构也在获得动力。接下来,调制从模拟域转向数字域,AFE与数字处理实现紧密集成。在此,在这个设计的十字路口,COTS器件能否提供足够的灵活性以在一系列设计中获胜,或者,使用模拟IP块的定制AFE设计,是否能够接管高端市场呢?下面来快速浏览一下快速采样AFE竞赛中的一些条目。

汽车雷达芯片组引起了业界极大的兴趣,尤其是在自动驾驶场景中。在宽温度范围和成本是重要考虑因素的情况下,许多设计团队决定采用调频连续波(FMCW)设计来简化芯片组。

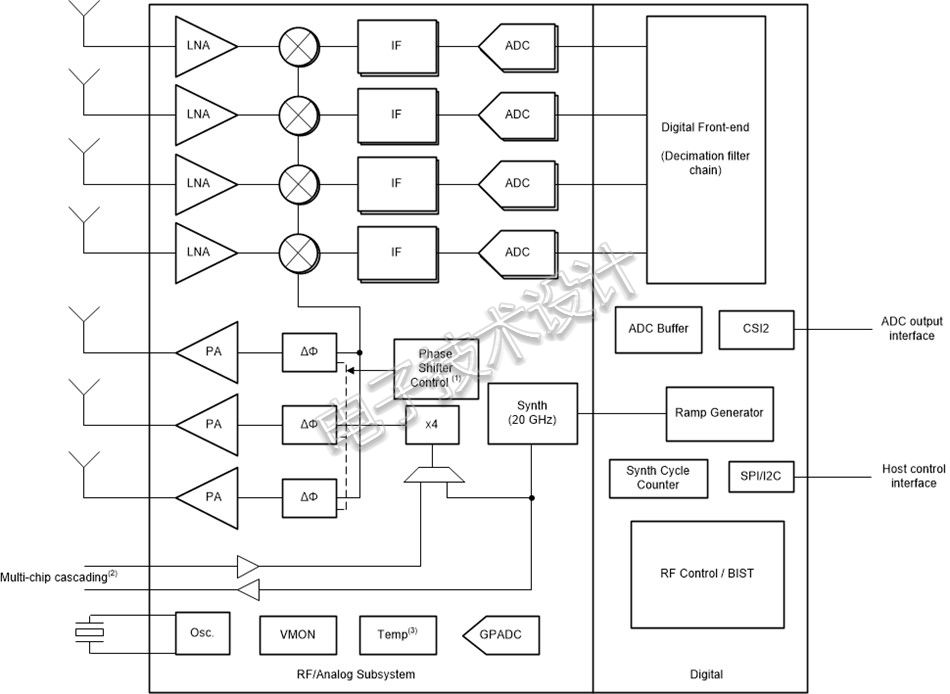

德州仪器(TI)已构建了一系列FMCW器件,从第二代AWR2243雷达AFE(图1)开始。它结合了四个接收器和三个工作在76-81GHz的发射器,并支持芯片到芯片同步以扩展通道。其45MSPS采样率可处理20MHz的IF带宽以改进检测。该模块与单芯片AWR1843雷达处理器中的处理器和DSP内核进行集成,具有25MSPS和10MHz中频带宽。

图1:AWR2243雷达AFE具有芯片到芯片同步功能以扩展通道。(图片来源:德州仪器)

在国防和航空航天应用中,原始性能通常占主导地位,而雷达信号处理则通常是专有的。随着相控阵元件数量的增加以及复杂性转移到数字域,具有可编程功能的灵活的AFE就可以胜任。在此,射频前端芯片可以帮助配置特定的雷达频率范围。

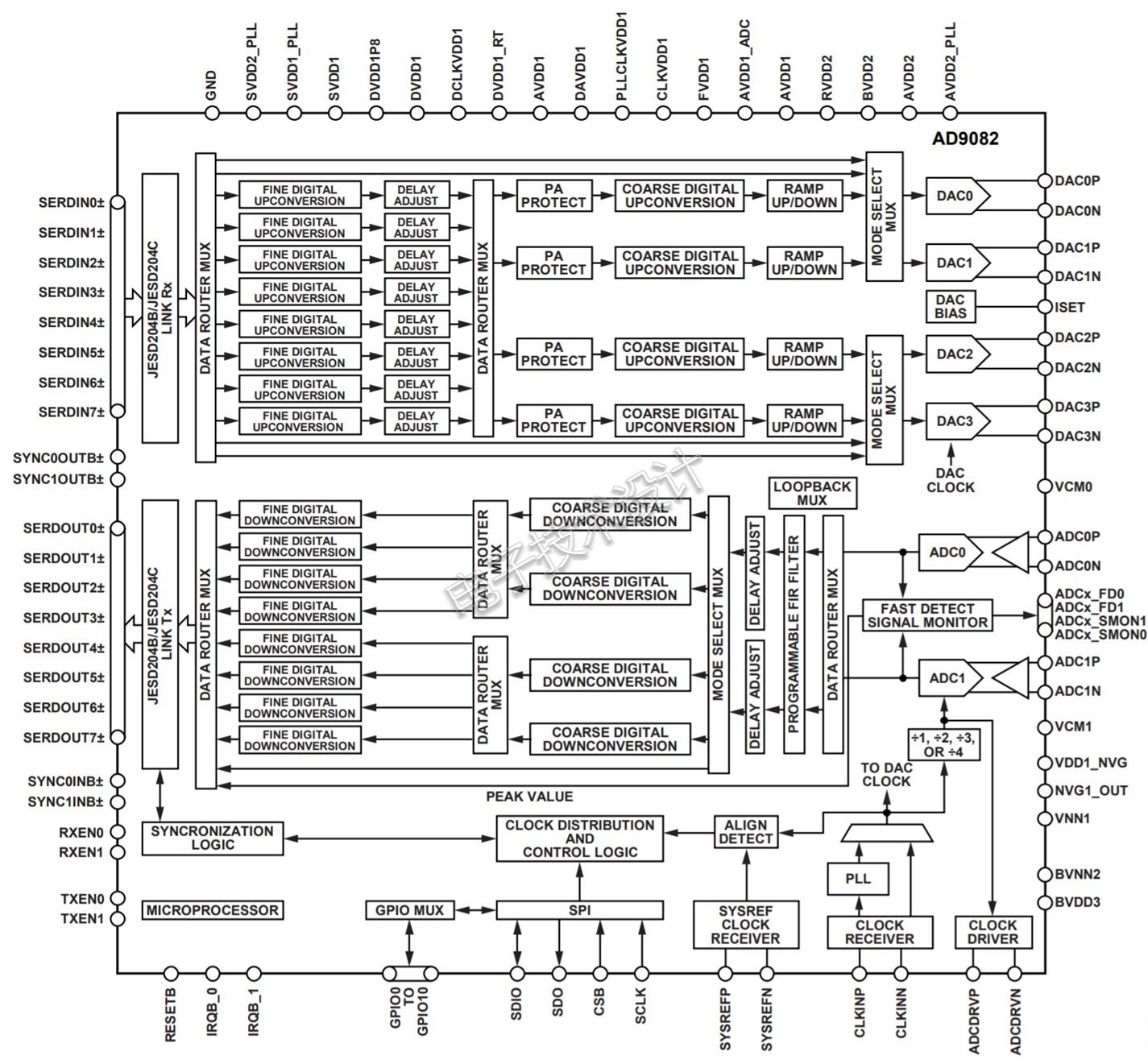

ADI公司推出了一个软件定义平台,可用于相控阵处理及其混合信号前端或MxFE。AD9082 MxFE提供了两个12位、6GSPS ADC和四个16位、12GSPS DAC(图2)。它在ADC端提供了数字下变频和可编程有限脉冲响应(FIR)滤波以及延迟调整,并在DAC端提供了数字上变频——如果需要,所有这些功能都可以旁路掉。此外,多芯片同步还可以对更大的阵列进行通道调整。

图2:AD9082模拟前端具有多芯片同步功能,可以对更大的阵列实现通道调整。(图片来源:ADI)

许多设计人员一直在使用他们所需的确切数字IP块来设计高度优化的定制芯片,以便节省功耗和空间。因此,直到最近,5G和雷达等应用的设计人员不得不选择具有GSPS级别速率的独立ADC和DAC。现在,市面上出现了一批GSPS ADC和DAC IP模块,可以支持具有类似优化的定制芯片设计。

Alphacore公司在低至GlobalFoundries(GF)22nm的各种工艺节点上拥有广泛的ADC和DAC IP模块。其28nm节点的10位ADC以2.4GSPS运行,功耗仅为6mW,而GF 22nm节点的8位ADC则以40GSPS运行,功耗为194mW。GF 22nm节点的12位DAC则以6GSPS运行,功耗为121mW。

Omni Design公司则提供基于其SWIFT运算放大器架构的高采样率ADC IP模块,该架构可将功耗降低,其节点低至28nm。其14位ADC的运行速度为1.2GSPS,而12位ADC的运行速度则为6GSPS。Omni Design的DAC IP模块运行速度则高达18GSPS。

Synopsys公司也具有快速模拟模块,特别是在IQ模式下具有3GSPS速率的12位ADC,以及具有4GSPS速率的12位DAC。该公司在一篇题为“Very High-Speed Data Converters for 5G Analog Front-End(用于5G模拟前端的超高速数据转换器)”的博客文章中发布了一些设计人员使用高采样率模块所面临的挑战。

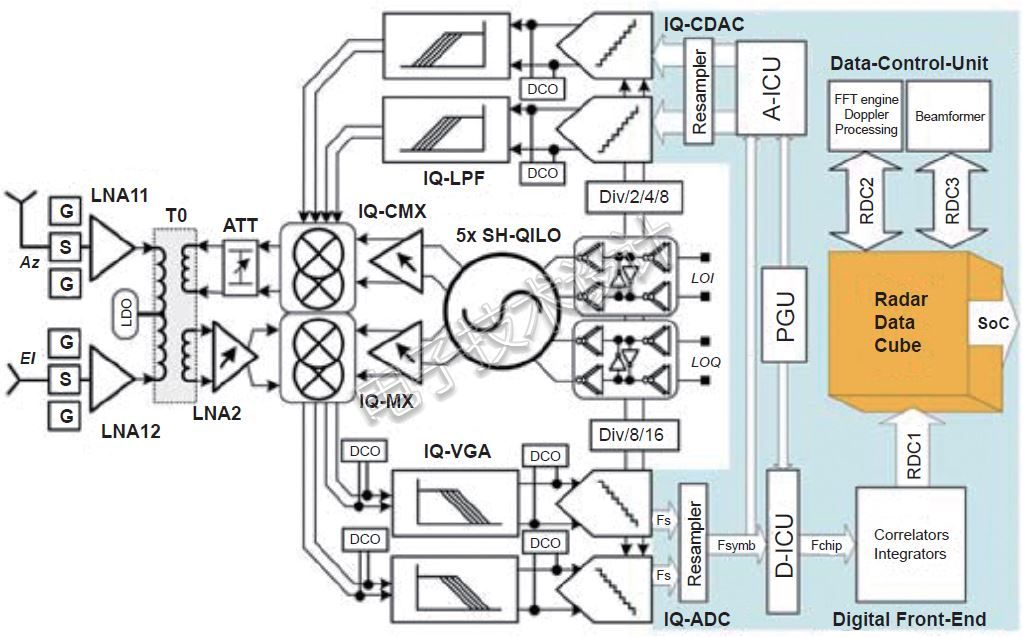

图3:该MIMO雷达SoC接收器的框图,突出了以IP为中心的系统级创新。(图片来源:Unhder)

使用诸如此类的IP块,开启了系统级的创新。Unhder公司就创建了一个很好的例子:面向汽车应用的频率为77-79GHz的192路虚拟接收器GMSK码域MIMO单芯片雷达(图3)。八个专有接收器块中的每一个都有两个天线输入(一个用于方位角,一个用于仰角),以及一个复杂的抵消反馈方案。接收器ADC(不知道这是谁的IP)在零中频架构中以2GSPS运行。

对于商业半导体供应商来说,提供满足最前沿速度的严格性能要求的AFE,变得更加困难。这需要对一个应用进行过多的调整,最重要的是,市场是有限的。为了实现灵活性,其中内置了太多的额外功能,因此从长远来看,设计人员可能会寻找更优化的定制芯片。此外,商业供应商必须首先证明其独立的ADC和DAC技术,直到AFE集成讲得通。

两种方法的挑战都是要在通道之间匹配转换器性能。例如,对多个ADC进行时间交错,就至关重要。以Teledyne SP Devices公司的ADX技术为例,该技术提供了数字后处理,可估计ADC之间的失配误差并对其进行抑制。

就目前而言,我认为在定制芯片设计中采用GSPS级模拟IP块的方向还摇摆不定,直到这些高采样率变得普遍并且有大概的应用出现而使得现成的GSPS AFE在经济上可行。更紧密的数字集成,也有利于模拟IP块方法。这将是一个有趣的观察空间。

Don Dingee在General Dynamics公司从事导弹制导系统工作十年后,成为摩托罗拉VMEbus和单板计算机技术的布道者。他为Planet Analog撰写有关传感器、ADC/DAC和信号处理的文章。

(本文授权编译自EDN电子技术设计姐妹网站Planet Analog,原文参考链接:Fast-sampling analog front-ends: COTS or custom?。由赵明灿编译。)

本文为《电子技术设计》2021年10月刊杂志文章,版权所有,禁止转载。免费杂志订阅申请点击这里。

最前沿的电子设计资讯

最前沿的电子设计资讯