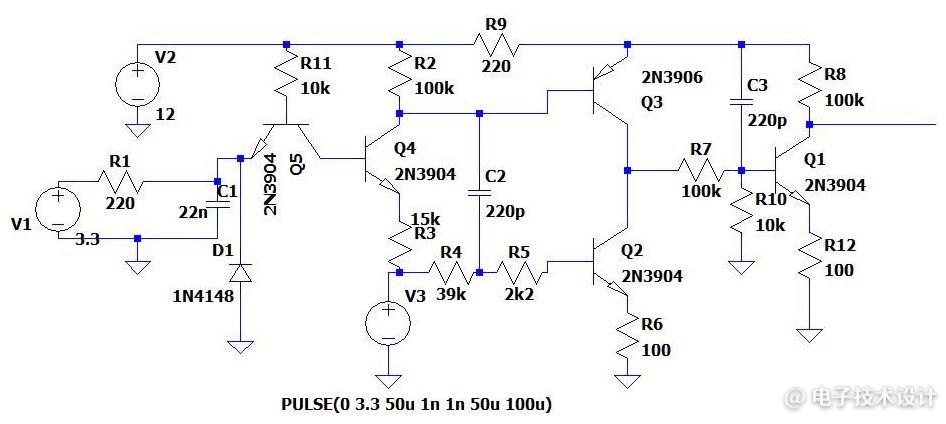

本文所示的是围绕二象限驱动器电路设计的PWM放大器电路(图1),该电路可以将3.3V或5V信号放大到更高的水平。

图1:围绕二象限驱动器电路设计的PWM放大器电路。

在此,R1和C1对晶体管Q4构成一个适度的滤波器。Q5发射极上的3.3V电压将对Q4的基极发射极结产生反向偏置,并使电流通过R11流向Q4的基极。流经Q4的电流驱动Q3和Q2,且该电流取决于PWM的水平。当PWM接近3.3V时,从Q4流出的电流减少,这使得Q3处于非活动状态,而Q2则会吸收电流。在0V时,210μA的电流流过Q4,这将使上拉晶体管Q3导通。因此,来自二象限驱动器的输出信号将发生反转。

该电路为三个双极型晶体管(BJT)添加了三个衰减电阻器,这将使输出的最大电流实现最小化,并且它们还能消除PWM信号边缘的直通。此外,它们还提供了一定的输出短路保护。

C2和C3的添加,能进一步减少直通。来自二象限驱动器的PWM输出受到反转,电路添加了带衰减的共源极级,这能为我们提供原始PWM信号的放大反射。可以在输出端添加一个缓冲器来驱动RC模拟PWM转换器等负载。

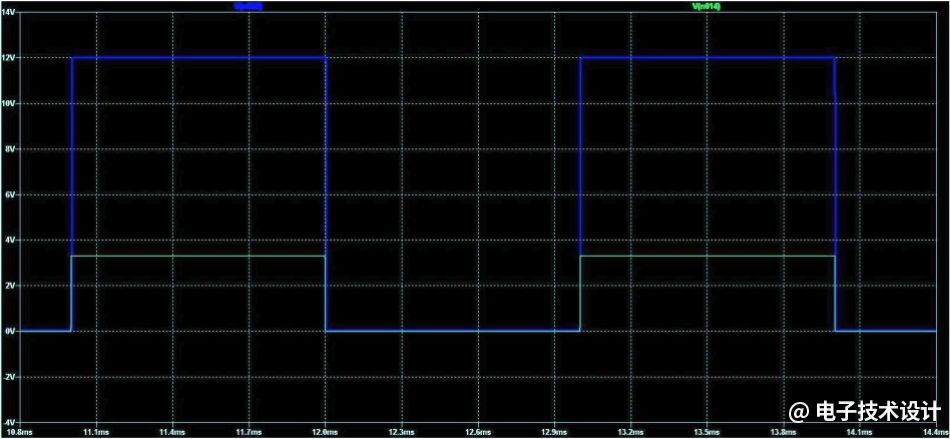

电路在500Hz时的响应如图2所示。

图2:500Hz时的响应。

在低频时,响应非常好,边沿很陡,转换速度与原始PWM信号一样快。此外,延迟可以忽略不计。

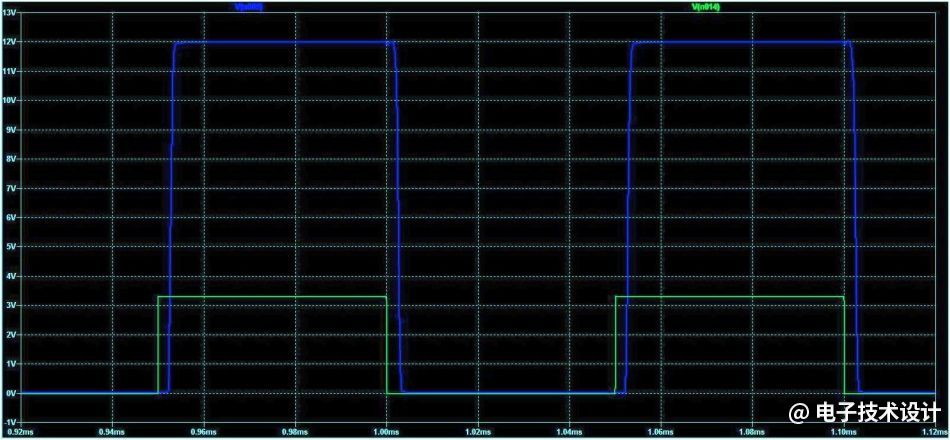

10kHz时的响应如图3所示。

图3:10kHz时的响应。

在10kHz时,可以观察到传播延迟,而且现在的转换速度也没有那么快。

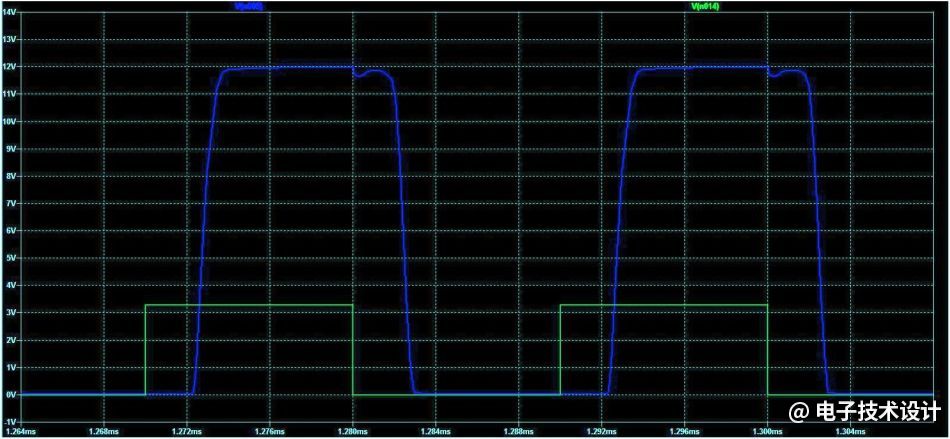

50kHz时的响应如图4所示。

图4:50kHz时的响应。

在50kHz时,响应变得更糟,但仍然没有那么糟糕。在此,关断瞬态有一个下降,传播延迟也非常显著。

因此,结果表明,该电路在高达10~20kHz的频率下具有非常好的性能。在更高的频率下,响应性能虽然有所下降,但仍然没有直通和其他噪声行为发生。

(原文刊登于EDN美国版,参考链接:PWM amplifier using a two-quadrant drive circuit,由Franklin Zhao编译。)

本文为《电子技术设计》2021年12月刊杂志文章,版权所有,禁止转载。免费杂志订阅申请点击这里。

最前沿的电子设计资讯

最前沿的电子设计资讯