如果去看任何CMOS模拟IC的原理图,就会看到NMOS和PMOS晶体管以及电阻、电容和电感的符号。还可以看到有导线(用于确定电路连接)将这些符号连接在一起。基本来讲,为电路设计版图的过程,也就是为此类符号绘制半导体几何图形,然后用导线将它们连接在一起。在大多数情况下,符号的几何形状由参数化代码所定义,形式为Cadence PCell或iPDK PyCell。然后,连接线则通常由版图设计人员手工绘制而成。

但是,除电路符号和导线之外,版图设计人员还必须为电路的实际工作设计一些其他结构。这些附加结构有一部分会在原理图中显示,有一部分会在后续的反标注过程中被添加到原理图中,还有一部分结构不会在原理图中显示,而其存在与否必须由设计人员来暗示。原理图不是详细的设计图,而更像是电路的架构草图。版图设计人员的职责是利用他们的培训和经验来解释原理图,进而创建出成功的版图。下面来看看这些额外的结构及其作用。

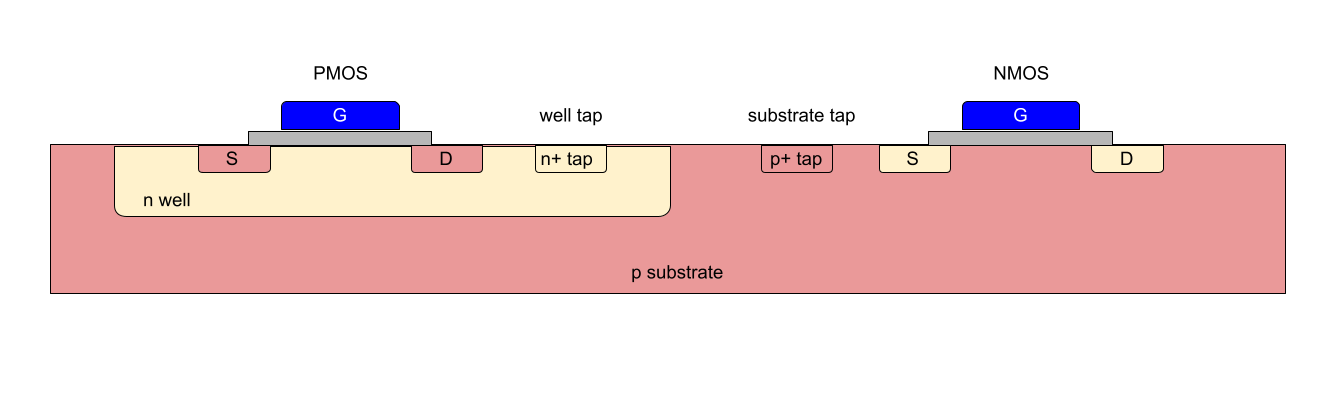

大多数CMOS工艺采用P型衬底制造,而NMOS器件则通过植入N型源极和漏极结构制造。要制造PMOS器件,就需要一个N型材料区域。N型材料称为N阱,它围绕P型源极和漏极结构产生MOSFET沟道。版图中必须要绘制出N阱。其通常包含在pcell/pycell代码中,但是版图设计人员要负责将这个区域扩展到单独的晶体管之外,并围绕一组器件产生连续的N阱。

MOSFET晶体管的性能对N阱和P型衬底的电位非常敏感(在深N阱工艺中则是P阱)。阱中的电荷积聚会改变晶体管的特性,因此必须谨慎管理,通常的做法是(但不总是)要确保在N阱的情况下使该阱与电源之间有良好连接,在P阱的情况下使该阱与地之间有良好连接。可以将抽头和/或保护环插入到版图中来实现这种连接。保护环本质上是一个环绕在晶体管周围的环形抽头。抽头和保护环也可以降低闭锁的可能性,否则就会在电源轨之间形成低阻抗路径,从而在电路中产生破坏性大电流。

图1:带抽头的PMOS和NMOS器件。

保护环除了可保持阱的电位之外,还有助于隔离敏感器件,使之避受来自电路其他部分的电荷流动和电气噪声的影响。因此,保护环在模拟设计中得到广泛应用。典型的四端MOSFET的原理图符号,指定了阱的连接性,但没有在原理图上绘制抽头和保护环结构。版图设计人员必须知道其插入的方法和位置。

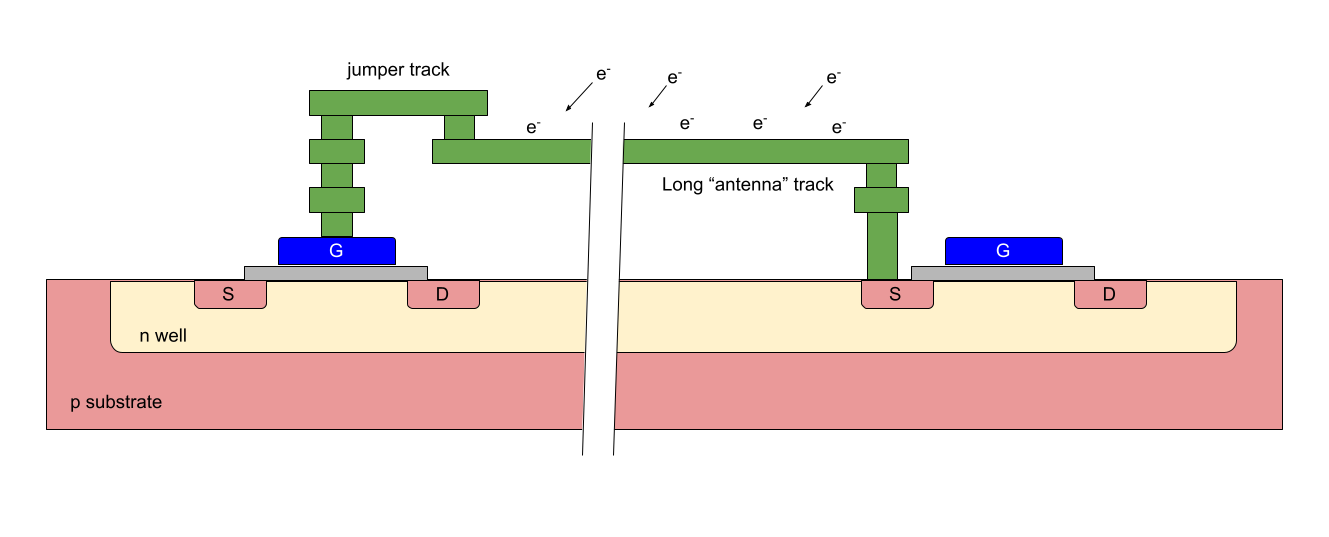

另一个未在原理图上出现的关键版图结构的例子,是将跳线和/或二极管插入,从而保护免受所谓的天线效应的影响。

IC制造过程涉及到材料沉积、掩模和等离子蚀刻的多次迭代。每次迭代都会增加一层材料,然后使用高能等离子体去除多余的材料。随着层数增加,就会出现长金属走线只连接到MOSFET栅极的情况。这些长走线会收集来自等离子体无法通过栅极氧化层“逃逸”到衬底的电荷。如果栅极上积累了足够的电荷(因此产生电势),就会导致氧化物薄膜分解,从而破坏或损坏MOSFET。在版图中添加跳线和/或二极管,就可以避免这个问题。

图2:断开的天线跳线走线。

可以利用跳线断开靠近栅极的长轨道,而将制造过程中积累的电荷减少到安全限值以下。跳线的构造使得长轨道仅在其也连接到扩散触点时才会连接到栅极,然后,扩散触点就可使电荷通过扩散到衬底上而实现消散。或者,也可以在栅极附近放置一个反向连接的二极管。二极管不会减少天线效应,而会使电荷在制造过程中安全消散,但其在工作过程中对晶体管的影响又最小。

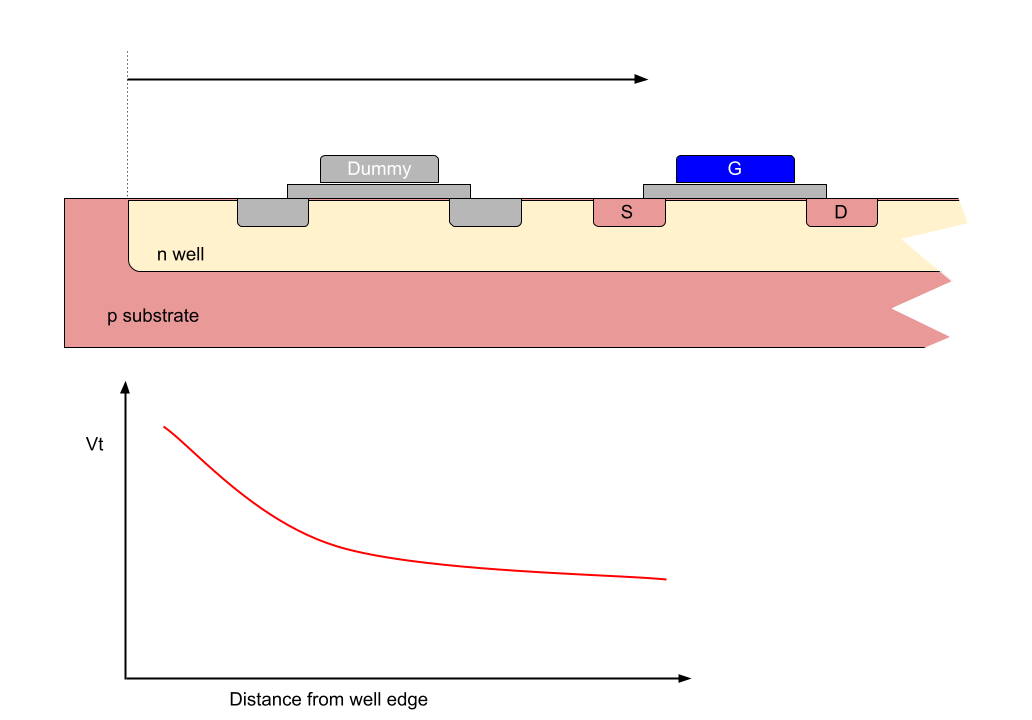

如果需要匹配器件,那么很多工艺都要求设计人员在版图中插入虚拟器件。后续工艺需要在所有器件的每一“行”的末端添加虚拟器件。当在硅片中进行蚀刻时,虚拟器件有助于确保一组匹配器件(例如电流镜)中的每一个都具有相同的几何形状。通过在版图中重复图案,就可以将由亚波长图案化所产生的光学变形最小化。工艺工程师可以在一定程度上使用光学工艺修正(OPC)等技术,但最好是产生统一的图案化版图。在这些图案改变的地方,硅片与所绘制的版图偏离最大。版图设计人员可通过在匹配结构周围插入虚拟器件扩展图案,也即匹配器件位于蚀刻图案的中心。

虚拟器件有助于匹配的第二个原因是可减少某些其他类型的版图依赖效应(LDE)。例如,虚拟器件可通过增加匹配器件与阱边缘的距离来降低阱邻近效应。

图3:器件阈值电压的阱邻近效应

初始原理图中通常不会出现虚拟器件,但与本文中所述其他结构不同的是,一旦版图设计完成了,就必须将虚拟器件反标注进原理图中。虚拟器件是完整但无功能的晶体管,要用LVS工具检测,因此必须加以解释。

电路工程师不能仅依靠原理图仿真来验证其电路。版图提取和完整寄生仿真对验证任何模拟电路来说必不可少。但是,从原理图创建高质量版图,远非是个简单的过程。本文简要介绍了典型模拟模块版图当中需要包含但却不属于原理图的“其他”内容。所有这些结构在电路的制造、工作和性能中都起着至关重要的作用。

我会在下次更详细地讨论如何在CMOS版图中实现这些结构,以及版图设计人员在将它们纳入版图设计时所必须考虑的一些折中。

(原文标题:Analog layout - not just transistors。由Franklin Zhao编译。)

本文为《电子技术设计》2021年12月刊杂志文章,版权所有,禁止转载。免费杂志订阅申请点击这里。

最前沿的电子设计资讯

最前沿的电子设计资讯