大多数电子时钟,无论是模拟的还是数字的,都使用基于32.768kHz晶体的晶振(XO)作为参考。事实上,它与许多微控制器系统通常所用作实时时钟的晶体相同。这些晶体的典型年稳定性为±3ppm[1]。

虽然这对于大多数应用来说已经足够了,但对于从事需要更高稳定性的应用的设计人员来说,这就太不精确了。这些所谓的“time nuts”(时间狂热者)[2]必须依赖高精度的时间源,例如恒温晶振(OCXO)[3],其年稳定性为±2×10-8;或铯标准[4],其典型稳定性更高,为±3×10-12。

不幸的是,将现有应用从基本的晶体时钟升级到高稳定性的频率参考,并不是一项简单的任务。这是因为这些高精度源是在10MHz的标准频率下工作,也即不是标准晶振的32.768kHz工作频率的整数因子。

一种解决方案是使用时钟发生器IC,例如SI5351。它由一个锁相环所组成,这个锁相环可将输入频率倍增至600至900MHz,然后将其分频,生成输出频率。这种解决方案过于复杂,并且可能会受到不期望的相位噪声影响而降低源的性能。本文所提出的替代解决方案则基于分数除法。

由晶振驱动的电子时钟可使用15个连续的2分频计数器将其32.768kHz参考频率分频为1Hz:215=32768。假设一秒内有32,768个脉冲,由于分频器链会对任何不规则的脉冲位置或占空比进行平滑,因此这些脉冲何时以及如何发生并不重要。

如果有一个有限状态机,它可以对10MHz时钟输入进行门控以仅让前32,768个脉冲通过,那么就可以实现此目的。然而,这将得到一个非常不规则的时钟,它由32,768个脉冲组成,频率为10MHz,然后有几乎997ms的间隙。对于期望获得一致的32.768kHz时钟的系统来说,这可能就太不规则了。

取而代之,可以使用分数除法来识别10MHz和32.768kHz的公因数,如以下等式所示:

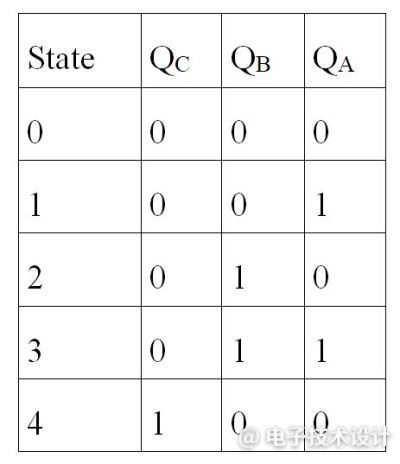

上面的等式说明,所需的除法可以通过六次2.5分频运算和一次1.25分频运算实现。可以使用标准的5分频逻辑元件,例如74HC390双十进制计数器中所提供的那个,生成2.5分频函数。74HC390由两个独立的2分频计数器和两个5分频计数器组成。5分频的真值表如图1所示,其中QC是最高有效位(MSB),QA是最低有效位(LSB)。

图1:5分频计数器的真值表。

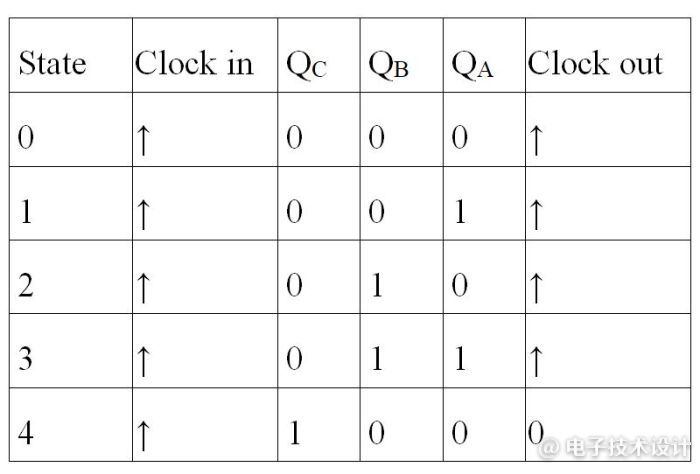

对于每五个输入时钟脉冲,QA产生两次脉冲,因此它执行不规则的2.5分频。如果恰好需要50%的占空比,则可以使用更先进的架构[5]。1.25分频则更复杂,但由于它相当于每五个输入脉冲产生四个输出脉冲,因此也可以使用简单的有限状态机来实现。这可以通过将输入时钟与五分频元件的QC非输出进行与运算来实现。因此其真值表如图2所示,其中↑是上升时钟。

图2:源自5分频函数的1.25分频计数器的真值表。

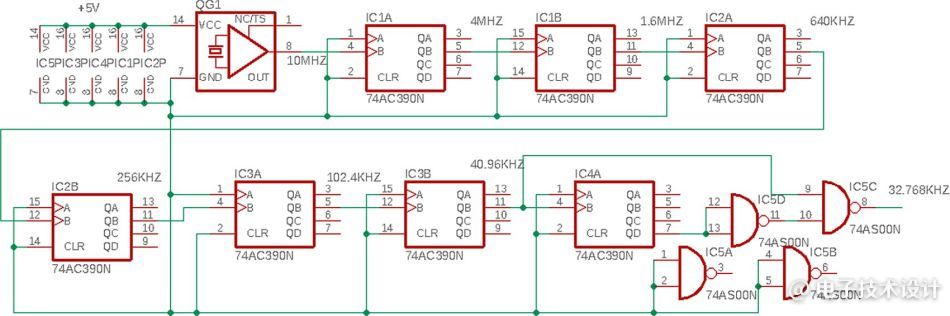

完整的分频器原理图如图3所示。QG1是一个10MHz晶振模块,如果需要的话,它可以是一个高稳定性的OCXO。它为第一个2.5分频IC1A提供了一个TTL兼容时钟。输入A是74HC390的2分频的时钟输入。在本例中,A未使用,因此将它连接到低电平,而其相应的输出QA则悬空。输入B则和输出QB、QC和QD形成5分频,其中QB是LSB输出。

图3:分频器链的原理图。

IC1A的QB将产生4MHz时钟,然后由IC1B进一步分频为1.6MHz。IC2和IC3使用2.5分频级将其进一步分频至40.96kHz。来自74HC00四路双输入与非门的IC5D对IC4A的QD输出进行反转。然后将它馈送到与非门,并在此将它与输入时钟进行“与”运算以形成1.25分频,从而在其输出(引脚8)处产生32.768kHz时钟。

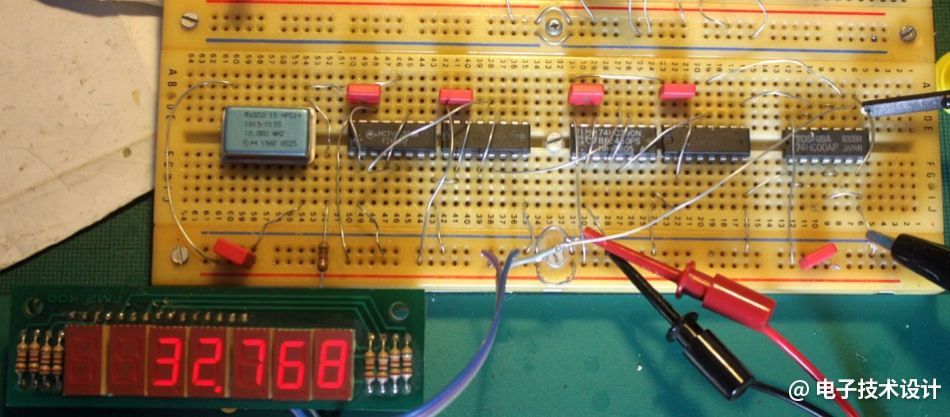

为了验证该理论,将该电路在面包板上制作了原型,如图4所示。

图4:用面包板实现带频率计数器的分频器链。

10MHz参考(QG1)是左侧的金属封装振荡器模块。四个74HC390在它的旁边,而74HC00则位于原型板的最右侧。原型板下方所示的显示器是基于ICM7216D的频率计数器,用于显示电路的输出频率。

图4中的频率计数器配置有1s的门控时间,在此期间对不规则的脉冲序列进行平滑。它使用与分频器链相同的10MHz晶体振荡器作为参考。正如预期的那样,如显示器所示,该平均输出频率是设计所指定的32.768kHz。

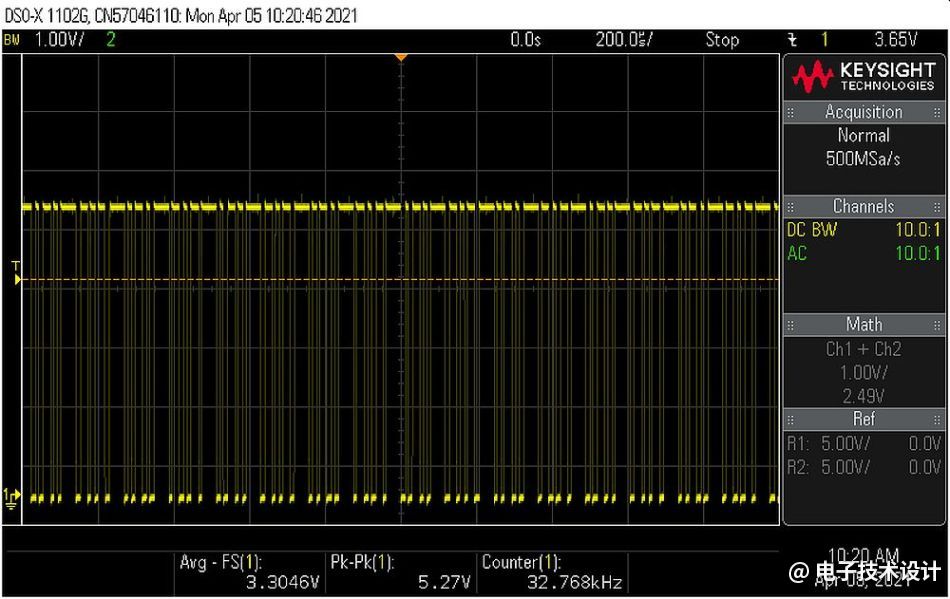

分频器电路的输出脉冲序列也使用Keysight DSO-X 1102G示波器进行了记录,如图5所示。其平均频率是用内部计数器测量的,显示为32.768kHz。另请注意,脉冲串的不规则性质在示波器显示屏上清晰可见。

图5:在输出端测得的脉冲序列。

这些确定的结果说明了可如何巧妙地从10MHz得到32.768kHz。

[1] Golledge GWX-1610 1610 Package 32.768kHz Watch Crystal.

[2] A Time Nuts website: http://www.leapsecond.com/

[3] Golledge HCD220 10 MHz OCXO.

[4] Lindon L. Lewis, “An Introduction to Frequency Standards”.

[5] Yongping Xia, “Divide by 2.5”, Electronics World + Wireless World, December 1991, pp. 1051.

Gavin是东芝(英国布里斯托尔)的一名电子工程师和终身硬件黑客。他主要从事射频工程领域的高级功率放大器等方面的工作。在业余时间,他最开心的是在他备用的卧室实验室里摆弄音频电子设备和老式测试设备。

(原文刊登于EDN美国版,参考链接:Drive any electronic clock with a high-precision 10-MHz reference,由Franklin Zhao编译。)

本文为《电子技术设计》2022年1月刊杂志文章,版权所有,禁止转载。免费杂志订阅申请点击这里。

最前沿的电子设计资讯

最前沿的电子设计资讯