也许极低阻值的电阻器(即mΩ级及以下)最常见的应用是电流控制电路,因为其低阻值可降低功率损耗。对于这类应用,大约10%-20%的容差就足够了。但即使在这样的容差下,精确测量非常低的电阻值也相当困难,尤其是在涉及大电流时。

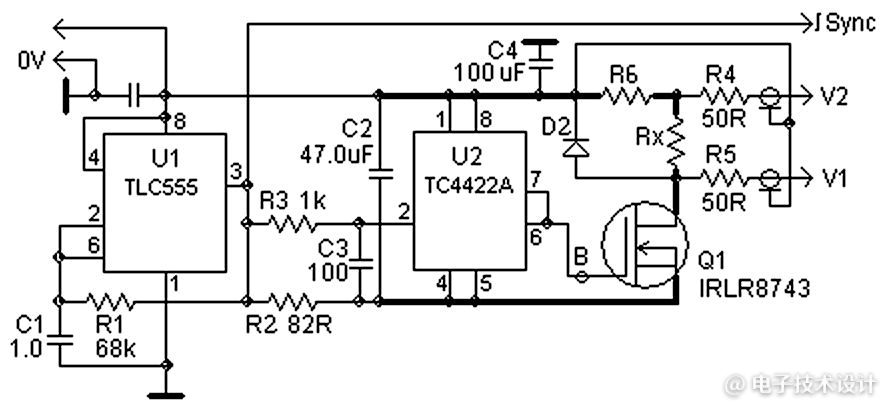

图1所示的电路通过向未知电阻器和已知阻值的参考电阻器施加低占空比脉冲,提供了解决该问题的方法。比率技术用于比较两个元件的响应并确定被测电阻器的值。

图1:以上电路通过向未知电阻器和已知阻值的参考电阻器施加低占空比脉冲,实现了极低电阻值的精确测量。

计算精确电阻值所需的测量值可使用普通示波器或脉冲峰值电压表(可提供更高精度)从输出V1和V2获得。

该电路使用古老的555定时器,在无稳态模式下运行,从而产生用于对低电感电容器C2进行充电和放电的脉冲。在放电周期,电流会通过精密的标准电阻器(R6)和被测电阻(Rx)。电阻值可由相应电压的比值来计算:

V1/V2=(Rx+R6)/R6=Rx/R6+1,

其中,V1和V2是峰值。

因此,未知值为:

Rx=(V1/V2–1)·R6

示波器/电压表的带宽应该足够大,以便捕捉电路产生的短脉冲。由于555振荡器的半周期与脉冲持续时间的比率非常大,一些示波器就无法确保足够的亮度。

该电路还可用于驱动其他需要大振幅、低持续时间电流脉冲的低电阻负载,例如半导体激光器。

同步脉冲(U1,引脚3)有助于示波器的早期同步;由于某些示波器的Y通道中可能没有延迟线,从而无法显示非常陡峭的前沿,因此同步脉冲和输出脉冲之间的延迟可能会使示波器捕捉到脉冲的前沿。该延迟由时间常数R3·C3决定。C3的值可能在20~500pF(甚至更大)的范围内,具体取决于所使用的时基和示波器本身。

MOSFET驱动器U2(TC4422A)用于确保Q1的大栅极充电电流和快速导通时间,这对于准确测量至关重要。

MOSFET(Q1)的RDSOn要非常低(低于3Ω),以便确保干净的大振幅脉冲。快速二极管D2用于限制Q1的过压。注意:这部分电路中所出现的大电流,需要特别注意元器件选择和PCB版图设计。有关详细信息,请参阅下面的元器件选择说明和设计说明两个部分。

该电路短而强大的电流脉冲还会在频域中产生广谱响应。因此,必须特别注意尽量减少寄生电感和电容负载,否则电路将显示高水平的电抗,并在版图的各个部分产生振荡。需要了解的有关如何将这些不期望的寄生效应降至最低的实用细节,在本文的设计说明部分有所记录。

强烈推荐为电路选用SMD元件。一些电容器,即使是基于薄膜的结构,当受到尖锐的大电流脉冲(类似于C2所暴露的那些脉冲)时,它们的介电层也会经历压电运动。有时甚至可以从此类电容器中听到非常明显的“滴答声”,这说明压电效应造成了高水平的损耗。在这种情况下,可以将“滴答”声较小的元件视为更好的元件。

本例中将来自TT Electronics的0.005Ω(5mΩ)、1%容差LOB-3精密电阻用作标准电阻(R6)。

由于电路采用比例测量技术,大多数元件的容差不是很关键,但应特别注意它们的稳定性和结构风格。例如,电容器C2的值并不重要,但它应该足够大以提供足够长的电流脉冲,从而让示波器或电压表很容易注意到。

该电容器应使用具有低内阻/低电感的叠层箔膜或陶瓷等构造技术。应该避免使用多种类型的电容器,尤其是陶瓷电容器,如果它们的电容值取决于所施加的电压。如有必要,可通过并联多个电容器产生所需的值。

对于MOSFET,具有极低RDSon的两个很好的例子是TI的CSD16321Q5和IR的IRLx8743。然而,此类器件通常具有相对较低的漏源和栅源击穿电压(CSD16321Q5仅为8V)——这是进行任何修改时都应考虑的潜在弱点。

另一个潜在限制是MOSFET的最大漏极电流。这两个参数都会影响测试电路的测量下限。

为了降低寄生振荡的水平,电阻器R6和电容器C4应具有非常低的电感——元件本身及其所连接的PCB走线。

R6和C4周围的PCB走线必须保持较短并且铺开,从而最大限度地减少寄生电抗——寄生电抗会因电流脉冲的激励而产生局部谐振。如果电路版图设计不符合此要求,那么就很容易超过MOSFET Q1的绝对最大额定电压。例如,对于6nF的容性负载(栅极电容),驱动器TC4422A的输出上升/下降时间可能小于25ns;这种情况加上通过电感的大电流(约100A),就会产生几乎可损坏任何MOSFET的电压。

请参阅原理图,查看以粗体突出显示的走线——这些走线必须要足够宽,从而能承载大电流,并且要尽可能短,从而最小化寄生电感。这对于将栅极连接到驱动器(U2,引脚6到Q1的基极)的走线尤其重要,该走线应保持在小于1英寸的数值。该走线上的铁氧体磁珠(B)有助于抑制不期望的振荡。

出于同样的原因,电阻Rx和R6的连接应尽可能接近相同的长度。它们还应尽可能短,从而最大限度地减少电感和电压降。

电路的所有外部连接都应使用基本的高频实践进行设计。例如,必须使用两端具有良好阻抗匹配的50Ω同轴电缆。

—Peter Demchenko在立陶宛维尔纽斯大学学习数学并从事软件开发工作。

(原文刊登于EDN美国版,参考链接:A simple ratiometric technique for measurement of very low resistances,由Franklin Zhao编译。)

本文为《电子技术设计》2022年1月刊杂志文章,版权所有,禁止转载。免费杂志订阅申请点击这里。

最前沿的电子设计资讯

最前沿的电子设计资讯