正如每个工程师在早期阶段都知道的那样,必须要遵守时钟沿设计。在数字领域,通过将全局和本地频率树的同步、压摆率和上升/下降时间都结合在一起,才能让产品“滴答”工作。利用时钟信号的上升沿和下降沿来增加数据吞吐量的概念——也就是所谓的双倍数据速率(DDR)——彻底改变了数字设计。

现在,DDR已被用于计算机系统的许多接口当中,其中之一与处理器与内存的接口方式有关。每种新的应用都要求突破该接口的极限。例如,人工智能(AI)、机器学习(ML)和数据挖掘等最新的应用,都在不断地对这些接口提出更严苛的要求。

最新版针对高带宽SDRAM的DDR接口DDR5,于2017年开始开发。2020年7月发布的JESD79-5 DDR5 SDRAM标准,比预期要晚,甚至更受人热切期待。

与DDR4相比,DDR5所承诺的主要功能是降低功耗和双倍带宽。这意味着带宽从3.2Gbps 增加到 6.4Gbps,时钟频率也相应地从1.6GHz 增加到3.2GHz。在降低功耗方面,则是通过将电源电压略微降低(0.1V)到1.1V来实现。

与之而来的是电源管理从主板到双列直插式内存模块(DIMM)的转变。DIMM的容量也从16Gb 增加到64Gb,从而也实现了更高容量的内存模块。通道数量的改变也对其进行了补充,每个DIMM从1个通道增加到2个通道,每个当中有40位数据通道,相比之下,DDR4中只有一个72位的数据通道。数据位的总数保持不变,但通过2个通道来传输该数据,会对时钟信号的生成和分配产生影响。这是为了提高信号完整性(SI)。

虽然较低的电源电压能降低功耗,但其也会使噪声容限变小,进而对设计造成影响。然而,DDR5还将电源管理IC(PMIC)从主板移到了模块上。这又一项重大变化,让电源管理、稳压和上电时序在物理上更接近模块上的内存器件。这也应该有助于改善电源完整性(PI),并对PMIC的工作提供更多控制。

很明显,信号完整性已经在标准的开发过程中受到考虑,而将PMIC移转到模块上也应该带来其自身的优势。然而,设计人员仍需要考虑兼顾电源影响(power-aware)的信号完整性的整体影响。传统的工作流程会假设有一个理想的配电网络(PDN),并且可能会忽略耦合信号及电源层和地层对整个PCB的整体信号完整性的影响。如果将电源完整性和信号完整性分开分析的话,则可能会遗漏兼顾电源影响的信号完整性问题。

(在PCB设计中如何兼顾电源完整性和信号完整性的要求?2022年4月21日,在AspenCore主办的“2022国际集成电路展览会暨研讨会(IIC Shanghai 2022)”(4月20-21日,上海国际会议中心)同期举办的“高效电源管理及宽禁带半导体技术应用论坛”上,来自是德科技、捷捷微、R&S、PI、英诺赛科、泰克科技、Future、必易微、EPC等行业知名厂商的专家,将会发表有关“利用电池模拟技术, 提升BMS设计的可靠性, 延长电池寿命”、“综合数据和电源的连接与数字生活的前世,今生、未来”、“实现小巧紧凑、性能先进、效率极高的高集成度反激式电源方案”、“精准测试助力解决SiC、GaN电源的开发测试难题”以及“多串锂电池的高精度监控器和保护器”等热门电源技术的主题演讲,探讨电源设计细节,邀您报名参加!)

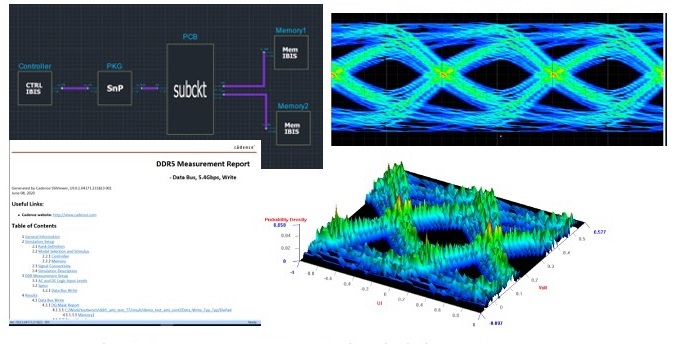

这包括同步开关噪声(SSN),它被比作PCB上的地弹。实际上,SSN具有改变地层电位的效应,或着它本身也可能表现为电源轨上的电压下降;这是由于有多个阱同时开关,所消耗的功率超过PDN所能提供的瞬时功率所引起的。当有多个信号一起开关时,DDR等高速并行总线可能会特别受到SSN的影响(图1)。

图1:利用2D和3D 眼图,将 DDR5的信号质量与JEDEC规范进行比较。(图片来源:Cadence Design Systems)

对SSN的影响进行准确建模并不是件很简单的事情,大多数传统EDA工具利用不同的兼顾电源影响的模型来解决这个问题,例如IBIS 5.0+模型和互连模型。大多数信号完整性分析工具并不能执行SSN分析,因为一旦版图设计完成,就能得到兼顾电源影响的互连模型。这说明设计阶段的噪声分析通常仅限于设计规则和几何规则检查。

在当今所采用的大多数仿真技术中,信号分析和PDN之间存在根本性的脱节。这是一个带有其他缺点的遗留问题,因为底层仿真技术早在DDR5等Gbps速度的并行总线被构思出来之前就已经被开发出来了。

通常SPICE模型的复杂性可能会有所不同,它们会利用时域仿真来产生一个准确的RLC模型,同时有时会假设有一个理想的地。这样得到的时域仿真模型,就是以通过仿真提取的简单频率响应为根据的。这就是以牺牲准确性来换取权宜之计,而对于更高的频率,工程师就会转用可以用混合求解器创建的S参数。SPICE模型和S参数都很有用,尤其是因为S参数不包含任何低频或直流信息。

将有限差分时域法(FDTD)与混合求解器一起使用,就可以将覆盖范围扩展到信号线、电源线和地线。最好是配备可以将多个求解器的输出集成和合并的工具,从而解决电路的版图设计以及传输线和电磁场,这样就可以提供数据与电源层/地层之间随时间变化的相互影响。一个例子是Sigrity SPEED2000 引擎,它利用了FDTD方法来分析IC封装和PCB的版图设计。

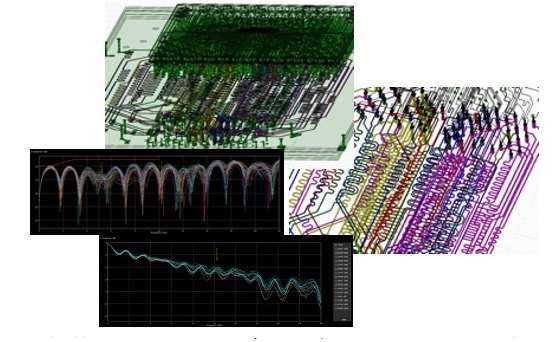

利用FDTD方法可通过使用兼顾电源影响的信号完整性分析,支持多域规则检查和仿真,进而支持快速的设计流程。但是最终的签核仍需转换至3D全波建模方法,这才能提供所需的准确性(图2)。

图2:信号完整性的签核过程需要对跨多个层与多个结构的耦合信号进行准确3D建模。(图片来源:Cadence Design Systems)

这种准确性是以计算能力和仿真时间为代价的。它可以通过分段来解决,但这只能将问题分割成较小的部分,而这些部分仍需要进行处理。

这就是并行化所能提供真正性能优势的地方。通过使用基于有限元分析(FEM)的方法,就可以将工作分解成更小的部分,从而将其分配到大规模的并行架构中,例如数据中心或云服务器。然后将分析结果根据频率响应,重新组合成S参数模型。FEM是由Clarity 3D Solver所提供的,而Sigrity技术则可以分析这种模型。

传统的信号分析通常是在假设PDN是“理想”的情况下运行。这是为了方便和权宜之计而不是准确性。随着我们进入具有6.4Gbps数据速率和3.2GHz系统时钟的DDR5领域,兼顾电源影响的信号完整性的问题就开始变得更加显著了。

如果工程师希望采用DDR5所提供的性能,那么就越来越有必要在系统中的所有关键点——芯片、封装和PCB——应用兼顾电源影响的信号完整性分析。这个分析水平会对底层计算平台提出巨大的要求,更不用说总设计时间了。

对于兼顾电源影响的信号完整性分析,没有哪种单独的方法可以提供完全满足其所需的覆盖范围。建议使用一种整体处理分析的方法,其主要要求是具有一套不同层次的工具,而能最终将信号、电源和地作为完整的电气系统进行分析。

在这一系列的工具中,设计人员就可以对电源层和地层之间的估计噪声耦合运用电气规则检查(ERC)。然而,最终解决方案所包含的兼顾电源影响的信号完整性分析,则必须结合快速准确的场求解器进行互连提取。

(原文刊登于EDN美国版,参考链接:Why power-aware signal integrity analysis matters in DDR5 design,由Franklin Zhao编译。)

本文为《电子技术设计》2022年3月刊杂志文章,版权所有,禁止转载。免费杂志订阅申请点击这里。

2022年4月21日,在AspenCore主办的“2022国际集成电路展览会暨研讨会(IIC Shanghai 2022)”(4月20-21日,上海国际会议中心)同期举办的“高效电源管理及宽禁带半导体技术应用论坛”上,来自是德科技、捷捷微、R&S、PI、英诺赛科、泰克科技、Future、必易微、EPC等行业知名厂商的专家,将会发表有关“利用电池模拟技术, 提升BMS设计的可靠性, 延长电池寿命”、“综合数据和电源的连接与数字生活的前世,今生、未来”、“实现小巧紧凑、性能先进、效率极高的高集成度反激式电源方案”、“精准测试助力解决SiC、GaN电源的开发测试难题”以及“多串锂电池的高精度监控器和保护器”等热门电源技术的主题演讲,探讨电源设计细节,邀您报名参加!

最前沿的电子设计资讯

最前沿的电子设计资讯