公众号:高速先生

作者:黄刚

上篇文章我们介绍了DDR5的一些总体特点,也到了很多网友的关注,文章获得了很多的点击和阅读量。因此高速先生也应广大网友的要求,在本期增加关于DDR5的仿真技术,相信应该是相当大部分网友首次看到的干货了,希望大家能有所收获哈。

高速先生在DDR5规范发布后不久就成功拿到了DDR5颗粒的模型,然后迫不及待的打开来看看模型的一些描述。关于DDR5技术对信号质量的改进来看,在上篇文章也写到了,主要是2个部分的技术改进:一是地址控制信号增加了ODT功能,二是数据信号加入了高速串行模块拥有的DFE均衡的功能。那本篇文章我们就边仿真边给大家介绍这两部分功能带来的信号质量的优化效果哈!

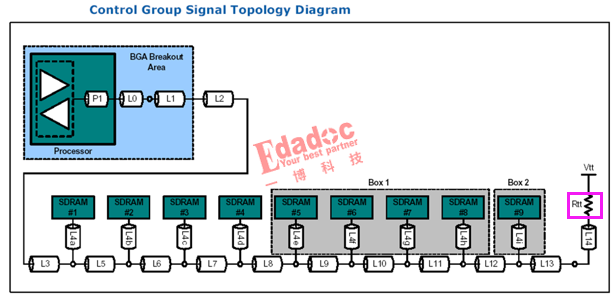

首先我们在本期文章先分享下地址控制信号内置ODT的效果哈。我们知道,在DDR4之前,地址控制信号都需要在PCB板上面外加ODT电阻,才能使信号质量得到保证,就像下图的情况。

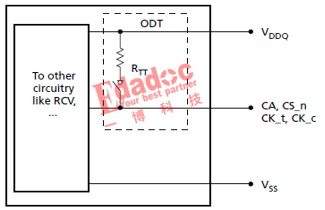

但是在DDR5的时代,这个外加的电阻就不需要了。我们看到DDR5规范上关于布线的图已经更新,变成了内置的ODT电阻,另外还说明的是,地址控制的ODT也是上拉到VDDQ电源的哈。

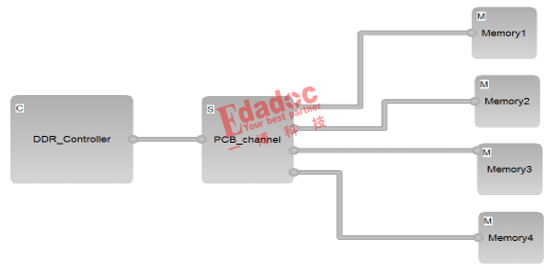

我们以一个一拖4的拓扑进行DDR5地址控制信号的仿真,在仿真软件上的模型如下:

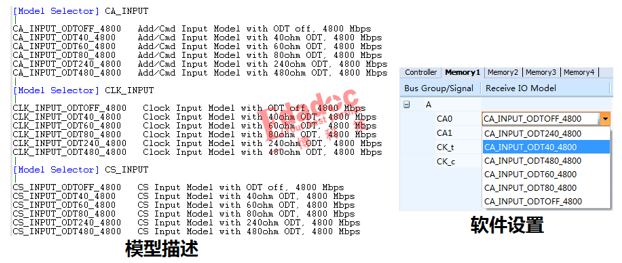

我们先看看颗粒模型上的描述,发现在地址控制信号已经存在了ODT的buffer,就是下面这样!所以我们在仿真软件上肯定也可以去设置它了。

而且还有一点很重要,就像我们这里展示的1拖4的拓扑来说,4个颗粒可以自由选择自己配置还是不配置ODT电阻,也就是说你可以对其中任何一个颗粒进行配置或不配置,拥有比较高的自由度,当然也就会有很多种信号质量的组合出来了。

好,话不多说,我们通过仿真来看看到底内置的ODT效果有多明显哈。仿真速率直接定到3200Mbps,对应数据信号的6400Mbps去,来到了DDR4基本上无法企及的量级了,但是对于DDR5只是个起步价。

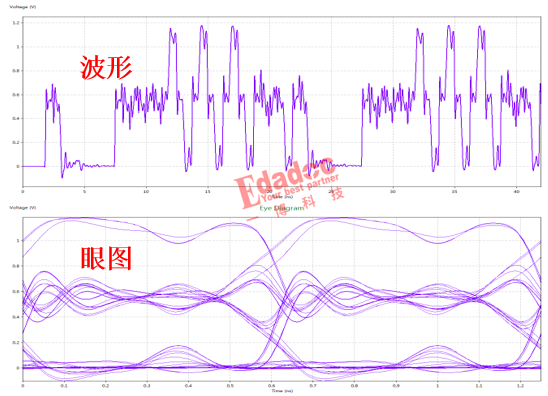

首先我们看看前面在没打开任何ODT情况下,相当于DDR4拓扑不外加端接电阻的情况下的信号质量波形,时间关系我们都只看最差颗粒,也就是第一个颗粒的波形!发现不加ODT情况下基本就是“凉凉”,没有任何眼图张开的机会!

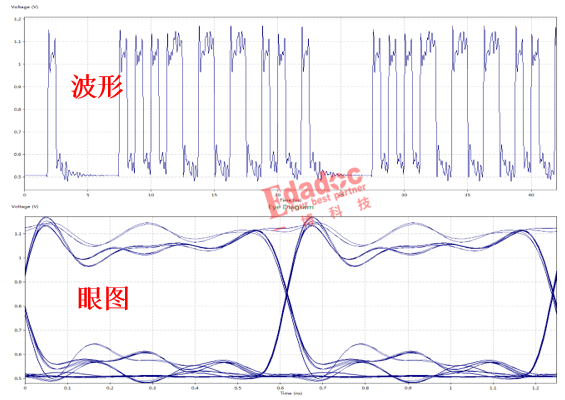

那我们这时候通过对最后一个颗粒进行ODT的配置,给一个40欧姆的ODT设置,我们再来看看信号质量的改善。可以看到效果异常明显,不仅眼图张开了,而且裕量非常的大!

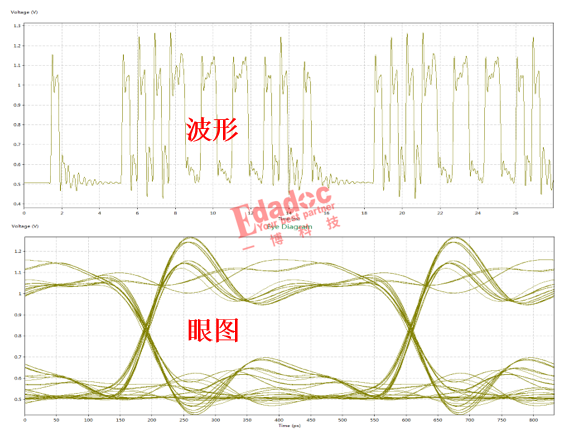

而且据说DDR5还能支持恐怖的到9600Mbps,我们也不妨用该模型仿真下最最极限的速率,看看内部ODT的加入还能不能hold得住它!我们在软件中直接修改速率再次进行仿真,结果如下所示:虽然能看到衰减变得更大了,反射也变得更严重了,但是信号还是有一些裕量,如果设计比较好的话还是有可能实现的哈!

以上就是DDR5地址控制信号对内部ODT的仿真过程了,通过仿真的结果,大家是不是觉得经历过在DDR4的地址控制信号那么难做,心态都快要崩了,现在突然发现还能再抢救一下呢?

最前沿的电子设计资讯

最前沿的电子设计资讯