黄刚 | 文

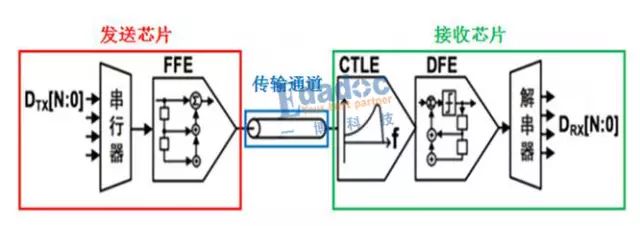

CTLE是什么?上篇文章也提到了,直白的翻译为连续时间线性均衡。它是在接收端芯片上的一种技术。之前也提到了,它的作用可以在传输损耗较大的链路,有效的改善接收端眼图的性能。

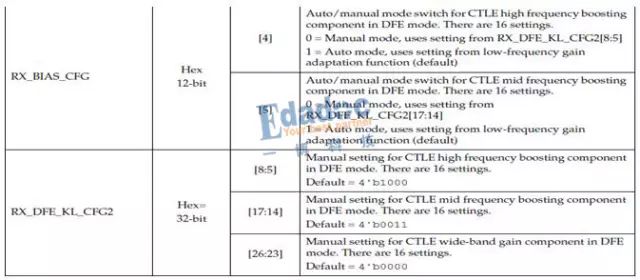

对于有过高速串行信号仿真经验的同行来说,最经常看到它的地方是IBIS-AMI的模型,以XILINX的V7芯片的ibis-ami模型为例,一般有以下对CTLE的描述:

很多初学的同行在对接收端的模型进行参数调节的时候,是不是一看到了“AUTO”的字眼,就马上选上,然后静静的等着之前闭合的接收端眼图慢慢张开,然后就会在结论中给出“接收端模型采用AUTO的自适应均衡即可满足要求”。的确,软件就是软件,做得越自动化越能提高仿真的效率,软件对CTLE的自动算法,的确能在确定通道频域特性的情况下优化出CTLE的响应,使得RX的接收频域特性达到最优,这样的话,时序和频域的波形就会变好了。

但是,如果真的要问CTLE为什么能使原本闭合的眼图张开,或者上述ibis-ami模型关于CTLE的参数是什么意思,这可能会难倒相当一部分人吧。好吧,我们喜欢从结果出发,那就先来看看加入CTLE后的效果吧。

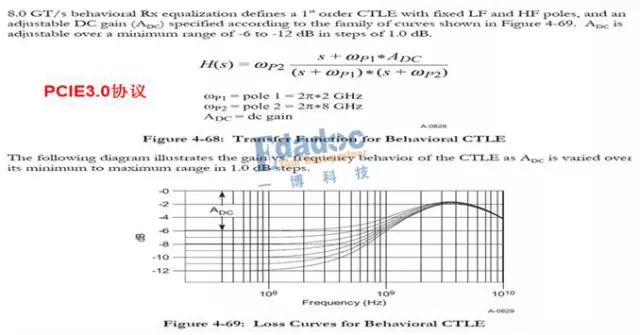

我们选择PCIE3.0协议的CTLE模型进行探讨,该模型的描述如下所示:

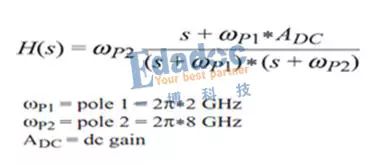

看到它实际上是频率和(幅度)dB值的关系曲线,我们先不管它的作用,先通过数学对下面的公式分析下:

首先我们知道,当s=0时,H(0)=ADC,也就是当频率为0的时候也就是直流的时候,实际上幅度是一个负的增益(常数),当频率在一个比较高(趋向无穷大)时,H为趋向于负无穷大;实际上曲线变化频段的部分是由公式上两个pole点来控制,我们一般称为极点或者peak点。根据该公式的数学运算,在两个pole点之间会出现该曲线的一个最大值。这样我们就通过增益,零点,极点来定义了一个频域响应了。

因此CTLE曲线就是一个在低频时增益衰减为常数,然后随着频率升高慢慢衰减变小,但是过了一个较高频率之后,衰减又开始慢慢变大的效果。其实我们想利用的频段是前两部分:在低频时候常数增益衰减,然后随着频率升高慢慢衰减变小的频段。然后我们能下这么一个结论,实际上,在起作用的频段内,CTLE是一个高通滤波器。

那我们来看看它对于通道的作用吧。

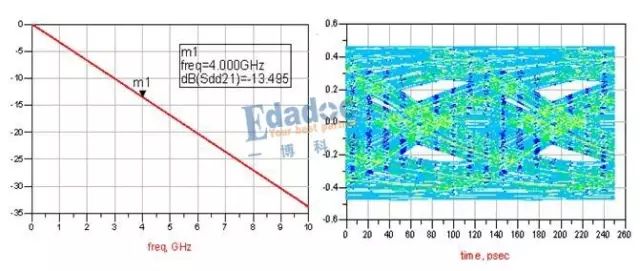

当PCIE3.0的传输通道达到如下损耗时,接收端眼图已经全部闭合。

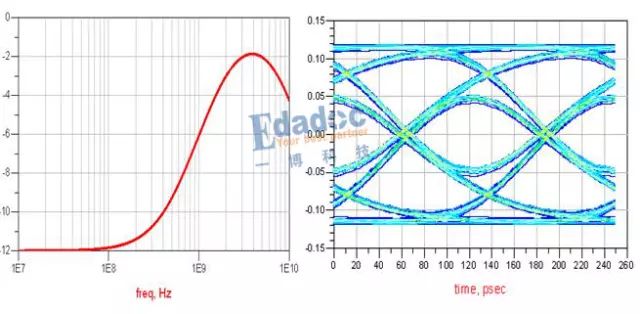

然后我们加入一个-12db-ADC的CTLE均衡,眼图变成了下面的样子。

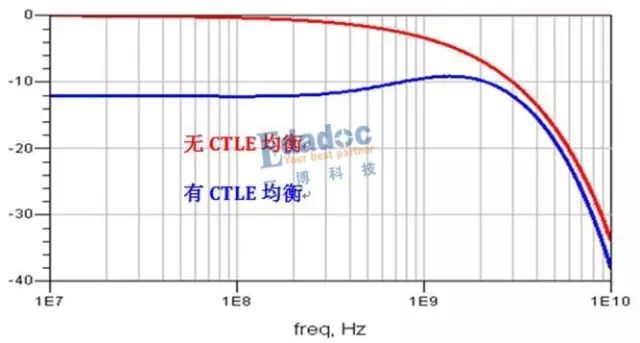

这时我们再去关注RX端的频率响应,加入CTLE前后的RX端损耗对比如下:

想不到有均衡之后的接收端损耗曲线竟然全频段都在无CTLE均衡的下面,说明均衡后的损耗总体都比无均衡的要差。

最前沿的电子设计资讯

最前沿的电子设计资讯