2021 HotChips会议上,台积电发布了最新的3D封装技术路线图,其中涉及到硅光相关的新型异质集成封装(heterogeneous integration)技术,台积称之为COUPE。小豆芽这里做一个简单的介绍。

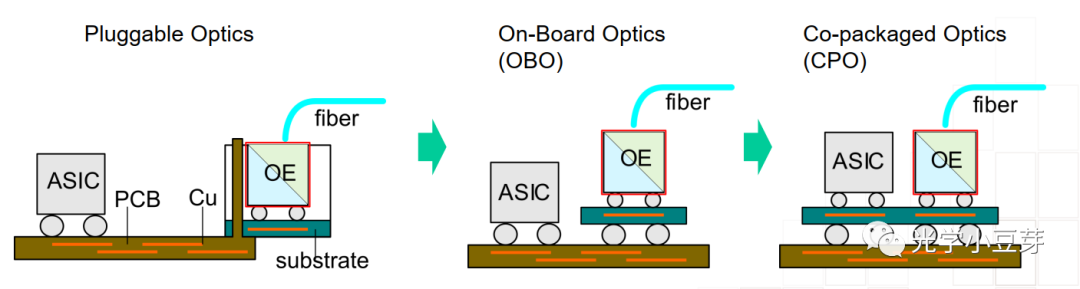

文献1中首先回顾了硅光封装形式的演变,从pluggable optics到on-board optics, 再到最近非常火热的co-packaged optics, 如下图所示,

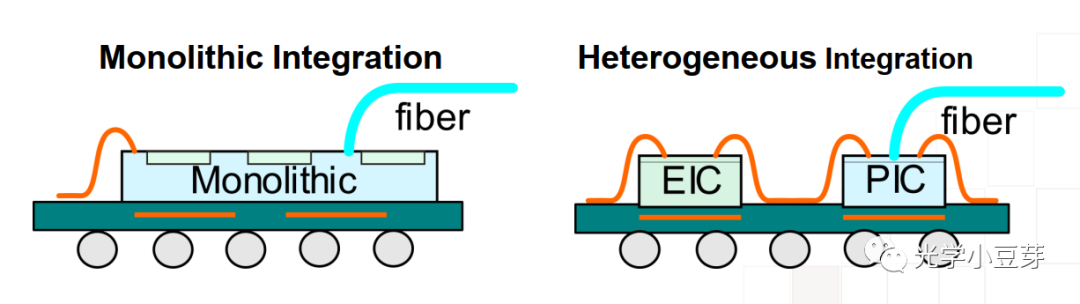

为了达到更大的带宽和更高的能效比,业界有一部分企业在推进EIC-PIC单片集成(monolithic integration)的路线(参看GlobalFoundry的300mm硅光子工艺平台), 如下图左图所示,在同一个芯片上同时加工电器件与光器件。但是TSMC认为,因为无法协调EIC与PIC的工艺节点,导致两个芯片的性能都无法达到最优,他们提出了异质集成的方案,将EIC与PIC放置在同一个基板上,信号通过wire bonding的方式在substrate上互联,如下图右图所示。

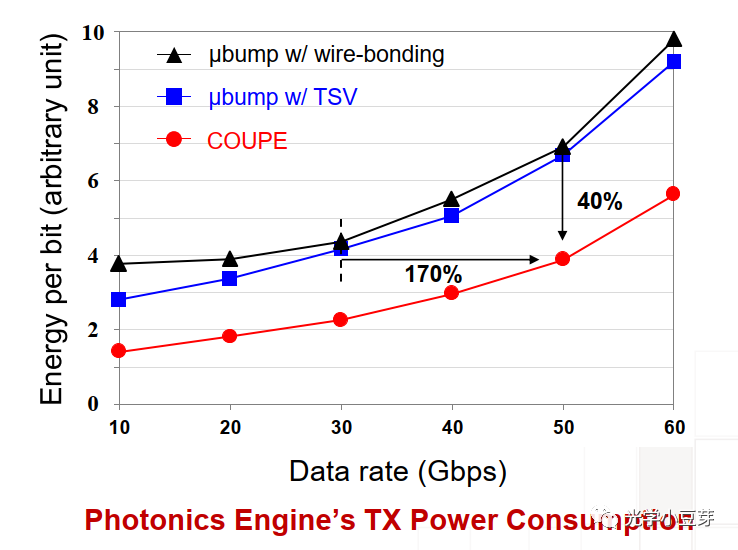

小豆芽这里有些困惑,一般来说,wire bonding的长度较长,传输的信号速率是有限制的,但是台积这里仍然采用的wire bonding方式,并且性能比micro-bump+TSV的方案还要好,如下图所示。COUPE方案的能耗降低了40%, 信号速率提高了70%。

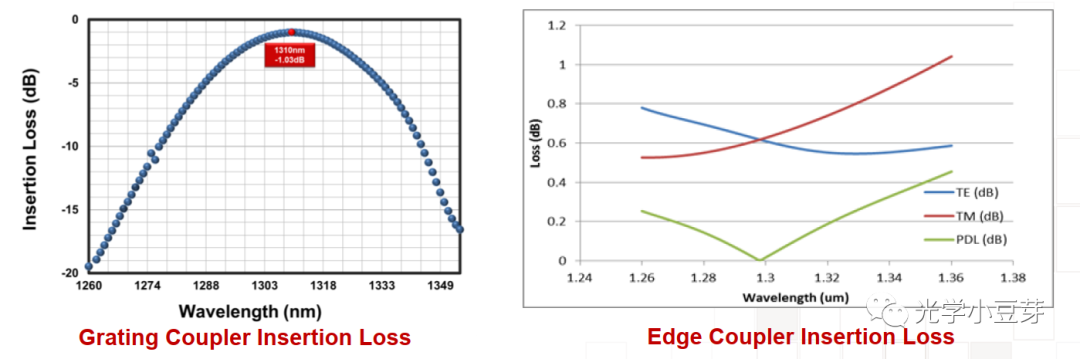

此外,台积还报道了其硅光两种耦合器的性能,光栅耦合器的耦合损耗为-1.03dB, 采用的一维切趾型光栅(apodized GC)。端面耦合的耦合损耗为-0.6dB,采用的是undercut型SSC, 两种耦合器的性能都达到了业界领先水平。测量结果如下图所示。台积没有报道其他的硅光器件参数,但是其与Luxtera长期合作,Luxtera之前报道过相关参数,器件性能也是非常优异的。

简单整理一下,TSMC揭开了其硅光封装的神秘面纱,采用了异质集成的硅光封装路线,电芯片和光芯片放置在同一个基板上,通过wire bonding的方式互联,能效比与带宽得到了提高。台积的硅光耦合损耗已经达到业界领先水平,耦合损耗在1dB左右。对于wire bonding的信号互联方式,小豆芽还有点存疑,欢迎大家留言讨论。看起来台积的野心很大,从EIC和PIC的芯片加工,再到后端的封装,它提供了整套的解决方案,想吃下整块蛋糕。

参考文献:

1. D. Yu, et.al., "TSMC Packaging Technologies for Chiplets and 3D", 2021 HotChips

最前沿的电子设计资讯

最前沿的电子设计资讯