去年OFC 2020, GlobalFoundries报道了其45nm工艺节点的硅光平台45CLO。今年OFC, GF又带来了很多新的进展,小豆芽这里简单整理一下。

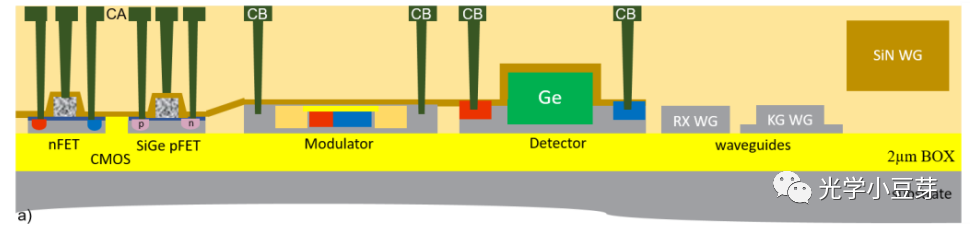

GlobalFoundries的45nm硅光单片集成(monolithically integrated)平台,其截面如下图所示。晶圆的尺寸为300mm(12 inch), 硅的厚度为160nm,Box层厚度为2um,调制器区域的硅减薄为50nm。为了优化电器件的性能,硅的厚度在CMOS区域减薄为88nm。此外,在硅上方还可以有一层300nm厚的SiN。

(图片来自文献1)

1. SiN相关无源器件

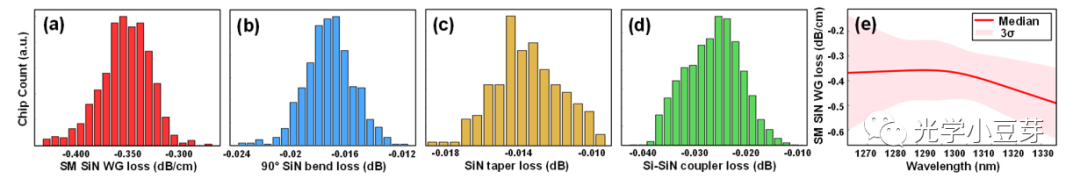

SiN层的厚度为300nm, 通过工艺的优化,目前单模SiN波导的损耗为0.35dB/cm, 90度弯曲波导的损耗为0.017dB, taper的损耗为0.014dB,Si-SiN转换器的损耗为0.026dB,测量结果如下图所示,

(图片来自文献2)

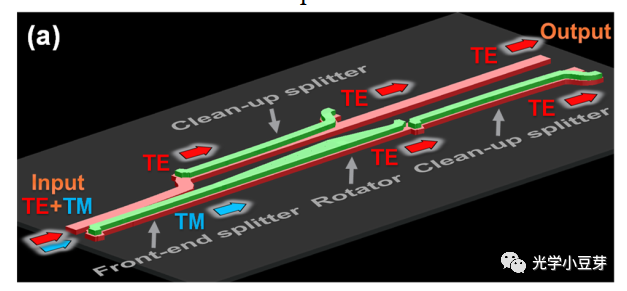

GF实现了较低损耗的偏振旋转分束器(PSR), TE和TM的插损分别为0.3和0.5dB,串扰小于-30dB。其结构如下图所示,PSR分为三部分,先是将TE和TM模式分离到两个波导中,进而对TM模式进行旋转,转化为TE模式,最后再经过一个分束器,进一步过滤TM模式。

(图片来自文献2)

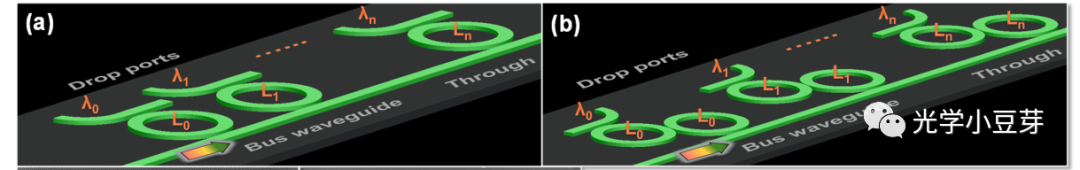

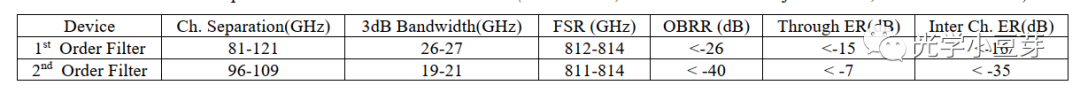

此外GF还尝试了SiN的微环滤波器,设计的通道间隔为100GHz, 3dB带宽为25GHz。微环的结构和测试结果如下图所示,

GF目前还没有在SiN ring中引入热调,由于器件的加工误差,测试结果与设计值有一定的偏差。

2. III-V激光器的混合集成

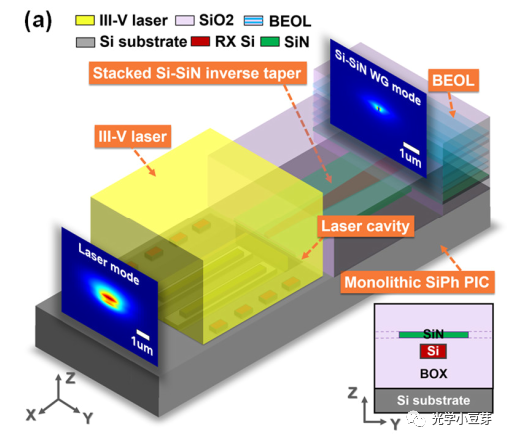

采用与V-groove类似的加工工艺,在硅光芯片上首先刻蚀出一个坑(laser cavity),在坑里加工出所需的金属线与焊料,再将激光器的die芯片倒装(flip-chip)到这个坑里,激光器产生的光通过taper耦入到硅波导中,如下图所示,

(图片来自文献3)

这个混合集成方案看起来非常简单,难点还在于工艺。GF此前在edge coupler的开发中积累了相关的passive对准工艺以及V-groove刻蚀工艺。通过该混合集成方案,在100mA驱动电流的情况下,有11dBm的光功率输入到硅波导中。

GF还提出了利用SiN波导作为taper的集成方案,如下图所示,可进一步降低插损。

(图片来自文献3)

3. MOSCAP型微环调制器

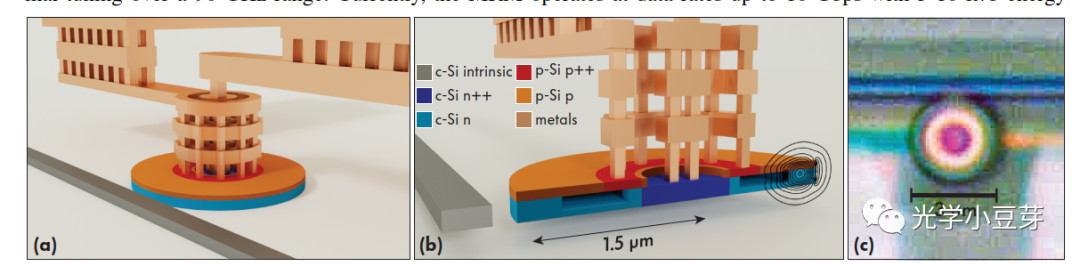

波士顿大学Milos研究组在GF 45CLO工艺平台上,开发出世界上最小的微环调制器。微环的半径为1.5um, 使用基于多晶硅层的MOSCAP型结构,调制效率为30GHz/V(文中没有给出poly Si的厚度)。器件结构如下图所示,

(图片来自文献4)

该调制器在1.5V偏压时的3dB带宽为2GHz, 可实现5Gbps速率的信号传输,如下图所示。功耗为10pJ/bit。

(图片来自文献4)

GlobalFoundries在硅光领域积累丰富,选择的是单片集成路线,提供了45nm工艺节点的光电混合集成平台。此外,GF还独立开发了全自动晶圆级硅光测试平台。GF是为数不多的对硅光工艺比较重视的fab, 当然这也与其宣布放弃7nm先进工艺的研发有关。目前有许多硅光创业公司选择在GF流片,包括Ayar Labs, Acacia(已被Cisco收购), Lightmatter, PsiQuantum等。可以看出GF的硅光平台,得到了产业界的广泛认可。

参考文献:

M. Rakowski, et.al., "45nm CMOS - Silicon Photonics Monolithic Technology (45CLO) for next-generation, low power and high speed optical interconnects", OFC 2020

Y. Bian, et.al., "Monolithically integrated silicon nitride platform", OFC 2021.

Y. Bian, et.al., "Hybrid III-V laser integration on a monolithic silicon photonic platform", OFC 2021.

H. Gevorgyan, et.al., "MOSCAP Ring Modulator with 1.5 µm Radius, 8.5 THz FSR and 30 GHz/V Shift Efficiency in a 45 nm SOI CMOS Process", OFC 2021.

最前沿的电子设计资讯

最前沿的电子设计资讯