OFC 2021有一个关于CPO(co-packaged optics)的workshop讨论,标题是"Are we on the right track to bring co-packaged optics to its prime time?"。关于CPO的基础知识,可以参看这篇笔记共封装光学(co-packaged optics)简介。小豆芽这里整理下OFC 2021相关的最新进展。

1. Intel与Ayar Labs合作实现8Tbps的共封装FPGA

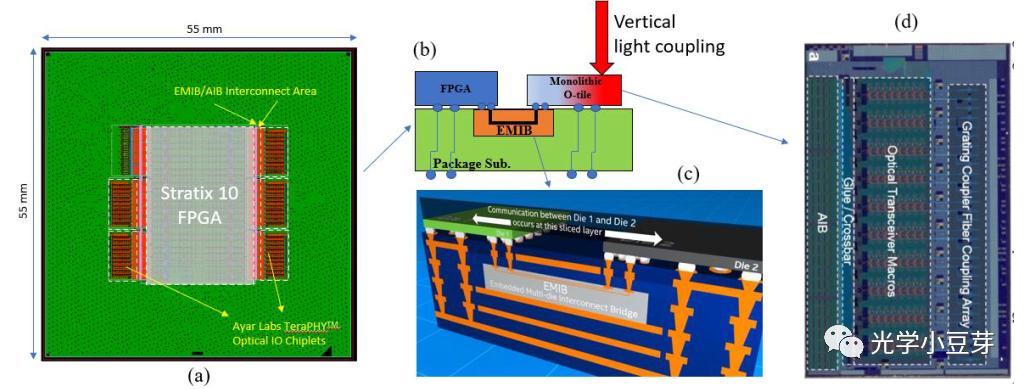

Intel的FPGA芯片Stratix 10通过EMIB技术与Ayer Labs的5颗TeraPHY芯片相连,如下图所示,

(图片来自文献1)

2. II-VI展示了3.2T速率的ROSA

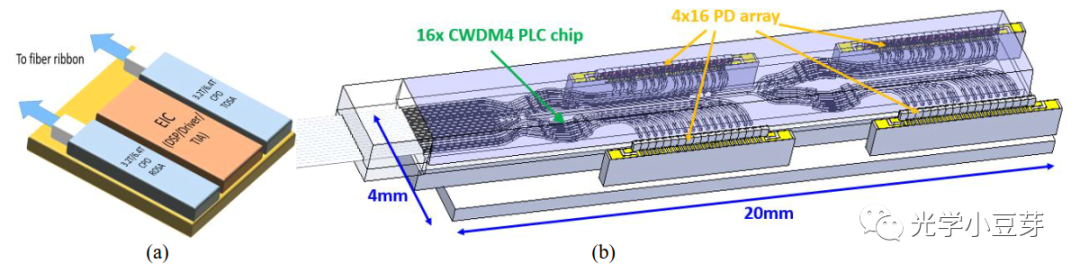

原Finisar上海团队在OFC上报道了其多通道的ROSA进展,可实现3.2T的接收速率。器件结构如下图所示,

(图片来自文献2)

ROSA由一个PLC和4个PD阵列构成,每个PD阵列含有16个InP探测器。PLC中含有16个AWG, 每个AWG实现对四个波长的波分复用,总共有64个波长通道,每个通道的信号速率为50GB/s。整个系统的尺寸为4mm*20mm。

3. 韩国Lipac公司报道了一种基于FOWLP的新型混合光电封装技术

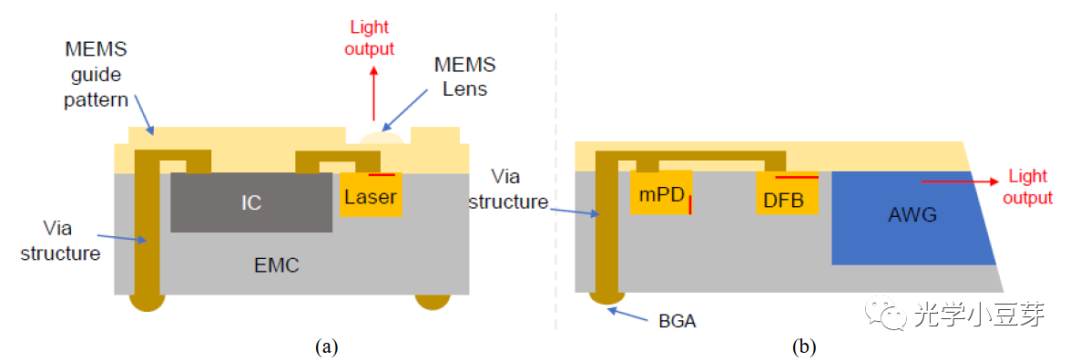

FOWLP的全称是fan-out wafer-level packaging, 不同的die之间通过RDL层互联,避免了使用wire bonding或者bump。TSMC在iPhone 7的A10处理器使用了该技术,获得巨大成功。Lipac公司提出将该项封装技术引入到光电芯片的混合封装中,其原理图如下图所示,

(图片来自文献3)

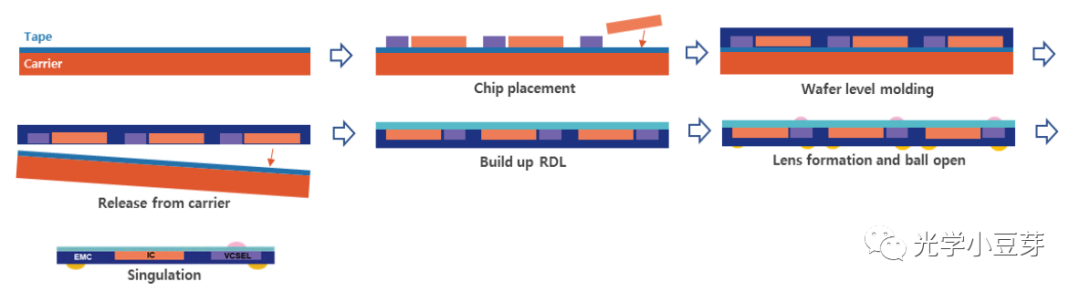

分立的有源光器件(包括激光器、mPD等)与电芯片(TIA, driver等)之间通过RDL连接。封装的工艺流程图如下图所示,

(图片来自文献3)

首先将各个die放置在wafer上,然后覆盖EMC层,接着将handle wafer去除,加工出所需的RDL连接线。根据需求,还可以在芯片表面加工出透镜,便于光信号的耦合。Lipac展示了使用该封装技术的100G SR4光模块。

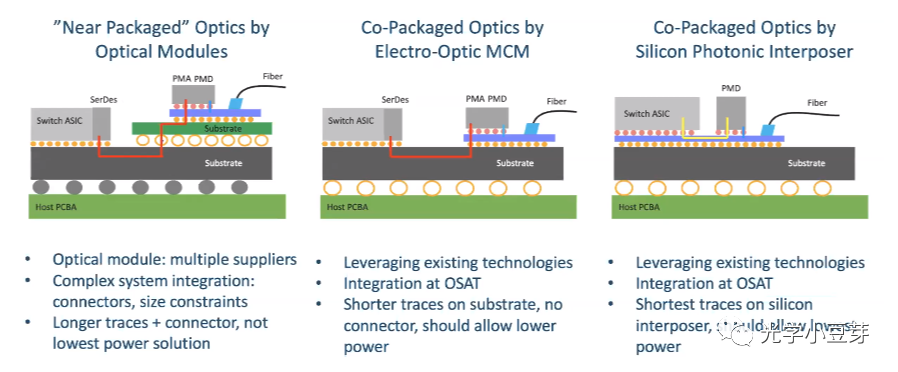

CPO涉及到光电芯片的混合集成,以下是常见的几种封装方案,

其中第三种方案将硅光芯片作为interposer, 电信号通过硅光芯片中的金属层互联。

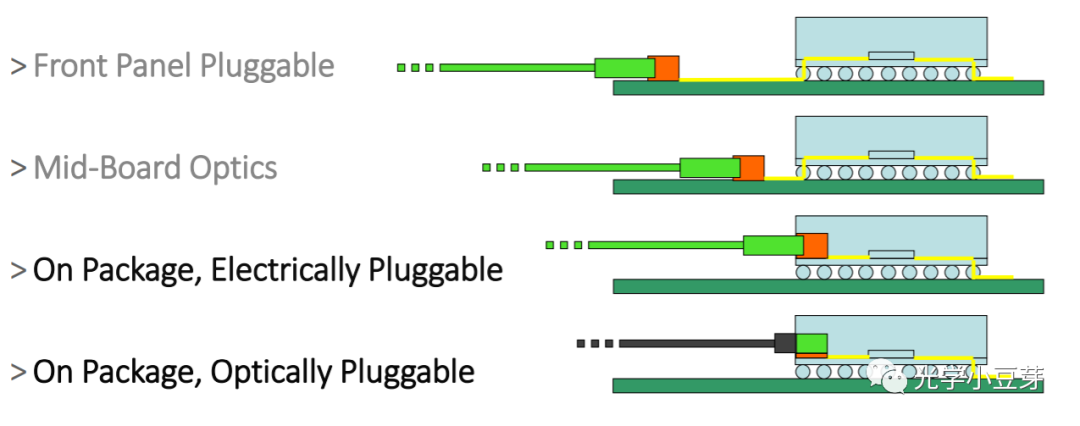

II-VI提出了一个有意思的观点,CPO只是换了一种封装形式的光模块,如下图所示,

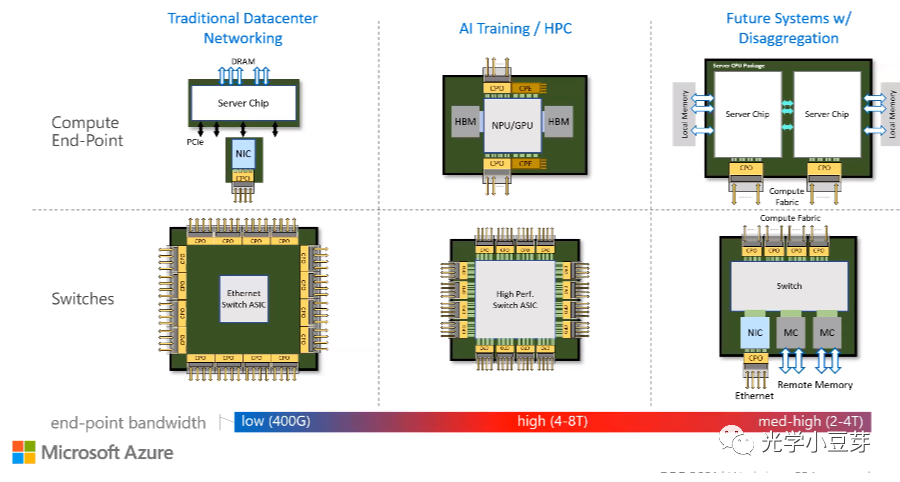

关于CPO的应用场景,现在大部分报道里都是将光引擎围绕着交换机芯片排布,微软的报告里提到了更多的潜在应用场景,如下图所示。CPO也可以应用到AI计算场景中,发挥其功耗低、带宽大的优势,值得期待。Xilinx与Nvida都在做相关的尝试。

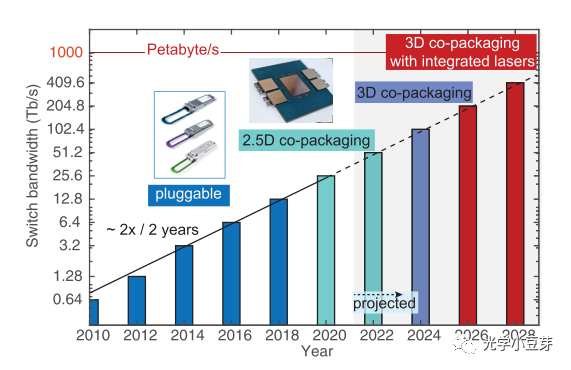

虽然CPO领域非常火热,但是目前对它的质疑声也有不少。主要集中在对系统的可靠性、可生产制造性、是否能提供足够高的带宽、成本是否降低等方面。这些问题不是一朝一夕可以解决的,需要整个行业往前推动。Broadcom、Intel、Cisco等公司都在积极推动CPO技术的落地, Corning公司提出了用于CPO场景的光连接器。但不管如何,如何降低数据传输的功耗与成本是大家的最大痛点,这也是CPO技术得到青睐的主要原因。如下图所示,CPO技术有望在2025年附近真正落地,信号速率达到102Tb/s。

参考文献:

K. Hosseini, et.al., "8 Tbps Co-Packaged FPGA and Silicon Photonics Optical IO", OFC 2021

L. Zhang, et.al., "3.2T/6.4T CWDM ROSA for Co-Packaged Optic

Transceiver", OFC 2021

S. Choi, et.al., "A New FOWLP Platform for Hybrid Optical Packaging Demonstration on 100Gbps Transceiver", OFC 2021

最前沿的电子设计资讯

最前沿的电子设计资讯