这篇笔记介绍下Ayar Labs在OFC 2021上报道的几个最新进展:

1) 1Tbps无差错的光信号互联

2) 多通道多波长的光模块

3) 其与Intel合作,实现了8Tbps的共封装FPGA

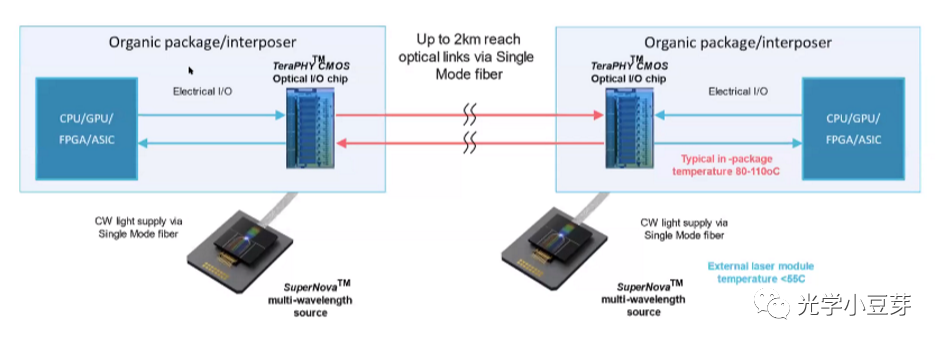

关于Ayar Labs公司的介绍以及技术路线细节,可以参看这篇笔记Ayar Labs公司的硅光子互联技术。其核心技术是借助于硅光芯片,使用光信号取代铜线实现chiplet间的信号互联(也称为optical I/O),其架构图如下图所示,

最终,硅光芯片与CPU/GPU/FPGA等计算芯片封装在一起,通过光纤与其他芯片互联(上图中的红线)。

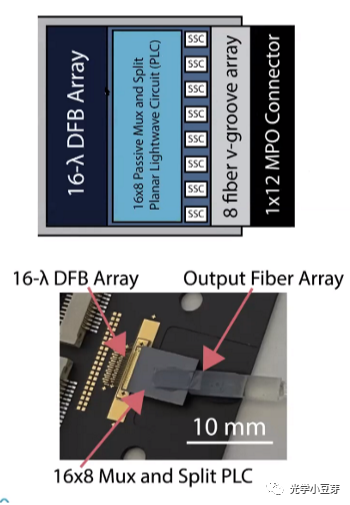

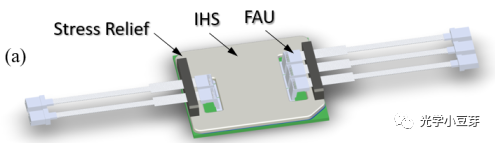

Ayar Labs采用的光源模块称为SuperNova, 其结构如下图所示,

SuperNova采用商用的DFB激光器阵列(与Macom合作),输出8个波长(图中标记的是16个波长,但后续实验中采用的是8波长),通道间隔为400GHz。DFB阵列与PLC构成的Mux与分路器相连,首先通过MUX将多波长合束到单一通道中,接着再通过splitter将光信号分发到多个端口。PLC通过V-groove与光纤阵列相连。最终封装好的SuperNova如下图所示,带着一个小尾巴,

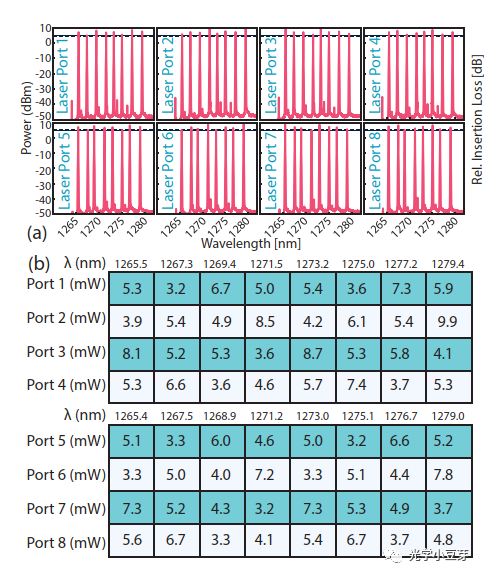

SuperNova共有8个输出端口,每个端口含8个波长,共有64组波长通道,下图是每个通道的功率数据,平均光功率为5.3mW, 不同通道的偏差有2mW左右。

(图片来自文献1)

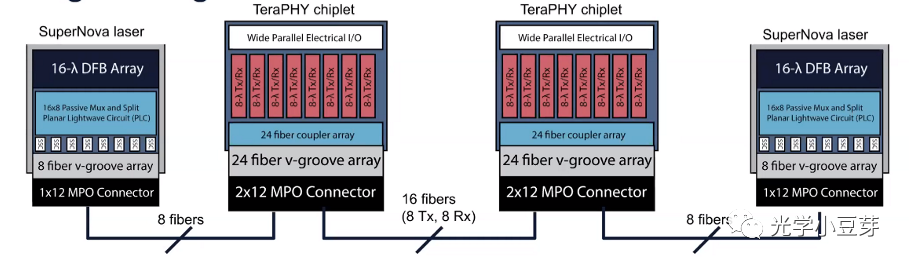

将SuperNova与其光电芯片TeraPHY相连,典型的链路如下图所示,

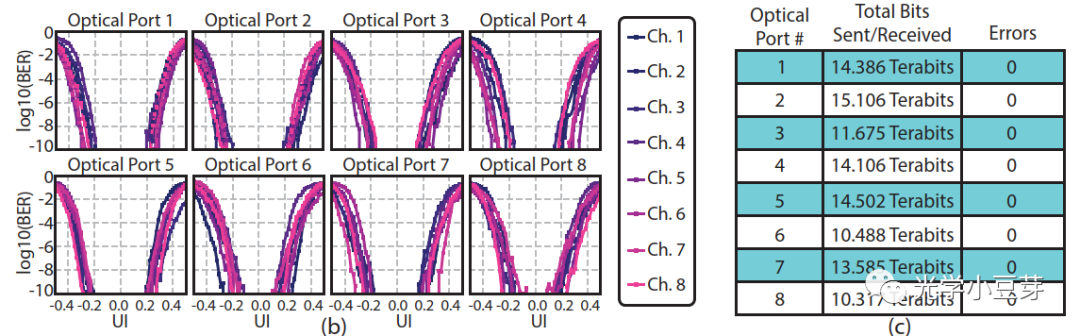

TeraPHY中包含8个Tx/Rx,每个通道的信号速率可以达到25Gbps,因此总的信号速率为25*64=1.6Tbps。Tx端主要为微环调制器,Rx端主要是微环滤波器。其测试结果如下图所示,

(图片来自文献1)

25Gbps时Rx端的眼图有些差,在芯片内集成了Equalization模块。芯片的功耗为5pJ/bit (不包含激光器),主要功耗来源于Rx和时钟。

8个端口的误码率测试结果如下图所示,误码率为0。

(图片来自文献1)

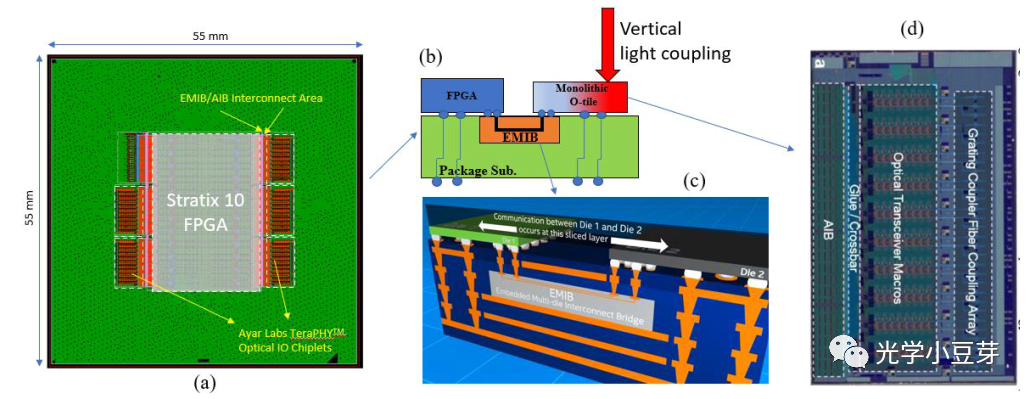

此外Intel与Ayar Labs合作,实现了8Tbps的共封装FPGA,将optical I/O的实用化进程向前推进了一步。整个芯片的结构如下图所示,

(图片来自文献2)

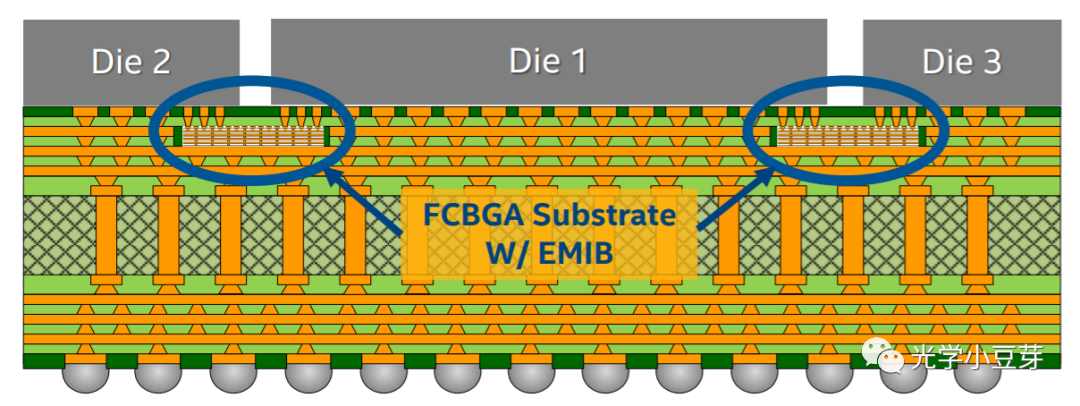

Intel的FPGA芯片Stratix 10通过EMIB技术与5颗TeraPHY芯片相连。EMIB技术全称为Embedded Multi-die Interconnect Bridge, 是Intel开发的一项2.5D封装技术,如下图所示。EMIB为Substrate最顶层两层金属,局部bump的pitch只有几十微米。两颗die通过EMIB互联。

(图片来自https://www.intel.com/content/dam/www/public/us/en/documents/pdf/foundry/sunit-rikhi-2014-idf-presentation.pdf)

Intel并没有展示过多的实验结果,侧重于讨论多颗芯片的共封装问题,其结构示意图如下图所示,

(图片来自文献2)

利用光来实现芯片间的高速信号互联,除了功耗的优势之外,还有波长这个光学独有的资源。通过使用多个波长通道,可以实现更大通量的信号传输。这也是Ayar Labs研发SuperNova的原因。他们也在积极推动CW-WDM这一MSA标准。Ayar Labs通过与Intel等合作,正在稳步地推进Optical I/O这一技术路线,将光互联推进到芯片间这一尺度,期待这一领域更多的进展。

参考文献:

1. M. Wade, et.al., "An Error-free 1 Tbps WDM Optical I/O Chiplet and

Multi-wavelength Multi-port Laser", OFC 2021

2. K. Hosseini, et.al., "8 Tbps Co-Packaged FPGA and Silicon Photonics

Optical IO", OFC 2021

最前沿的电子设计资讯

最前沿的电子设计资讯